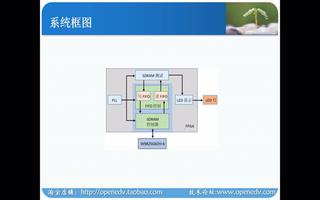

介紹了一種應(yīng)用于通用微處理器系統(tǒng)中的SDRAM與雙口RAM之間的數(shù)據(jù)轉(zhuǎn)移接口控制電路,由VHDL語(yǔ)言設(shè)計(jì),用Xilinx公司4000系列FPGA實(shí)現(xiàn),目前該電路硬件實(shí)現(xiàn)和微處理器系統(tǒng)已經(jīng)通過(guò)驗(yàn)證,證

2011-11-11 09:43:14 1415

1415

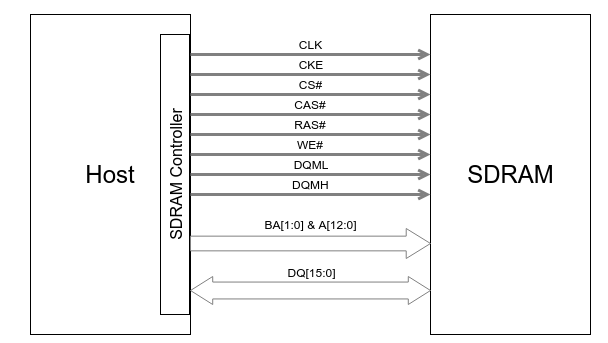

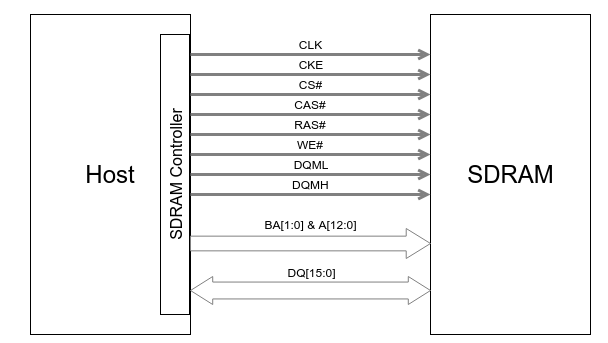

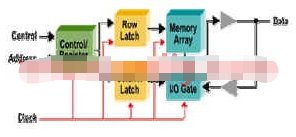

本文則以 SDR SDRAM 為例,描述 DRAM Device 與 Host 端的接口,以及其內(nèi)部的其他模塊,包括 Control Logic、IO、Row & Column Decoder 等。

2020-09-22 15:34:59 4192

4192

誰(shuí)有SDRAM的基于modelism的讀寫(xiě)仿真圖,發(fā)給我一份,急用,在此多謝了,qq:847192168

2014-06-08 08:17:57

~133MHz,單片容量可以達(dá)到64Mbit或更高,因此在需要高速、大容量存儲(chǔ)器的系統(tǒng)中得到廣泛應(yīng)用,如應(yīng)用在目前的計(jì)算機(jī)內(nèi)存中。但是SDRAM的控制比較復(fù)雜,其接口不能直接與目前廣泛應(yīng)用的普通微處理器如

2019-06-10 05:00:08

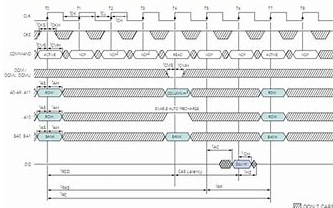

SDRAM的控制原理是什么?SDRAM有哪些控制命令呢?SDRAM的讀寫(xiě)流程有哪些呢?

2021-10-22 08:31:37

SDRAM的基本工作原理是什么SDRAM的基本讀寫(xiě)操作步驟是什么一種簡(jiǎn)單的通用SDRAM控制器的實(shí)現(xiàn)

2021-05-10 06:26:44

“STM32F429等系列的芯片增加了SDRAM接口,擴(kuò)展的內(nèi)存在做人機(jī)界面等應(yīng)用時(shí)是非常有用的。”1.SDRAM硬件接口SDRAM(Synchronous Dynamic R...

2022-01-20 08:28:51

;如果上一次執(zhí)行了寫(xiě)操作,則此次執(zhí)行讀操作。如果不是同時(shí)出現(xiàn)讀寫(xiě)請(qǐng)求,則是什么請(qǐng)求就執(zhí)行什么操作。2)采用全頁(yè)模式的讀寫(xiě)操作,該模式在讀、寫(xiě)完成時(shí),需要給出預(yù)充電命令才能結(jié)束。3)刷新請(qǐng)求始終優(yōu)于讀、寫(xiě)請(qǐng)求。DDR的時(shí)序與SDRAM是相似的,學(xué)好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

請(qǐng)教大家,下圖紅圈處是我用的sdram。請(qǐng)問(wèn)sdram的時(shí)鐘可調(diào)嗎?是不是只要不超過(guò)最大時(shí)鐘頻率就可以呢。我用100MHz的讀寫(xiě)沒(méi)問(wèn)題。用125MHz或150Mhz就出現(xiàn)問(wèn)題了。不知道是需要調(diào)整

2013-06-27 14:25:34

SDRAM的讀寫(xiě)程序怎么寫(xiě)啊。求幫忙解決下,一下附上資料,

2013-07-02 15:58:54

的應(yīng)用也越來(lái)越普遍。E1是我國(guó)電信傳輸網(wǎng)一次群使用的傳輸標(biāo)準(zhǔn),速率是2.048 Mb/s。實(shí)現(xiàn)多路接口與E1協(xié)議的相互轉(zhuǎn)換,將可以把多種設(shè)備同時(shí)連接至高速的E1線路。本文基于FPGA(Field

2019-06-10 05:00:04

摘要:介紹SDRAM的主要控制信號(hào)和基本命令時(shí)序,提出一種應(yīng)用于解復(fù)用的支持多路讀寫(xiě)的SDRAM接口設(shè)計(jì),為需要大容量存儲(chǔ)器的電路設(shè)計(jì)提供了新思路。關(guān)鍵詞:SDRAM 解復(fù)用 接口 存儲(chǔ)器

2018-12-03 15:20:48

該文檔為基于FPGA的多路模擬數(shù)據(jù)采集接口設(shè)計(jì)講解文檔,介紹一種基于 8,RQ 的多路模擬數(shù)據(jù)采集接口的設(shè)計(jì)方案。該方案使用Max1281 作為模數(shù)轉(zhuǎn)換芯片,在 APA150 FPGA 中設(shè)計(jì)和實(shí)現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲(chǔ)模塊;給出了系統(tǒng)設(shè)計(jì)框圖、FPGA開(kāi)發(fā)要點(diǎn)和仿真波形。

2018-09-21 14:37:00

ADI TS201的RS422串口通信 和與SDRAM讀寫(xiě)的程序交流

2018-10-30 09:18:47

本帖最后由 eehome 于 2013-1-5 10:06 編輯

FPGA讀寫(xiě)SDRAM的實(shí)例

2012-08-15 16:38:04

,SDRAM 由于其性能價(jià)格比的優(yōu)勢(shì),而被 DSP 開(kāi)發(fā)者所青睞。DSP 與 SDRAM 直接接口是不可能的。FPGA(現(xiàn)場(chǎng)可編程門陣列)由于其具有使用靈活、執(zhí)行速度快、開(kāi)發(fā)工具豐富的特點(diǎn)而越來(lái)越多地出現(xiàn)在

2020-04-23 08:00:00

STM32H7系列,F(xiàn)MC接片外SDRAM,連續(xù)讀寫(xiě)測(cè)試,每次讀寫(xiě)間加一個(gè)延時(shí)不會(huì)報(bào)錯(cuò),但去掉延時(shí),連續(xù)讀寫(xiě)就讀寫(xiě)不一致了?

請(qǐng)教大神是哪里配置出了問(wèn)題么?

另外還有個(gè)奇怪的現(xiàn)象。。。在循環(huán)的最后

2024-03-11 08:07:46

,TFT彩屏和SDRAM都是板載外設(shè),兩者相比SDRAM更實(shí)用,用途更廣泛,對(duì)板子接口要求更多,因?yàn)楦呒?jí)的開(kāi)發(fā)板才有SDRAM,而TFT彩屏的上述特點(diǎn)都與SDRAM相反,而研究耗費(fèi)的時(shí)間卻更多。 下面

2017-03-05 12:25:51

請(qǐng)問(wèn)各位大蝦 SDRAM是如何進(jìn)行讀寫(xiě)的,如何將文件數(shù)據(jù)存儲(chǔ)到SDRAM中 網(wǎng)上沒(méi)找到這方面的資料 求各位大蝦幫忙

2013-04-14 10:09:13

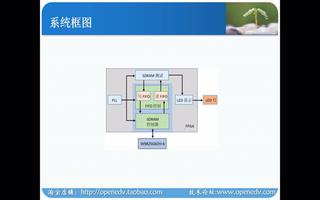

基于FPGA的SDRAM控制器設(shè)計(jì)(三)讀寫(xiě)作者:小周 本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請(qǐng)注明出處! SDRAM控制器設(shè)計(jì)的主要功能是能對(duì)SDRAM進(jìn)行讀寫(xiě)操作,本工程實(shí)現(xiàn)了SDRAM的初始化、自動(dòng)

2020-04-23 11:31:47

互動(dòng),大家可以給公眾號(hào)的后臺(tái)發(fā)送自己對(duì)于讀寫(xiě)FIFO作用的理解。當(dāng)然還是有很多網(wǎng)友給后臺(tái)發(fā)送過(guò)自己的理解,正確率應(yīng)該是60%左右。使用讀/寫(xiě)FIFO的原因:1.寫(xiě)SDRAM, 串口發(fā)送4個(gè)字節(jié)的數(shù)據(jù)所需

2017-05-08 22:38:37

第1節(jié) SDRAM讀寫(xiě)控制器--作者:小黑同學(xué)本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請(qǐng)注明出處!1.1 總體設(shè)計(jì)1.1.1 概述同步動(dòng)態(tài)隨機(jī)存取內(nèi)存(synchronousdynamic

2020-10-15 15:16:02

如題,用的是xilinx的virtex 4的板子。現(xiàn)要向DDR SDRAM讀寫(xiě)數(shù)據(jù),DDR SDRAM的地址該怎么寫(xiě)?

2013-11-05 16:01:53

兩片 MT48LC32M16的SDRAM 操作讀寫(xiě)問(wèn)題 ??? 描述如下:#define SDRAM_BASE_ADDR((uint32_t)0xC0000000)// CS01、按照 32位的讀寫(xiě)

2019-02-19 07:00:08

用Altera_Cpld作了一個(gè)186(主CPU)控制sdram的控制接口, 發(fā)現(xiàn)問(wèn)題:要使得sdram讀寫(xiě)正確, 必須把186(主CPU)的clk送給sdram, 而不能把clk經(jīng)cpld的延時(shí)

2019-09-18 05:02:19

課程介紹1. SDRAM文檔的閱讀和理解2. SDRAM的功能匯總3. SDRAM的實(shí)現(xiàn)架構(gòu)4. SDRAM接口的模塊劃分5. SDRAM的時(shí)序分析和約束練習(xí)3說(shuō)明視頻,轉(zhuǎn)碼問(wèn)題,上傳不了。需要完整

2022-02-15 10:26:33

大蝦們好,最近在使用 stm32f7x單片機(jī)對(duì)sdram 讀寫(xiě) ?? 出現(xiàn)如下情況:圖片1,讀寫(xiě)正常,單個(gè)字節(jié)讀寫(xiě),見(jiàn)圖片描述一寫(xiě)一讀正常,這說(shuō)明硬件木有什么問(wèn)題吧 ??下面的連續(xù)寫(xiě)或者連續(xù)讀都不

2018-11-15 08:55:34

自己做的DSP開(kāi)發(fā)板,在DSP對(duì)SDRAM進(jìn)行寫(xiě)操作的時(shí)候,發(fā)現(xiàn)一個(gè)問(wèn)題:當(dāng)往SDRAM中寫(xiě)的地址數(shù)超過(guò)128個(gè)的時(shí)候,再尋址的時(shí)候第8根地址線會(huì)亂掉,導(dǎo)致地址錯(cuò)位,此時(shí),數(shù)據(jù)線第8根電壓也反向了

2014-04-23 20:14:39

的mcuFIFO中,(sdram讀寫(xiě)頻率為90MHZ),數(shù)據(jù)經(jīng)過(guò)MCUfifo后輸出DATAOUT(8位數(shù)據(jù)),得到的數(shù)據(jù)存在以下問(wèn)題:

2014-09-10 19:49:20

分享一款不錯(cuò)的SDRAM接口的VHDL設(shè)計(jì)

2021-05-08 06:04:27

和刷新,同時(shí)控制FIFO的讀、寫(xiě)操作;FIFO是DSP與SDRAM之間的數(shù)據(jù)通道,深度為256,其作用是充分利用SDRAM的突發(fā)讀寫(xiě)功能,提高系統(tǒng)速度,同時(shí)簡(jiǎn)化DSP軟件設(shè)計(jì)。 3.1 命令接口和刷新

2018-12-07 10:35:02

純邏輯實(shí)現(xiàn)SDARM控制器工程說(shuō)明本項(xiàng)目展示如何用“至簡(jiǎn)設(shè)計(jì)法”設(shè)計(jì)SDARM,具體功能要求如下:1)讀寫(xiě)仲裁機(jī)制:當(dāng)同時(shí)出現(xiàn)讀寫(xiě)請(qǐng)求時(shí),如果上次執(zhí)行了讀操作,則此次執(zhí)行寫(xiě)操作;如果上一次執(zhí)行了寫(xiě)

2017-08-02 17:43:35

上一期介紹了如何使用語(yǔ)音助手控制多路接口,這一期將為大家介紹如何使用官方提供的APP控制多路接口。1、APP的下載地址,以及使用方法可以參考此處,筆者為大家找了一個(gè)講的很詳細(xì)的網(wǎng)頁(yè)。2、關(guān)于

2021-11-03 08:51:50

如何實(shí)現(xiàn)Reg istered SDRAM接口電路的設(shè)計(jì)?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口電路的原理設(shè)計(jì)與布局布線規(guī)則是什么?

2021-04-12 07:10:21

只是讀寫(xiě)檢測(cè),沒(méi)有硬件sdram接口的f103可以測(cè)試嗎

2023-09-21 06:38:25

這樣的,我在跑100MHz讀寫(xiě)sdram的時(shí)候,經(jīng)常出現(xiàn)sdram工作失常的現(xiàn)象。我懷疑是sdram相移引起的。請(qǐng)問(wèn)該如何調(diào)整呢?非常感謝!

2014-01-02 17:08:19

篇有關(guān)SDRAM接口讀寫(xiě)時(shí)序的文章,希望能夠幫助不了解的同學(xué)對(duì)SDRAM數(shù)據(jù)讀寫(xiě)有更進(jìn)一步的認(rèn)識(shí)。 一、SDRAM初始化在SDRAM內(nèi)部有一個(gè)邏輯控制單元,并且有一個(gè)模式寄存器為其提供控制參數(shù)。每次

2020-01-04 19:20:52

實(shí)驗(yàn)中,各端口信號(hào)的管腳分配如下表所示:表 33.3.1 SDRAM讀寫(xiě)測(cè)試實(shí)驗(yàn)管腳分配程序設(shè)計(jì)在本次實(shí)驗(yàn)中,由于SDRAM的控制時(shí)序較為復(fù)雜,為方便用戶調(diào)用,我們將SDRAM控制器封裝成FIFO接口

2020-08-17 15:25:11

我在做一個(gè)FPGA的片外SDRAM讀寫(xiě)功能的開(kāi)發(fā),參考了特權(quán)老師的verilog代碼。背景:片外SDRAM采用的是HY57V561620FT-HI,模塊當(dāng)中利用100K時(shí)鐘產(chǎn)生數(shù)據(jù)流,利用20M時(shí)鐘

2018-04-24 10:38:29

如題.......最近移植特權(quán)的sdram,怎么調(diào)都不通,而且特區(qū)的例子帶了fifo,看起來(lái)異常復(fù)雜也不好仿真,所以求一個(gè)能用的單獨(dú)讀寫(xiě)sdram特定地址的范例,急求謝謝

2015-08-11 08:54:04

的時(shí)鐘雙沿讀寫(xiě)嘛,速度這不就一下翻番了。很對(duì),但是再往深入去,你思考過(guò)嗎?難道DDR內(nèi)部尋址時(shí)數(shù)據(jù)也是雙沿讀寫(xiě)么?非也DDR SDRAM外部的數(shù)據(jù)總線接口位寬,一般是8位或者16位。而它左邊那個(gè)紅圈里

2014-12-30 15:22:49

最近在寫(xiě)ADC采集程序,將ADC采集的數(shù)據(jù)存儲(chǔ)至SDRAM中去。我使用的ADC是20Msps的,所以每個(gè)數(shù)據(jù)是50ns的占留時(shí)間。SDRAM使用的是100MHZ,這個(gè)是SDRAM的操作時(shí)鐘頻率,但是不知道讀寫(xiě)一個(gè)數(shù)據(jù)SDRAM要花多少個(gè)時(shí)鐘呢??應(yīng)該這個(gè)就是SDRAM的讀寫(xiě)速率吧。

2019-04-23 23:38:22

用C5509A讀寫(xiě)外部SDRAM,例程里面souraddr =(int *)0x40000;deminaddr = (int *)0x41000;我把目的地址改為0x50000,發(fā)現(xiàn)從0x40000

2018-07-31 06:23:46

分析了IDE接口硬盤(pán)控制寄存器模型;論述了IDE接口硬盤(pán)的讀寫(xiě)幾項(xiàng)技術(shù);給出了設(shè)計(jì)硬盤(pán)克隆軟件的思想和方法,方法針對(duì)硬盤(pán)物理扇區(qū)進(jìn)行讀寫(xiě),與硬盤(pán)上安裝的具體操作系統(tǒng)

2009-02-22 23:47:29 76

76 針對(duì)SDRAM 控制器讀寫(xiě)數(shù)據(jù)塊訪問(wèn)延時(shí)長(zhǎng)、速度慢的問(wèn)題,提出時(shí)間隱藏技術(shù),將其應(yīng)用于SDRAM 控制器的設(shè)計(jì),采用FPGA實(shí)現(xiàn)。實(shí)驗(yàn)結(jié)果表明,時(shí)間隱藏技術(shù)有效縮短了數(shù)據(jù)塊讀寫(xiě)訪問(wèn)

2009-03-25 09:00:34 15

15 介紹基于現(xiàn)場(chǎng)可編程門陣列(FPGA),利用VHDL 語(yǔ)言設(shè)計(jì)實(shí)現(xiàn)MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結(jié)構(gòu)、SDRAM 存儲(chǔ)接口結(jié)構(gòu)和SDRAM 控制狀態(tài)機(jī)的設(shè)計(jì)。

2009-05-15 14:47:29 24

24 SPI接口讀寫(xiě)串行EEPROM:93C46為采用3線串行同步總線SPI接口方式的EEPROM,其芯片引腳名稱和功能描述如圖1-1:

2009-09-19 11:39:27 89

89 SDRAM設(shè)計(jì)詳細(xì)說(shuō)明

完成SDRAM的上層驅(qū)動(dòng)設(shè)計(jì),對(duì)SDRAM讀寫(xiě)、管理無(wú)誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 基于FPGA的高速SDRAM控制器的視頻應(yīng)用

0 引言 SDRAM(同步動(dòng)態(tài)存儲(chǔ)器)是一種應(yīng)用廣泛的存儲(chǔ)器,具有容量大、數(shù)據(jù)讀寫(xiě)速度快、價(jià)格低廉等優(yōu)點(diǎn),特別適

2009-11-04 09:56:20 847

847 為了降低DSP外部SDRAM存儲(chǔ)系統(tǒng)的功耗,針對(duì)DSP訪問(wèn)片外SDRAM的功耗來(lái)源特點(diǎn),提出了基于總線利用率動(dòng)態(tài)監(jiān)測(cè)的讀寫(xiě)歸并方案。該方案動(dòng)態(tài)監(jiān)測(cè)外部存儲(chǔ)器接口(EMIF)總線的利用率,根據(jù)總線利用率的不同選擇開(kāi)放的頁(yè)策略、封閉的頁(yè)策略或休眠模式;設(shè)計(jì)了簡(jiǎn)化

2011-01-14 17:40:12 50

50 USB接口的彩電存儲(chǔ)器讀寫(xiě)器讀寫(xiě)軟件

2011-03-19 11:00:11 1613

1613 SDRAM 以其高速和大容量的優(yōu)點(diǎn)獲得了極大的應(yīng)用,但是其接口與目前廣泛應(yīng)用的微處理器系統(tǒng)不兼容,介紹了用 VHDL 語(yǔ)言實(shí)現(xiàn)的SDRAM與RAM之間的接口控制電路,從而將SDRAM應(yīng)用到微處理器

2011-06-01 15:29:15 57

57 介紹如何利用EM Microelect ronic 公司的射頻卡讀寫(xiě)基站芯片EM4094 和Arasan 公司的SDIO 接口芯片AC2200 來(lái)構(gòu)建一種基于通用接口SDIO 的即插即用型的RFID 讀寫(xiě)器,它可以在支持SDIO 接口的掌上電腦

2011-06-02 15:29:54 58

58 SDRAM存儲(chǔ)芯片擁有快速讀寫(xiě)的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴(yán)格的控制時(shí)序和工作狀態(tài),可以使用有限狀態(tài)機(jī)理論

2011-10-24 15:08:05 0

0 雖然目前SDRAM內(nèi)存條價(jià)格已經(jīng)接底線,內(nèi)存開(kāi)始向DDR和Rambus內(nèi)存過(guò)渡。但是由于DDR內(nèi)存是在SDRAM基礎(chǔ)上發(fā)展起來(lái)的,所以詳細(xì)了解SDRAM內(nèi)存的接口和主板設(shè)計(jì)方法對(duì)于設(shè)計(jì)基于DDR內(nèi)存的主

2012-01-05 16:21:11 247

247 使用功能強(qiáng)大的FPGA來(lái)實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存儲(chǔ)控制器的用戶接口設(shè)計(jì)與仿真,本設(shè)計(jì)通過(guò)采用多路高速率數(shù)據(jù)讀寫(xiě)操作仿真驗(yàn)證,可知其完全可以滿足時(shí)序要求,由綜合結(jié)果可知其使用邏輯資源很少,運(yùn)行速

2013-01-10 14:12:45 2990

2990 介紹在 Nios II 中利用 SDRAM 控制模塊實(shí)現(xiàn)對(duì) SDRAM 存儲(chǔ)芯片——

K4M561633G 的讀寫(xiě),通過(guò)本章,你能學(xué)到

(1)SDRAM 控制模塊的使用。

(2)在 Nios II 中讀寫(xiě) SDRAM 芯片。

2015-12-14 15:40:33 0

0 華清遠(yuǎn)見(jiàn)FPGA代碼-SDRAM讀寫(xiě)控制的實(shí)現(xiàn)與Modelsim仿真

2016-10-27 18:07:54 26

26 作者:Steve Leibson, 賽靈思戰(zhàn)略營(yíng)銷與業(yè)務(wù)規(guī)劃總監(jiān) Adrian Cosoroaba和Terry Magee在本月MemCon上給出了關(guān)于DDR4 SDRAM接口的詳細(xì)展示,該演示

2017-02-08 14:03:01 608

608 控制器,在介紹控制器的邏輯結(jié)構(gòu)的基礎(chǔ)上,對(duì)FPGA與SDRAM間數(shù)據(jù)通信進(jìn)行了時(shí)序分析,實(shí)現(xiàn)SDRAM 帶有自動(dòng)預(yù)充電突發(fā)讀寫(xiě)和非自動(dòng)預(yù)充電整頁(yè)讀寫(xiě)。

2017-11-18 12:42:03 2054

2054

在很多通信芯片及系統(tǒng)的開(kāi)發(fā)中,常常需要用到存儲(chǔ)容量大、讀寫(xiě)速度快的存儲(chǔ)器。在各種隨機(jī)存儲(chǔ)器件中,SDRAM的價(jià)格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較,SDRAM的控制

2017-11-28 19:51:26 5

5 -ST固件庫(kù)版本:1.5.1 【 !】功能簡(jiǎn)介: 讀寫(xiě)板載的 SDRAM 芯片。 學(xué)習(xí)目的:學(xué)習(xí)STM32的FMC驅(qū)動(dòng)及SDRAM內(nèi)存器。 【*】注意事項(xiàng): 無(wú) 【 !】實(shí)驗(yàn)操作: 電腦端使用串口調(diào)試

2017-12-13 15:13:37 18

18 所以SDRAM需要在電容的電量放完之前進(jìn)行刷新;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)的讀寫(xiě)。” 這只是對(duì)SDRAM的概念介紹,下面再簡(jiǎn)單的看一下SDRAM的內(nèi)部結(jié)構(gòu)。

2018-03-29 09:30:54 7542

7542

問(wèn):如何操作SDRAM的自刷新命令而不影響正常讀寫(xiě)操作? 眾所周知,SDRAM從開(kāi)始工作伊始,一直伴隨著64ms刷新一遍的最基本規(guī)定(假設(shè)該SDRAM有4096行,那么必須大約15us的時(shí)間就要發(fā)出

2018-06-20 10:41:32 10512

10512

操作,設(shè)計(jì)了DDR SDRAM 的數(shù)據(jù)與命令接口。用控制核來(lái)簡(jiǎn)化對(duì)DDR SDRAM 的操作,并采用自頂至下模塊化的設(shè)計(jì)方法,將控制核嵌入到整個(gè)數(shù)據(jù)采集系統(tǒng)的控制模塊中,完成了數(shù)據(jù)的高速采集、存儲(chǔ)及上傳

2019-08-14 08:00:00 3401

3401

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫(xiě)SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文主要包括了:FPGA讀寫(xiě)SDRAM的實(shí)例,SDRAM控制器核心介紹,系列SDRAM數(shù)據(jù)手冊(cè)

2018-12-25 08:00:00 56

56 對(duì)于mig與DDR3/DDR2 SDRAM的讀寫(xiě)時(shí)序我們不需要了解太多,交給mig就可以了。

2019-03-03 11:11:53 5640

5640

SF-EPIC開(kāi)發(fā)板上使用的是三星SDR SDRAM (K4S641632)。由于控制SDRAM的讀寫(xiě)不同于之前的很多簡(jiǎn)單接口實(shí)驗(yàn)(它們對(duì)時(shí)序的要求都不高,即便不做時(shí)序約束也無(wú)關(guān)緊要),SDRAM

2019-03-06 14:01:51 2

2 同步動(dòng)態(tài)隨機(jī)存取內(nèi)存(synchronous dynamic random-access memory,簡(jiǎn)稱SDRAM)是有一個(gè)同步接口的動(dòng)態(tài)隨機(jī)存取內(nèi)存(DRAM)。通常DRAM是有一個(gè)異步接口

2019-03-07 15:12:46 3025

3025 的。 SDRAM,同步的DRAM,即數(shù)據(jù)的讀寫(xiě)需要時(shí)鐘來(lái)同步。 DRAM和SDRAM由于實(shí)現(xiàn)工藝問(wèn)題,容量較SRAM大。但是讀寫(xiě)速度不如SRAM,但是現(xiàn)在,SDRAM的速度也已經(jīng)很快了,時(shí)鐘好像已經(jīng)有150兆的了。那么就是讀寫(xiě)周期小于10ns了。SDRAM雖然工作頻率高,但是實(shí)際吞吐率要打折扣。

2019-04-01 16:24:29 35283

35283 SDRAM有一個(gè)同步接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。時(shí)鐘被用來(lái)驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的指令進(jìn)行管線(Pipeline)操作。這使得SDRAM與沒(méi)有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個(gè)更復(fù)雜的操作模式。

2019-09-12 07:04:00 1896

1896

SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

2019-09-12 07:02:00 2009

2009

DDR2 設(shè)備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標(biāo)準(zhǔn),該電氣標(biāo)準(zhǔn)具有較低的功耗。與TSOP比起來(lái),DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1793

1793

采用單端(Single-Ended)時(shí)鐘信號(hào),第二代、第三代與第四代由于工作頻率比較快,所以采用可降低干擾的差分時(shí)鐘信號(hào)作為同步時(shí)鐘。SDR SDRAM的時(shí)鐘頻率就是數(shù)據(jù)存儲(chǔ)的頻率,數(shù)據(jù)讀寫(xiě)速率

2020-04-03 16:04:01 1489

1489 DDR SDRAM的原理及特點(diǎn):DDR SDRAM不需要提高時(shí)鐘頻率就能加倍提高SDRAM的速度,因?yàn)樗试S在時(shí)鐘脈沖的上升沿和下降沿讀寫(xiě)數(shù)據(jù)。至于地址和控制信號(hào),還是跟傳統(tǒng)的SDRAM一樣,在時(shí)鐘的上升沿進(jìn)行傳輸。

2020-08-10 17:33:21 603

603

SDRAM 是一種 RAM 類型的易失性存儲(chǔ)器件,因其具有較大的容量和相對(duì)較低的價(jià)格在嵌入式系統(tǒng)中應(yīng)用廣泛。

2020-09-01 10:40:23 7162

7162

平衡。這樣必須有一套合理多通道復(fù)用仲裁方法,達(dá)到整個(gè)數(shù)據(jù)存儲(chǔ)效率最大化,用最小的存儲(chǔ)空間達(dá)成最大的平均吞吐。 外部高速緩存的基本讀寫(xiě)流程描述 外部緩存SDRAM (DDR)由于讀寫(xiě)共用一個(gè)物理接口,所以讀寫(xiě)需要分時(shí)產(chǎn)生,讀時(shí)不能寫(xiě)

2020-11-20 15:54:54 635

635 針對(duì)SDRAM 操作繁瑣的問(wèn)題,在對(duì)SDRAM 存儲(chǔ)器和全頁(yè)突發(fā)式操作進(jìn)行研究的基礎(chǔ)上,提出一種簡(jiǎn)易SDRAM 控制器的設(shè)計(jì)方法。該設(shè)計(jì)方法充分利用全頁(yè)式高效率存取的優(yōu)點(diǎn),對(duì)SDRAM 進(jìn)行配置、全頁(yè)突發(fā)式讀寫(xiě)時(shí),操作方便。在實(shí)現(xiàn)sDRAM 的快速批量存儲(chǔ)方面,具有良好的應(yīng)用價(jià)值。

2020-12-18 16:13:18 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA讀寫(xiě)SDRAM存儲(chǔ)器的實(shí)例工程文件和程序免費(fèi)下載。

2020-12-18 16:13:13 10

10 目前,在很多通信芯片及系統(tǒng)的開(kāi)發(fā)中,常常需要用到存儲(chǔ)容量大、讀寫(xiě)速度高的存儲(chǔ)器。在各種隨機(jī)存儲(chǔ)器件中,SDRAM 的價(jià)格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較

2021-06-30 09:16:47 2346

2346

FPGA作為ARM的SDRAM使用的LPC3250與FPGA接口程序(華為嵌入式開(kāi)發(fā)工程師拉勾網(wǎng))-FPGA作為ARM的SDRAM使用的LPC3250與FPGA接口程序,適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-08-04 12:09:30 22

22 SDRAM有一個(gè)同步接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。時(shí)鐘被用來(lái)驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的...

2022-01-26 19:40:35 1

1 Bank/Row active 在對(duì)SDRAM進(jìn)行讀寫(xiě)時(shí),需要先激活對(duì)應(yīng)的bank和行,該命令用于選擇一個(gè)bank的一行進(jìn)行激活,以便接下來(lái)進(jìn)行讀寫(xiě)訪問(wèn)。

2022-12-28 14:34:16 540

540 電子發(fā)燒友網(wǎng)站提供《如何擴(kuò)展USB接口進(jìn)行對(duì)U盤(pán)的讀寫(xiě).doc》資料免費(fèi)下載

2023-10-25 10:15:18 0

0 。 SDRAM是一種集成電路存儲(chǔ)器,可以通過(guò)同步鐘信號(hào)進(jìn)行數(shù)據(jù)讀寫(xiě)。與傳統(tǒng)的靜態(tài)隨機(jī)存儲(chǔ)器(SRAM)相比,SDRAM具有更高的存儲(chǔ)密度和更低的成本。擴(kuò)展SDRAM接口使得微控制器能夠使用外部

2024-01-04 14:09:23 343

343

?

? ??

??

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論