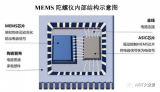

微機電(MEMS)陀螺廣泛應用于航空、汽車自動化和消費類電子產品等領域,按照振動結構的不同,主要分為線振動陀螺和旋轉振動陀螺。隨著MEMS陀螺成本功耗不斷降低、體積重量逐漸減小,對其數字化方案也提出了新的要求如高精度、高采樣頻率等。為使MEMS陀螺能在高頻率下工作,數字化電路就需要具備高采樣頻率,而目前MEMS陀螺的數字化主要是通過采用嵌入式現場可編程門陳列(FPGA)、數字信號處理器(DSP)芯片或者它們的組合來實現。

最終使用MEMS陀螺在該平臺上進行測試驗證,使陀螺的信號解調和控制能在PC端實現,實際的使用過程比一般的FPGA或者DSP更加便捷。通過PCIe(PCIexpress)總線,實現PC和采集卡的高速傳輸,最大控制延時小于10μs.

1、計算機實時控制系統穩定低延遲優化設計

實時性作為陀螺測控系統的關鍵指標,本節將著重設計和優化控制系統的低延時性和穩定性。第一部分低延遲性優化主要包括硬件優化和軟件優化。硬件優化需要考慮高速總線的類型和高速總線的傳輸控制方式;而軟件優化則主要涉及到操作系統驅動層面的優化以及控制算法優化。第二部分穩定性優化是讓計算機實時控制系統穩定地產生輸出信號,在實際工程中則是避免該系統對陀螺設備的控制受到中斷延時和傳輸延時波動的影響。

1.1、數據傳輸的低延優化

圖1 ?實時測控平臺低延遲優化方案

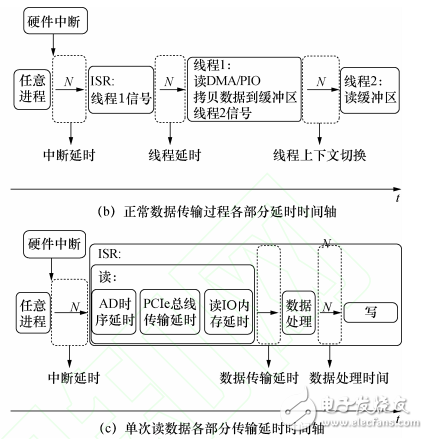

圖1a展示了實時測控平臺的軟硬件框架和數據流向。硬件中斷發出后,AD采集到的數據需要經過接口轉換層、FPGA的PCIeIP核、PCIe總線等才能到達計算機IO內存空間。完成內存地址映射后,用戶程序就可以從該內存讀取數據,進行數據處理。在實際多線程的數據傳輸中,還會產生額外的延時,如圖1b中所示,有中斷延時、線程延時和線程上下文切換延時等。其中中斷延時定義為計算機端硬件中斷產生到中斷服務程序(ISR)中第一條指令執行的時間差,主要與內核架構、CPU主頻和負載有關。由于線程之間的調度,內核需要準備時間,用于保存和恢復線程上下文環境、獲取或釋放信號量等。線程延時定義為ISR中從產生喚醒正在等待的線程信號,到線程執行第一條指令的時間差。線程上下文切換時間則為一個線程運行完到第二個線程第一條指令執行的時間差。

圖1.1 ?實時測控平臺低延遲優化方案

為了實現數據低延遲傳輸,下文將具體針對系統總線、傳輸控制方式、驅動程序(硬件和軟件)、數據處理等逐個進行優化。

1)高速總線的類型優化。

在測控系統中,總線是采集卡和計算機之間的橋梁,而總線的速度、帶寬等因素對系統的性能至關重要。本測控系統高速可靠的數據采集和傳輸依賴于計算機和采集卡之間的傳輸效率,因此選擇合適的總線可為后續板卡的進階優化提供保證。隨著計算機技術發展,總線技術也在不斷革新,應用范圍也從低、中速IO設備逐漸擴大到中高速設備。

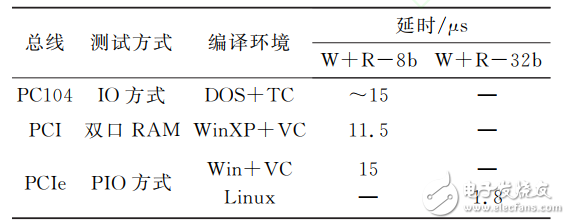

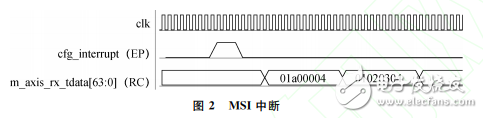

為了驗證不同總線在不同PC平臺下實際的傳輸速率,此處測試了4種情況(僅對目前已有的測試平臺):DOS系統下的PC104總線、WindowsXP下的PCI總線、Windows7以及Linux(內核4.2)下的PCIe總線。其中本測試平臺的ISA總線和PCI總線掛在相應的橋接芯片上,Windows7下的PCIe驅動是采用Jungo公司的Windriver工具自動生成的標準代碼。結果如表1所示。

表1 ?不同PC總線的IO讀寫延時測試

表1中“W+R-8b”代表讀和寫一個8位的數,“W+R-32b”代表讀和寫一個32位的數。通過測試發現,PCIe總線在傳輸速率上優于PC104和PCI總線。對于不同系統下PCIe總線的延時結果顯示,Windows下IO讀寫各1字節延時,耗時已達到15μs,而Linux下IO讀寫各4字節都只需1.8μs,原因是:Linux系統的實時性優于Windows系統的;另外,Windows下的驅動是Windriver工具自動生成的,并沒有針對性的進行過優化。后文中的測試結果都是在Linux系統下完成。

2)傳輸控制方式優化。

該測控平臺要求單次傳輸的數據量雖然比較少,但采樣頻率較高,對測控系統的動態響應能力提出了較高的要求。為滿足以上要求,需要一種快速的數據傳輸方式,常見的PCIe總線數據傳輸方式是PIO(programmedinput/output)和DMA(directmemoryaccess).DMA方式因不需要依賴CPU過量的中斷負載,一般在處理圖像等大數據傳輸中廣泛應用,但是在對小數據量高速、高動態響應的情況下,卻無法保證數據傳輸的及時性。

測試結果如表2所示,在Linux下,DMA方式讀16字節的數據,傳輸時間就已經超過了10μs.而PIO方式能實現小數據量高速傳輸,更適合本測控平臺。但是還需要對PC端PCIe驅動進一步優化,保證實時性。

表2 ?DMA和PIO傳輸時間對比

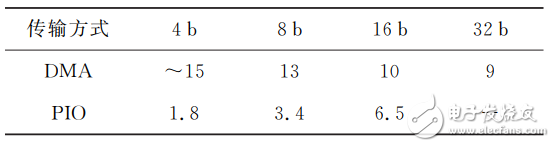

另外,PC和采集卡通訊有2種常見的方式:一種方式是輪詢狀態寄存器,另一種方式是使用中斷。當輪詢頻率過快的情況下,PC負載也會大,此時無法保證CPU能及時響應,必然會產生較大的延時;而中斷方式能明顯緩解PC負載過重的情況。硬件中,外圍芯片FPGA中的PCIeIP核支持兩種不同的中斷方式:MSI中斷和Legacy中斷.MSI中斷是基于消息機制的,相比Legacy中斷更高效更快速。為此,在FPGA中單獨編寫了一個中斷處理模塊,就能實現將硬件的MSI中斷請求通過PCIe總線發送到PC端。下文搭建了一個產生MSI控制信號的仿真環境,對MSI中斷進行了仿真驗證。模擬仿真了兩個設備:RC(RootComplex)和EP(EndPointDevice),分別由PC機和PCIe板卡模擬,仿真結果如圖2所示。

圖2中,cfg_interrupt為EndPointDevice產生的中斷信號,中斷發生后,RootComplex接收到數據包m_axis_rx_tdata,其中01a00004為消息頭,數據為0x01020304.

3)PC端PCIe驅動優化。

通常情況下,內核層PCIe驅動編寫好以后,開發者會給用戶提供一個通用的應用庫,用戶可以在用戶層完成相關算法的編寫,方便研究人員更快速地進行開發工作。考慮到用戶層權限低,用戶和內核空間的數據傳輸存在延時會影響系統穩定性,降低數據傳輸速率。因此,本平臺將控制算法的實現搬移到內核層,同時也給用戶提供了一個相應的庫,方便用戶修改控制算法中的參數。

4)控制算法的優化。

前面提到算法在內核層實現,陀螺閉環控制中,需要產生正弦余弦信號。為了解決內核浮點兼容性和減少指令計算時間,本平臺采用查表的方式,自制了一個正余弦表,將浮點運算轉換為定點運算。因為PC機CPU主頻高,所以查表的方式也能加速代碼的運行。

1.2、穩定的實時數據傳輸設計

低延遲優化能使數據在最短時間里從硬件傳輸到PC端。但是由于PC安裝的是多任務的操作系統,無法保證每次都能在一個周期的同一個時間點響應中斷,這一特性決定了這個最短時間不是一個固定值,而是一個范圍。在實際中,取值不定的這個最短時間會引發數據傳輸的不穩定,從而導致對陀螺的控制不連續。

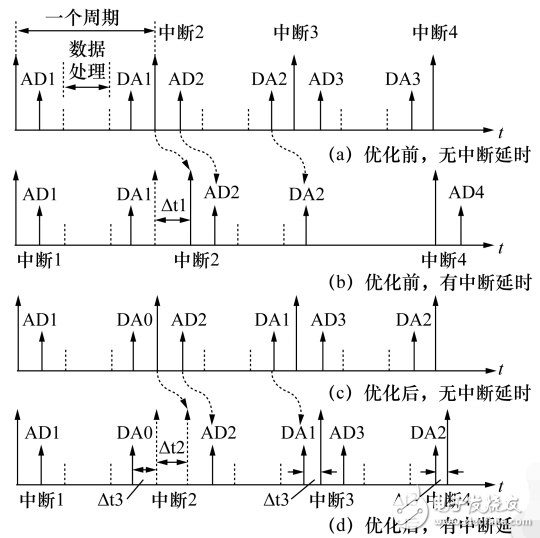

針對陀螺控制的不連續問題,以中斷延時為例,分析了由該現象產生的負面影響,并設計了一套可靠的控制時序,如圖3所示。假設它們都發生在ISR中,在一個周期中,進中斷函數后,先讀取下位機中AD的數據,進行數據處理,將解析完的數據再經過總線返回DA的值。圖3a表示在中斷和傳輸延時都固定時,正常的數據傳輸過程。而實際應用中,中斷和傳輸延時都會波動。以中斷延時為例,圖3b中第二個中斷信號到達時,假設已延時△t1,后續的讀寫操作相應的也會延遲△t1.當FPGA(下位機)往DA2寄存器寫數據的時刻,寫入的是上一周期中的DA1里的值,因為PC端并沒有及時返回DA2的值(延時△t1),導致數據沒有實時更新;另外,還有丟失中斷的可能性,如圖3b中的中斷3.這兩個問題都將加大陀螺控制的不穩定性。

圖3 ?數據傳輸控制時序優化

由此可知,為了達到陀螺數據傳輸的穩定性和可靠性要求,除了要優化MSI中斷控制方式和PIO方式傳輸方式,還需要上位機即PC和下位機即FPGA之間制定一套高效的握手協議。

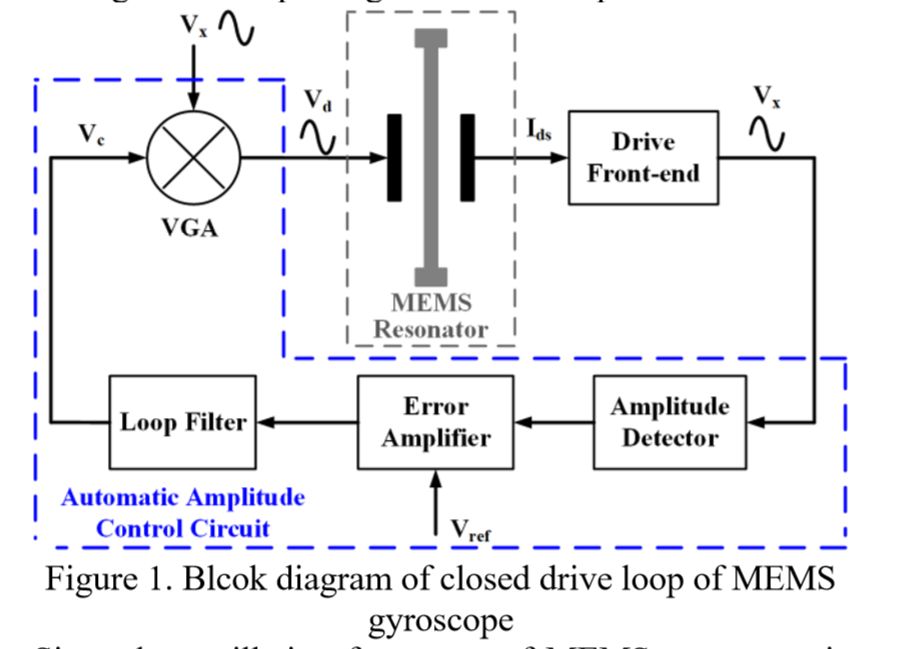

2、陀螺控制系統

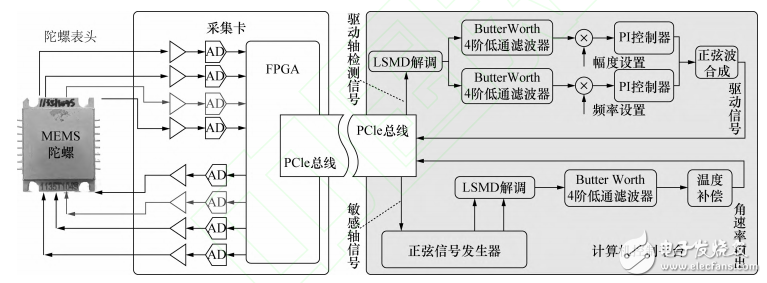

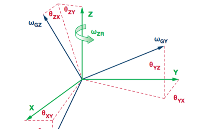

根據陀螺的工作原理,陀螺數字控制系統詳細的總框圖如圖4所示。陀螺數字控制系統由4個部分組成:陀螺表頭(包括前置處理電路)、ADC與DAC調理電路及FPGA外圍電路、系統總線PCIe的控制和PC端的陀螺控制算法。

圖4 ?完整的系統框圖

第1部分是和陀螺直接連接的前置放大電路,前置電路產生陀螺的驅動電壓并對陀螺輸出的信號做初步的放大處理,用于提高信號的信噪比。

第2部分是AD和DA數據采集卡。由于既要采集AD的數據和控制DA的數據輸出,又要與PC端進行高速的通訊,在這里采用能支持PCIe2.0的XilinxArtix7FPGA,FPGA大大簡化了數字電路的設計難度,便捷地處理AD和DA的時序還能提升PCB板的集成度。需要注意的是,這里的FPGA主要用于簡化數字電路的設計以及實現和計算機進行高速通信,并不涉及陀螺控制信號的處理。

第3部分是FPGA和PC進行高速通訊的PCIe總線。

第4部分則是PC端的陀螺算法實現,

主要包括陀螺驅動軸頻率閉環和幅度閉環控制。經過LSMD(leastsquaredmeandifference,最小均方差)解調以后的驅動軸檢測信號分為正交分量和同相分量:其中正交分量與參考信號有90°的相位差,可以近似反映陀螺本身的幅值信息;而同向分量與參考信號同相位,可以近似反映陀螺本身的相位信息。低通濾波用于除去二倍頻分量,在實際的閉環過程中,首先給陀螺驅動軸頻率設定一個預估值,此時陀螺的驅動軸檢測信號和驅動信號相位差接近-90°,并通過PI控制器作為反饋量,閉環控制驅動軸的輸入頻率,最終使其穩定在諧振頻率。

3、實驗結果及分析

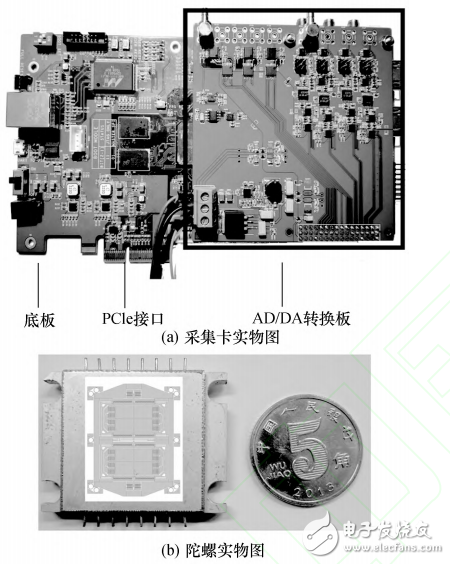

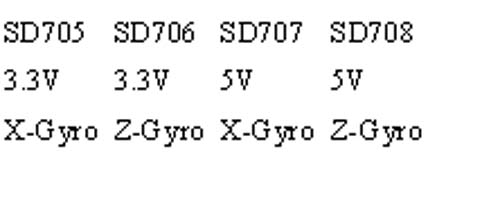

圖5a為PCIe的采集板卡:底板上主要是XilGinxArtix7芯片和PCIe的接口,主要功能是用于簡化外圍電路和PCIe總線的邏輯控制;AD/DA轉換板上是AD和DA的調理電路,用于高精度陀螺信號的采集和控制信號的發生。圖5b是用于測試的MEMS陀螺。

圖5 ?采集卡和實際用陀螺

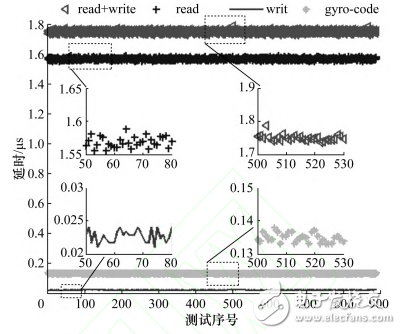

3.1、總延時時間消耗分布測試

為了進一步了解程序運行時各部分功能所占用的時間,對數據讀寫以及代碼量進行了延時測試。圖6中,“read”代表PC端讀4字節所占用的時間,“write”代表PC端寫4字節到板卡所占用的時間,“read+write”代表讀和寫各4字節所占用的時間,“gyroGcode”代表單軸陀螺代碼(小于1000條指令)運行占用的時間。

圖6 ?傳輸耗時分布圖

3.2、陀螺控制測試結果

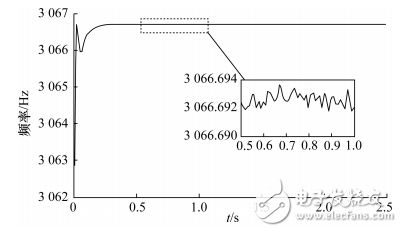

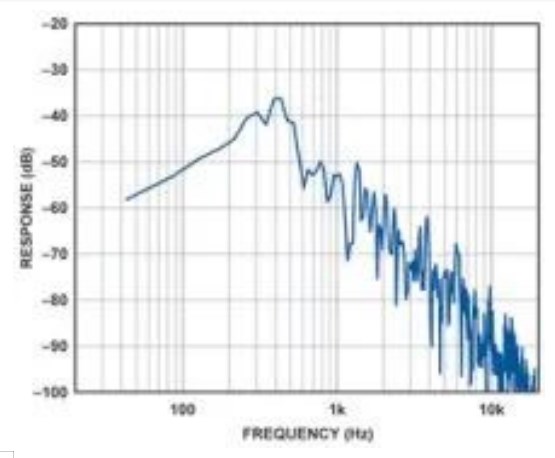

為了驗證測控平臺的可行性,本系統對陀螺控制程序進行簡化,僅有陀螺驅動軸閉環控制(包括幅值閉環和頻率閉環控制),檢測軸開環,無自補償環路。實測的頻率閉環控制過渡過程如圖7所示,大概在0.3s以后,驅動頻率最終穩定在3067Hz,頻率閉環控制達到了很好的控制效果。

圖 7 ?頻率閉環控制曲線

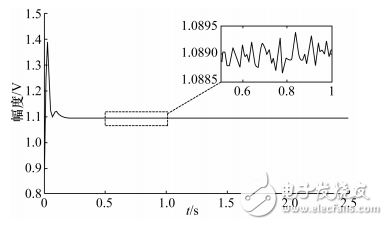

實測的幅值閉環控制過渡過程如圖8所示,幅值最終穩定在1V左右,與設定值相符

圖8 ?幅度閉環控制曲線

4、結論

本文提出了一個用于MEMS陀螺的PCIe實時測控平臺。通過硬件和軟件優化,減少數據傳輸延時,并且利用高效的數據傳輸時序,實現了陀螺驅動頻率閉環和幅度閉環控制,使線振動陀螺工作在諧振頻率上且幅值穩定,最終將測控系統的數據傳輸延時降低至10μs.下一步將通過優化實時內核,提高該測控系統的采樣頻率,為更高工作頻率的陀螺提供高速、可靠、穩定的數據傳輸方案.

電子發燒友App

電子發燒友App

評論