從低密度的后通孔TSV 硅3D集成技術(shù),到高密度的引線混合鍵合或3D VSLI CoolCubeTM解決方案,研究人員發(fā)現(xiàn)許多開發(fā)新產(chǎn)品的機(jī)會(huì)。本文概述了當(dāng)前新興的硅3D集成技術(shù),討論了圖像傳感器、光子器件、MEMS、Wide I/O存儲(chǔ)器和布局先進(jìn)邏輯電路的硅中介層,圍繞3D平臺(tái)性能評(píng)估,重點(diǎn)介紹硅3D封裝的主要挑戰(zhàn)和技術(shù)發(fā)展。

硅的3D應(yīng)用機(jī)會(huì)

從最初為圖像傳感器設(shè)計(jì)的硅2.5D集成技術(shù),到復(fù)雜的高密度的高性能3D系統(tǒng),硅3D集成是在同一芯片上集成所有功能的系統(tǒng)芯片(SoC)之外的另一種支持各種類型的應(yīng)用的解決方案,可用于創(chuàng)建性價(jià)比更高的系統(tǒng)。硅3D集成技術(shù)的主要優(yōu)勢(shì):縮短互連線長度,降低R.C積,讓先進(jìn)系統(tǒng)芯片(SoC)能夠垂直劃分功能,進(jìn)一步降低系統(tǒng)尺寸和外形因數(shù)。

在首批出現(xiàn)的3D產(chǎn)品中,業(yè)界認(rèn)為存儲(chǔ)器層疊方案可以提高DRAM/邏輯控制器的容量/帶寬,適用于高性能計(jì)算系統(tǒng)、圖形處理器、服務(wù)器和微型服務(wù)器(圖1)。

圖1:與邏輯控制器相連的DRAM混合存儲(chǔ)器層疊模塊(HMC)(來源:美光)。

美光的混合存儲(chǔ)器模塊(HMC)和海力士的寬帶存儲(chǔ)器(HBM)開始進(jìn)入量產(chǎn)階段,這兩個(gè)解決方案都連接硅中介層,面向高性能計(jì)算(HPC)應(yīng)用。

Xilinx于2012年提出在硅中介層制造現(xiàn)場可編程門陣列(FPGA)的概念,該技術(shù)最初采用CoWoS集成工藝,引起供應(yīng)鏈巨變,后來改用兩個(gè)28nm FPGA和兩個(gè)65nm混合信號(hào)芯片堆疊在65nm中介層上。

服務(wù)器對(duì)高帶寬和低功耗的進(jìn)一步需求催生了將CMOS/BiCMOS和光子功能分開的每個(gè)通道傳輸速率高達(dá)25 Gb/s的硅光子器件平臺(tái)(圖2),以及產(chǎn)生了硅光中介層集成技術(shù)。

圖2左圖:一個(gè)采用3D層疊技術(shù)在光子器件上安裝BiCMOS器件的光學(xué)封裝測(cè)試芯片;右圖:該芯片在RX 25/28Gbps時(shí)的電眼測(cè)量圖

研究人員認(rèn)為在邏輯層上堆疊存儲(chǔ)層可以大幅降低存儲(chǔ)器與處理器之間的接口功耗。堆疊在邏輯層上的Wide I/O DRAM(圖3)的能效是LPDDR解決方案的四倍,并且在未來幾年內(nèi)傳輸速率將達(dá)到50 GB/s 。

圖3:置于65nm邏輯層上的Wide IO存儲(chǔ)器,頂層/底層具有1250個(gè)TSV互連線,1000個(gè)倒裝片銅柱(底部/ BGA)。

為了給高性能計(jì)算或電信應(yīng)用提供高帶寬性能,研究人員設(shè)計(jì)了一個(gè)基于異步3D Network-On-Chip架構(gòu)的先進(jìn)邏輯層疊方案,采用3D封裝方法將兩顆相同的邏輯裸片正反面層疊,證明了可擴(kuò)展的同構(gòu)3D層疊方法的技術(shù)優(yōu)勢(shì)。該3D集成方案的邏輯芯片采用CMOS 65nm制造工藝,使用寬高比為1:8 的TSV Middle通孔和40μm節(jié)距的銅柱連接芯片(圖4)。

圖4 :采用邏輯芯片層疊方法的異步Network-on-Chip 3D架構(gòu)

在2.5D TSV被引入CMOS圖像傳感器(圖5)后,3D集成技術(shù)從2013年開始進(jìn)入智能手機(jī)和平板電腦中,目前市場上存在多個(gè)不同的相互競爭的層疊技術(shù),數(shù)字處理層可以布局在硅襯底上,而不是像素陣列電路上,通過功能劃分和工序優(yōu)化,圖像傳感器尺寸變得更加緊湊(圖6)。

圖5:晶圓級(jí)攝像頭2.5D后通孔方法。

圖6:索尼圖像傳感器[11]采用直接鍵合+ TSV的晶圓級(jí)層疊解決方案(來源:System Plus Consulting)。

圖7:博世采用TSV 3D技術(shù)在ASIC中集成3軸加速度計(jì)(來源:Yole Developpement)。

3D技術(shù)挑戰(zhàn)

3D集成被廣泛應(yīng)用證明,TSV等先進(jìn)技術(shù)節(jié)點(diǎn)的基本模塊技術(shù)已經(jīng)成熟(圖8)。現(xiàn)在,研發(fā)重點(diǎn)轉(zhuǎn)移到由市場需求驅(qū)動(dòng)的新挑戰(zhàn)上:封裝應(yīng)變管理;通過改進(jìn)散熱效率提高系統(tǒng)性能;提高芯片間的互連密度。

圖8:6x55μm 28FDSOI Via Middle 集成TEM視圖,對(duì)測(cè)試載具良率沒有影響,通過了TDDB、EMG和TC測(cè)試

對(duì)于較大的硅中介層來說,熱機(jī)械應(yīng)變是一個(gè)需要考慮的難題,需要解決硅光子變化以及HBM/CPU集成封裝問題,疊層之間的熱膨脹系數(shù)(CTE)不匹配將會(huì)致使裸片翹曲。根據(jù)裸片級(jí)曲率對(duì)溫度的敏感性,研究人員開發(fā)出一種應(yīng)變監(jiān)測(cè)和翹曲補(bǔ)償策略,通過綜合使用陰影莫爾干涉儀(圖9)、現(xiàn)場應(yīng)力傳感器和有限元建模(FEM)方法,創(chuàng)建了介電層特性模型。(圖10)

對(duì)于MEMS,微縮化是除成本和性能之外的另一個(gè)差異化要素。2007年以來,技術(shù)發(fā)展趨勢(shì)是開發(fā)3D異構(gòu)MEMS功能,包括通過TSV連接IC(圖7)。

圖9:使用ShadowMoiré干涉儀在室溫下測(cè)量80 μm硅中介層的裸片級(jí)翹曲,測(cè)量結(jié)果有一個(gè)球面非線性翹曲。

圖10:中介層機(jī)械應(yīng)力場模擬(左圖)和8片負(fù)應(yīng)變傳感器放置方式(右圖)。

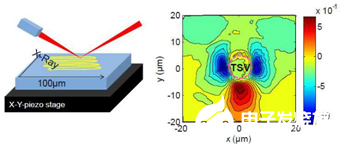

研究人員利用X射線衍射技術(shù)對(duì)TSV集成引起的局部應(yīng)變進(jìn)行了表征實(shí)驗(yàn)(圖11)。同步輻射源納米級(jí)聚焦X射線衍射測(cè)量圖高亮顯示了TSV周圍應(yīng)變的2D平面分布情況,并證明應(yīng)變分布與3D FEM模擬相關(guān)。

圖11:使用納米聚焦X射線束衍射方法測(cè)量的TSV周圍應(yīng)變2D平面空間應(yīng)變分布。稀化樣品是在室溫和原位退火過程中完成測(cè)量。

熱管理是業(yè)界關(guān)注的影響3D性能的一個(gè)主要問題。精確的FEM模型和在TSV 3D電路上校準(zhǔn)的緊湊型熱模型有益于設(shè)計(jì)流程改進(jìn),研究人員做過高導(dǎo)熱率散熱器材料的評(píng)測(cè),這種材料可以提高封裝的散熱性能,耐受更大的耗散功耗,可以顯著降低潛在的局部熱點(diǎn)效應(yīng)(圖12),高性能冷卻技術(shù)被證明具有嵌入式微流體特性(圖13)。

圖12:3D電路被動(dòng)散熱器評(píng)估:頂層裸片使用銅散熱器與使用熱解石墨薄板(PGS)散熱器的溫度原位測(cè)量對(duì)比(300mW熱點(diǎn))。

頂層裸片上的60個(gè)微通道,通道深125 μm,寬75 μm,H2O /乙二醇混合物,在0.75 0,75 cm3/s,沒有散熱器時(shí),T》450°C

圖13左圖)在一個(gè)熱點(diǎn)密集且密閉Wioming 3D 電路上的微流體冷卻技術(shù)(2000 W /cm2)。右圖)在Si中蝕刻的微通道和鰭引腳的SEM圖像

互連密度提高:混合引線鍵合工藝是一個(gè)前景很好的微凸點(diǎn)技術(shù)的替代方法,或者可以替代裸片互連使用的TSV直接氧化物鍵合方法(圖14)。

圖14:互連線間距隨著新技術(shù)解決方案和機(jī)會(huì)的出現(xiàn)而發(fā)展變化。

混合鍵合工藝允許在后工序進(jìn)行低節(jié)距的面對(duì)面的層疊,但也給集成和設(shè)計(jì)優(yōu)化帶來新挑戰(zhàn)。

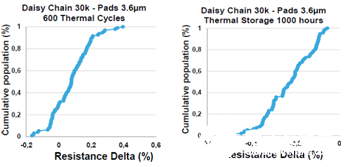

CEA-Leti 發(fā)布了一個(gè)集成背面照明(BSI)與控制邏輯單元的晶圓級(jí)混合鍵合封裝,證明低節(jié)距(5μm至24μm)焊盤對(duì)準(zhǔn)精度在400nm以下,并使用了2x6金屬層0.13μm 雙大馬士革鑲嵌工藝(圖15)。

圖15:混合鍵合封裝的SEM圖像(俯視圖和3D視圖),包括BSI成像器結(jié)構(gòu)+邏輯的所有金屬層。

為避開非鍵合區(qū)域,必須優(yōu)化焊盤設(shè)計(jì)和表面拋光工序。套刻精度優(yōu)于250 nm的高性能對(duì)準(zhǔn)系統(tǒng)能夠?qū)崿F(xiàn)最低7μm的高密度節(jié)距(圖16)。

研究人員做了鍵合界面完整性表征實(shí)驗(yàn),在附加的熱應(yīng)變實(shí)驗(yàn)后進(jìn)行EDX分析,未在氧化層發(fā)現(xiàn)銅擴(kuò)散現(xiàn)象(圖17)。

圖17:EDX混合鍵合界面表征,實(shí)驗(yàn)顯示無銅通過界面擴(kuò)散(在焊盤失準(zhǔn)情況下)。

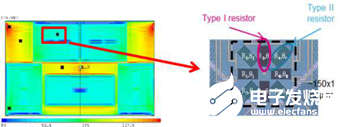

一份有關(guān)混合鍵合技術(shù)的電學(xué)表征實(shí)驗(yàn)和初步可靠性的研究報(bào)告證明,在300mm層疊晶片上,良率達(dá)到100%,在30k菊花鏈時(shí),界面電阻離差較低。儲(chǔ)熱循環(huán)實(shí)驗(yàn)(圖18)結(jié)果證明,技術(shù)成熟的圖像傳感器專用混合鍵合工藝實(shí)現(xiàn)了低電阻離差(小于0.5%)(ST內(nèi)部數(shù)據(jù)待發(fā)布)。

圖18:混合鍵合可靠性實(shí)驗(yàn)結(jié)果。熱循環(huán)(左圖)和儲(chǔ)熱(右圖)測(cè)試的電阻離差小于0.5%。

直接鍵合的趨勢(shì):研究人員可能會(huì)想出更先進(jìn)的解決方案,例如,3D VLSI CoolCubeTM集成[22],該方案利用獨(dú)特的連接密度超過百萬/平方毫米的通孔技術(shù),可以垂直堆疊多層芯片,為異質(zhì)集成帶來新的機(jī)遇( 高微縮化的像素、CMOS與NEMS混合架構(gòu)、III-V/Ge材料)和設(shè)計(jì)靈活性,特別適合于線長微縮或神經(jīng)形態(tài)計(jì)算(圖19)。

底層FET工藝

體硅,F(xiàn)INFET, FDSOI…

標(biāo)準(zhǔn)工藝

W/SiO2金線

直接鍵合頂層有源器件

SOI + 回蝕或SmartCutTM 工藝

支持各種襯底、材料和對(duì)位

低熱預(yù)算頂層FET

通過SPER或納秒級(jí)激光回火激活摻雜

低溫外延層

低熱預(yù)算和低K襯墊

3D觸點(diǎn)實(shí)現(xiàn)與后工序

3D通孔=在氧化物層上制造標(biāo)準(zhǔn)的W型孔

銅線和低K金線

圖19 - CoolCubeTM 原理

結(jié)論

硅3D集成現(xiàn)已成為現(xiàn)實(shí),是一個(gè)高性能的半導(dǎo)體集成創(chuàng)新解決方案,可以替代因光刻技術(shù)投資龐大而在未來十年內(nèi)難以維持經(jīng)濟(jì)效益的標(biāo)準(zhǔn)“摩爾定律”。3D集成被選擇背后的動(dòng)因是性能、帶寬、復(fù)雜性、互連密度,以及系統(tǒng)微縮化、最終成本和價(jià)值鏈。熱管理、熱機(jī)械應(yīng)變和連接密度等難題都已有相應(yīng)的解決辦法。隨著直接混合鍵合套刻精度提高,業(yè)界可能會(huì)想出創(chuàng)新的集成方法,替代現(xiàn)有的裸片層疊解決方案,簡化產(chǎn)品價(jià)值鏈,開發(fā)出功能分區(qū)、高密度互連的高性能器件。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論