隨著先進封裝形式的逐漸普及,可選擇的低密度封裝類型正在增加。

幾家半導體封測公司正在為高端智能手機開發新一代的高密度扇出式封裝,與此同時,較低密度的扇出式封裝市場也正在醞釀更大的戰斗。

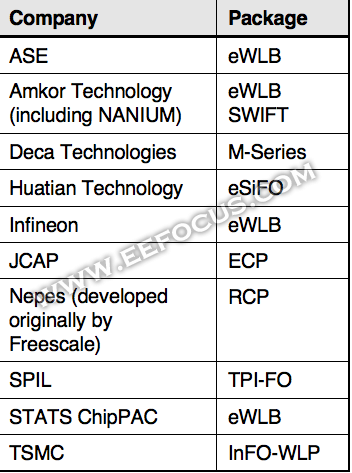

Amkor、ASE、STATS ChipPAC等公司提供傳統的低密度扇出式封裝服務,在這個市場上,正在出現一些具有競爭力的新型技術。低密度(有時也稱為標準密度)扇出式封裝是扇出式封裝市場的兩個主要類型之一,另一種類型是高密度扇出式封裝。

一般而言,扇出式技術能夠實現一種小型的封裝,可以集成比其他封裝類型更多的IO,但是它并不是唯一的選擇項。根據半導體封測服務提供商(OSTA)先進半導體工程公司(ASE)的說法,在移動設備、物聯網及其相關應用中,低密度(標準密度)扇出式封裝指的是IO數量小于500個、線寬和間距大于8um的封裝類型。

ASE表示,高密度扇出封裝針對中檔到高端應用,IO數量超過500個,線寬/間距小于8um。臺積電的InFO技術是高密度扇出封裝的典型例子,它被應用在蘋果最新款的iPhone手機上。其他OSAT廠商在高密度扇出封裝市場上激戰正酣。

低密度扇出封裝市場也在升溫。TechSearch國際公司總裁Jan Vardaman說:“臺積電用在蘋果手機上的InFO技術是高密度扇出封裝市場上的統治者,同時,市場上也存在很多標準密度扇出封裝類型,適合于很多種設備。”

Vardaman表示,標準密度扇出封裝的推動力包括音頻編解碼器、電源管理IC、雷達模塊和RF器件。高通公司是該領域最大的客戶。她說:“現在,除了高通公司之外,我們看到其他公司也開始大批量使用這種封裝。”

這個市場可能會在其它方面發生一些變化。總體來說,這個市場上的幾家供應商正在提供或準備提供六種或以上不同類型的低密度扇出封裝技術。Yole Développement公司的一名分析師Azemar表示:“這取決于你如何統計它們,長遠來看,這個市場容不下這么多類型的封裝,所以,有些可能會消失,有些雖然名字不同,但也可能會變得越來越像。”

哪種扇出類型的生命力比較長久最終取決于成本、可靠性和用戶的采納,所以,芯片制造商需要密切關注這個市場,以下是該市場近期的一些主要事件:

最先出現的扇出類型-嵌入式晶圓級球柵陣列(eWLB)- 經歷了長期供不應求,供應商現在開始增加產能。

ASE和Deca正在開發一種新的低密度扇出類型,似乎可以和eWLB競爭。

中國的幾家OSAT廠商正在進軍扇出封裝市場。

幾家封測公司正在開發面板級別的扇出,這是一種低密度扇出類型,有望降低扇出成本。

據Yole透露,整體扇出式封裝市場規模預計將從2014年的2.44億美元增長到2021年的25億美元。其中,低密度扇出市場規模預計將從2017年的3.5億美元增長到2022年的9.5億美元。 “這些數字可能會減少,具體取決于最終有多少廠家會轉向扇出技術。目前,市場對高通等大公司的依賴性較強。最終的市場規模還取決于面板級別扇出封裝能否快速面世,并提供更低的成本。”Azemar說。

什么是扇出型封裝?

相對來說,扇出型封裝是一個新事物。幾十年來,IC封裝過程比較簡單。 Lam Research先進封裝業務副總裁Choon Lee解釋說:“在傳統的封裝工藝中,成品晶圓首先被切割成很多個獨立的芯片,然后粘合和封裝。”

OSAT廠商最初一直使用這種方法,直到21世紀初,出現了一種叫做晶圓級封裝(WLP)的技術,事情發生了很大變化。“WLP,顧名思義,就是在芯片還在晶圓之上時進行封裝,”Lee在一篇博客中寫道。“WLP生成的芯片封裝尺寸較小(和芯片本身的尺寸大致相同),這是對尺寸敏感的智能手機登設備考量的一個重要因素,WLP的其它優勢包括精簡了制造過程,在切割之前就可以測試芯片功能。”

WLP封裝有兩種主要類型-芯片級封裝(CSP)和扇出(fan-out)。 CSP有時被稱為扇入式。KLA-Tencor高級營銷總監Pieter Vandewalle表示:“封裝類型的發展和進化主要是由最終應用推動的。扇入式/扇出式WLP主要由移動應用推動,這些應用需要高性能、高能效的薄而且小的封裝形式。”

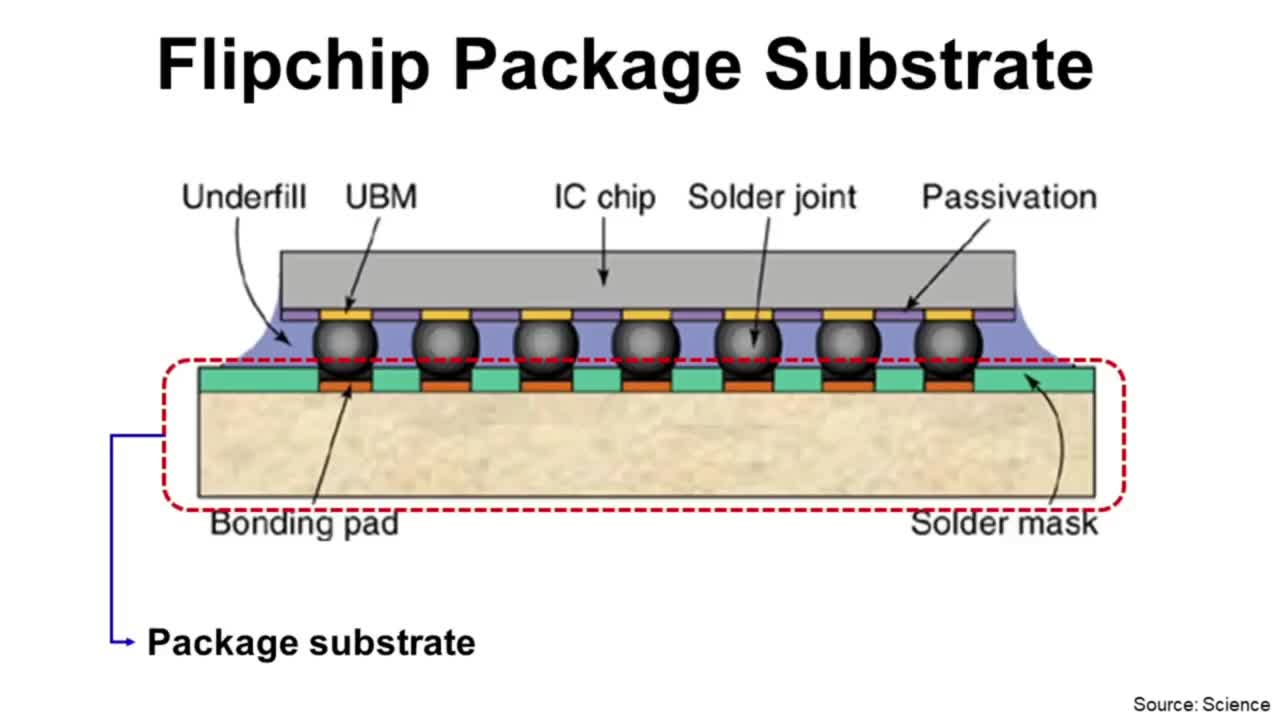

扇入式和扇出式封裝有些許的不同。其中一個主要區別就是這兩種封裝類型集成再分配層(RDL)的方式。RDL是將封裝的一部分和另一部分電氣連接在一起的銅金屬連接線。RDL是由線寬和間距來衡量的,如上所述,低密度扇出封裝的線寬和間距大于8um。

在扇入式封裝中,RDL向內走線,因此,當IO數量到達200個左右,層間互聯間距在0.6mm時,扇入式封裝就有些力不從心了。

但在扇出式封裝中,RDL可以向內走線,也可以向外走線,從而可以實現具有更多I/O數量且更薄的封裝。ASE工程高級主管John Hunt說:“在扇出式封裝中,你擴大了可用的封裝面積。”

在高密度扇出式封裝使用方面,蘋果是領頭羊。之前,智能手機的應用處理器使用層疊封裝技術(PoP),存儲器放在頂層,應用處理器放在底層。

因為技術成熟而且價格低廉,許多智能手機原始設備制造商仍然在堅持使用PoP技術。但是,當層間互聯間距到0.8mm左右時,PoP技術就有些力不從心了。所以蘋果公司在最新款的iPhone手機的應用處理器上轉向了扇出式封裝技術。蘋果最新的A11處理器基于臺積電的10nm工藝,使用臺積電的InFO扇出封裝技術,可以實現更小、更薄的封裝。

在其它應用場景中,客戶可能會將數字、模擬和射頻等不同類型的器件集成到扇出式封裝中,其中,數字芯片可能采用先進工藝,而模擬和射頻器件則使用成熟的老工藝。

采用先進工藝的器件和成熟老工藝的裸片可以分開,然后在同一個封裝中互聯起來。Hunt說:“采用扇出式封裝,你可以把多個裸片均勻或非均勻地組合成一個電氣互連的封裝。我們不僅可以將多個裸片放在一個封裝中,而且還可以放入MEMS、濾波器、晶體和被動器元件。”

扇出式封裝并不是將多個裸片集成到一個封裝內的唯一方案。事實上,客戶還有很多種選擇,包括2.5D/3D、扇出、系統級封裝(SiP)和引線鍵合技術。

根據TechSearch的統計,現如今,75%到80%的IC封裝采用了一種稱為引線鍵合的老互連方案。在這種方案中,一個被稱為引線接合器的系統使用細導線將一個芯片縫合到另一個芯片或襯底上。

在高端市場,OSAT廠商提供2.5/3D方案,這是一種使用硅通孔(TSV)的芯片堆疊技術。同時,SiP方案可以結合一系列裸片和被動元件,以實現一個獨立的功能。

哪種多裸片封裝技術更好呢?這取決于具體應用。“采用扇出式封裝還是SiP封裝取決于應用、帶寬需求和實際可用的資源。和引線鍵合式器件相比,它們都能實現性能的顯著提升,”TEL子公司TEL NEXX的戰略業務發展總監Cristina Chu說,“ 在復雜的FPGA器件中,縮短上市時間是SiP方案的主要優勢。在某些情況下,這些SiP甚至可以將來自不同工藝節點的組件結合在同一個封裝中。”

傳統扇出和新興扇出類型

在2005年左右,飛思卡爾和英飛凌分別推出了各自首個扇出式封裝類型。

2006年,飛思卡爾推出了一種名為“再分配芯片封裝(RCP)”的扇出技術,2010年,飛思卡爾將RCP許可給了Nepes。Nepes在韓國建設了一條使用RCP技術的300mm生產線。TechSearch的Vardaman表示:“Nepes正在生產雷達和物聯網模塊。(2015年,恩智浦收購了飛思卡爾。)

英飛凌的eWLB技術最初是為蜂窩電話中的基帶芯片設計的。英飛凌現在仍然擁有用于雷達模塊的200mm eWLB生產線,Vardaman說。

2007年,英飛凌還將eWLB技術授權給了ASE,一年之后,又與STATS ChipPAC達成了類似的協議。 后來,英飛凌將eWLB許可給了后來被Amkor收購的Nanium。這些授權協議賦予這些OSAT廠商使用eWLB封裝的權利。

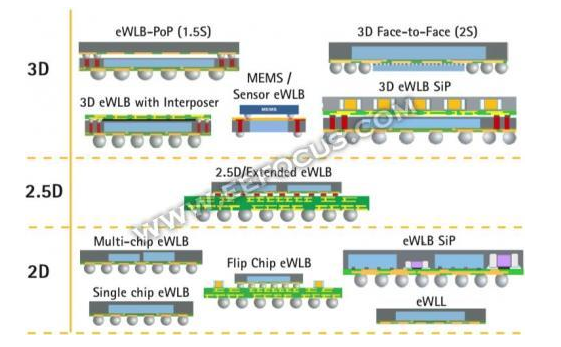

最初,eWLB是一種單芯片封裝,但是最終,這種技術逐漸進化到更復雜的可集成被動元件的多芯片形式。

“一般而言,2D eWLB器件通常用于中低密度應用。2.5D和3D eWLB器件適用于需要超過IO數量超過500個或1,000個的高端或高性能應用。但是,根據不同應用的需求,某些情況下,3D eWLB SiP封裝的IO數量也可以少于500個,”中國最大的半導體封測廠商長電科技集團(JCET)技術戰略總監Seung Wook Yoon解釋說。2015年,中國最大的OSAT廠商-長電科技收購了新加坡的STATS ChipPAC。

2D eWLB器件從2009年就已經開始出貨。Yoon說:“我們目前有許多2.5D和3D eWLB器件通過了客戶的認證,但均尚未達到大批量生產水平。”

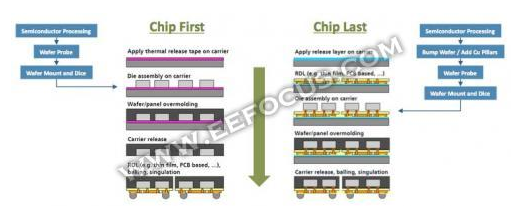

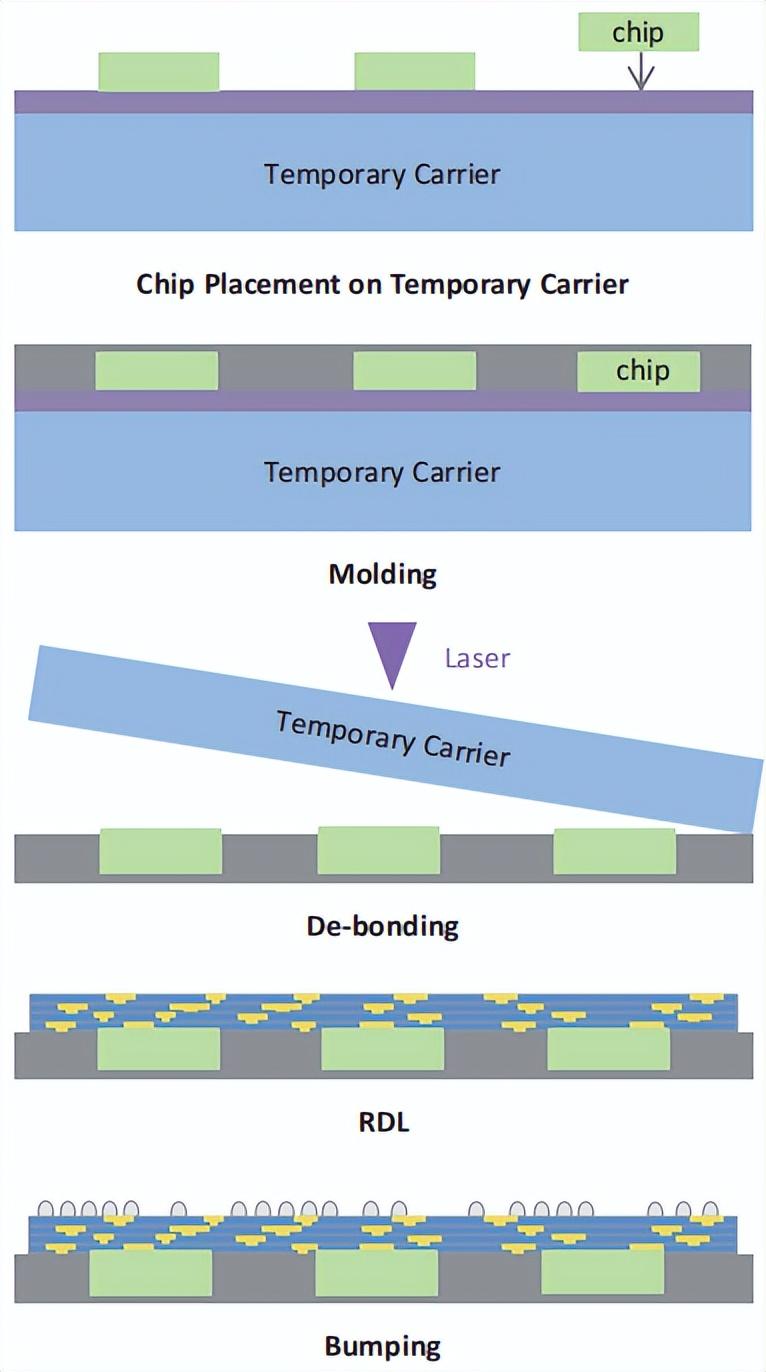

扇出型封裝有三種形式,第一種使用先放芯片/正面超下的工藝流程制造,另外兩種分別是先放芯片/正面朝上和后放芯片類型,有時也被稱為先放RDL。

在先放芯片/正面朝下的工藝流程中,在晶圓廠中,首先在晶圓上處理芯片,然后將芯片切割出來。通過使用抓取-放置系統,將裸片放在基于環氧樹脂模塑化合物的新晶圓上,這被稱為重組晶圓。

重組晶圓可以在200mm或300mm晶圓上加工。封裝就是在這個晶圓上進行的。然后,切割芯片,形成容納在扇出式封裝中的芯片。

先放芯片這種類型的封裝已經生產了將近十年。工藝流程不同的后放芯片這種封裝類型尚未被廣泛采用。

扇出封裝存在一些挑戰。在處理過程中,重組晶圓容易發生翹曲。當芯片嵌入到重組晶圓中時,在整個工藝流水中,芯片也容易移動,從而造成被稱為芯片移位的意外效應,這會影響產量和良率。

OSAT廠商已經克服了許多這些挑戰。2016年和2017年可能出了一些大問題。當時,由于高通的巨大需求,兩個主要的eWLB封裝供應商-星科金朋和Nanium的扇出封裝產能均出現供不應求的局面。

產能缺口促使客戶開始尋找其它類型的封裝,結果導致了eWLB市場的停滯。

作為回應,星科金朋和ASE都擴大了其eWLB產能。接下來,在2017年,Amkor收購了Nanium,給這家扇出封裝專家提供了一些支持。

現在,eWLB市場上有三家具備足夠產能的供應商,這個變化應該能夠重新啟動eWLB市場。 “低密度到中密度應用對FOWLP的需求持續增長。 我們在智能手機、5G或汽車應用領域有一些需要的IO數量少于500個的扇出封裝客戶,“Yoon說。 “FOWLP有許多新興的細分市場,比如5G毫米波器件、MEMS、指紋傳感器以及高級駕駛員輔助系統(ADAS)等汽車應用。”

不過,eWLB預計將在2018年面臨一些新的競爭。提供eWLB封裝技術的ASE也一直在與Deca科技合作開發另一種低密度扇出技術。賽普拉斯半導體公司的子公司Deca是該技術的原始開發商,該技術被稱為M系列。

此外,ASE正在與***的Siliconware Precision Industries(SPIL)合并。SPIL也正在研究一種叫做TPI-FO的扇出技術。

而且,ASE計劃在2018年上半年將M系列扇出技術推進到量產階段。與eWLB不同的是,M系列是一種芯片在先、裸片朝上的技術。

M系列解決了傳統扇出技術的一些問題。“在傳統的扇出封裝生產過程中,你必須使用高精度的倒裝芯片鍵合機來放置芯片,這個過程的吞吐量相對而言比較低,一個小時大約只能處理8000個裸片,”ASE的Hunt說。“有一個主要問題是裸片移位,封料后放置裸片時,它已經不在最初放置它的地方了,因為它移動了。”

為了解決這個問題,Deca開發了一種被稱為自適應圖案化的技術。 首先,使用高速表面貼裝系統以每小時30000-35000個裸片的速度將裸片放置在晶圓上。不過,每個芯片的放置精度不如傳統系統那么準確,為了彌補精度問題,Deca的技術會測量晶圓上每個裸片的實際位置。

“然后,我們重新計算RDL圖案,以適應每個晶圓上的每個裸片的移位。重新計算過程大約需要28秒。當晶圓到達成像系統的時候,圖案已經被重新計算出來了。”Hunt說。

將計算出來的新圖案數據送入成像系統。在eWLB中,傳統的光刻系統在裸片上圖案化出一個樣貌,Deca的技術使用專有的激光直接成像系統,就像直寫光刻一樣,不用使用掩模,就可以在裸片上寫入樣貌。

在Deca的技術中,激光直接成像系統將整個RDL圖案與測量過的裸片位置對齊,據推測,這種方式可以解決裸片移位問題。

競爭對手也正在關注這項技術。長電科技的Yoon說:“Deca的M系列解決方案有其獨特的優勢,但尚未在大批量生產中得到驗證。”

中國新勢力來了

與此同時,扇出市場也來了一些新勢力-中國人。例如,隸屬于江蘇長電科技(JCET)的江陰長電先進封裝有限公司(JCAP)有一個晶圓級封裝技術,說句題外話,長電科技收購了星科金朋。

中國大陸另外一家大型半導體封測廠商-天水華天科技-也開發了幾種封裝類型,其中就包括扇出型封裝。“江陰長電的晶圓級封裝已經量產了,華天科技的可能也接近量產。中國版本的扇出式封裝的工藝和原始的eWLB有所不同。”TechSearch的Vardaman表示。

天水華天科技的扇出技術被稱為eSiFO。在eSiFO中,先把晶圓蝕刻,形成一個縫隙,然后使用抓取-放置系統將裸片放置在間隙中,最后密封。

“這種技術使用的是硅載體,不需要模具化合物。這項技術正在吸引客戶的注意,因為應力低,翹曲也較少。我們的硅載體晶圓和嵌入在干法蝕刻出的溝槽內的裸片之間的CTE不匹配最小。而且,從根本上來說,這也是一個簡單的工藝,”華天科技集團美國地區銷售和營銷副總裁Allan Calamoneri說。“目前,這種技術應用在密度較低、封裝較小的芯片中,而且最近開始用在多芯片封裝中。這項技術通過了一些美國客戶的認證,但目前的大批量生產只局限在中國客戶上。”

下一步怎么走?目前的扇出式封裝都是將芯片封裝在200mm或300mm晶圓上。在研發層面,一些公司正在開發面板級扇出式封裝技術,它是在一個大的方形面板上封裝芯片。這個技術的初衷是在單位面積上處理更多的芯片,理論上可以將成本降低20%。

ASE-Deca、Nepes和三星公司等正在開發面板級扇出。目標上市時間為2018年和2019年,據稱,面板級別的扇出封裝技術能夠實現更便宜的低密度產品。

但是,就目前來看,面板級封裝技術難以掌握,這個領域也沒有相關標準。“選擇的主要落腳點總是成本,”Yole的Azemar說。 “面板級封裝的出現可能改變封裝市場的未來。”

那么,從長遠來看,哪些低密度扇出技術將占上風?有些技術會繼續尋找市場入口,有些技術會繼續攻城拔寨,有些則淪為小眾產品。不過目前還不清楚哪種技術前景更好,盡管市場上出現了許多新的應用,但是是否每種技術都有生存空間,還很難確定。

電子發燒友App

電子發燒友App

評論