摘要 本文提供了在襯底表面上沉積碳化硅薄膜的方法。這些方法包括使用氣相碳硅烷前體,并且可以釆用等離子體增強(qiáng)原子層沉積工藝。該方法可以在低于600“C的溫度下進(jìn)行,例如在大約23丁和 大約200V之間

2022-02-07 14:01:26 898

898

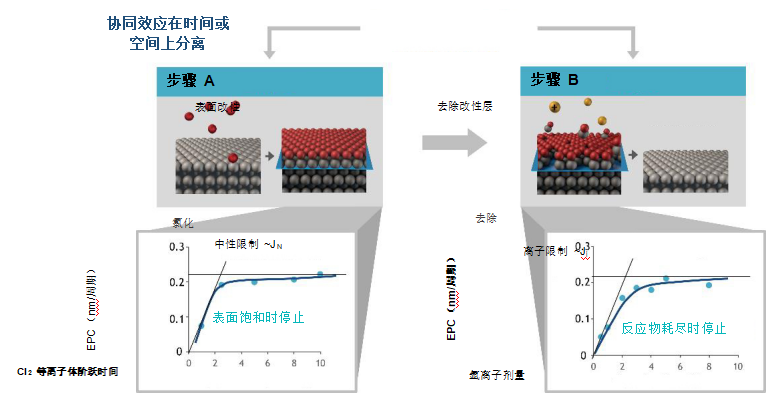

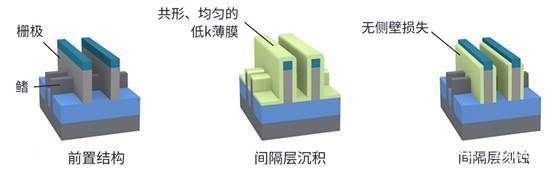

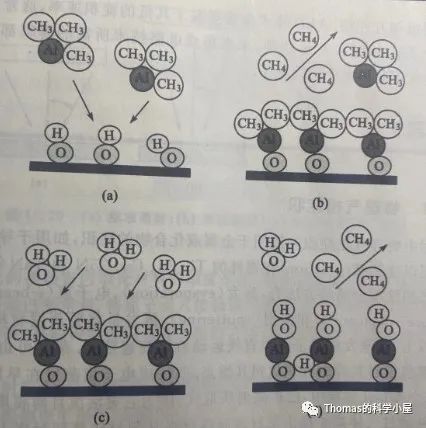

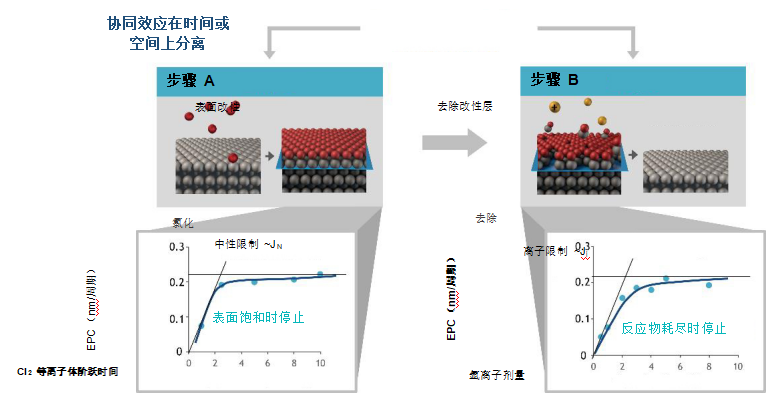

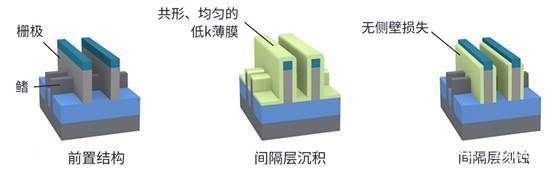

原子層刻蝕和沉積工藝利用自限性反應(yīng),提供原子級(jí)控制。 泛林集團(tuán)先進(jìn)技術(shù)發(fā)展事業(yè)部公司副總裁潘陽(yáng)博士 分享了他對(duì)這個(gè)話題的看法。 技術(shù)節(jié)點(diǎn)的每次進(jìn)步都要求對(duì)制造工藝變化進(jìn)行更嚴(yán)格的控制。最先進(jìn)的工藝

2021-02-08 10:53:00 6590

6590

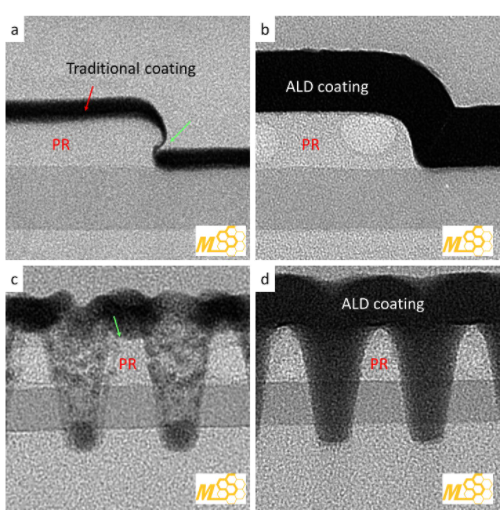

原子層沉積技術(shù)(Atomic layer deposition, ALD)近年在集成電路制程設(shè)備產(chǎn)業(yè)中受到相當(dāng)大的矚目,對(duì)比于其他在線鍍膜系統(tǒng),原子層沉積技術(shù)具有更優(yōu)越的特點(diǎn),如絕佳的鍍膜批覆性以及

2021-02-05 15:23:17 4743

4743

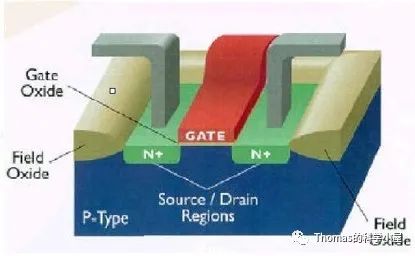

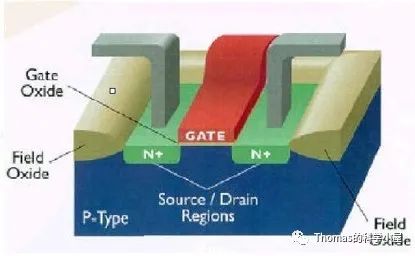

單晶圓系統(tǒng)也能進(jìn)行多晶硅沉積。這種沉積方法的好處之一在于能夠臨場(chǎng)進(jìn)行多晶硅和鎢硅化物沉積。DRAM芯片中通常使用由多晶硅-鈞硅化物形成的疊合型薄膜作為柵極、局部連線及單元連線。臨場(chǎng)多晶硅/硅化物沉積

2022-09-30 11:53:00 1235

1235 進(jìn)行MEMS制造的最基本需求是能夠沉積1到100微米之間的材料薄膜。NEMS的制造過程是基本一致的,膜沉積的測(cè)量范圍從幾納米到一微米。

2022-10-11 09:12:59 1193

1193 比較厚的金屬或合金薄膜[2]。應(yīng)用于MEMS器件中的微電鍍與以防腐和美觀為目的的普通電鍍?cè)?b class="flag-6" style="color: red">一樣,同屬于電化學(xué)范疇,除膜厚度不受限制外,它還具有生產(chǎn)周期短、設(shè)備簡(jiǎn)單、易于操作等優(yōu)點(diǎn),可以大大降低MEMS工藝薄膜沉積的成本,有利于產(chǎn)業(yè)化。

2019-07-04 08:14:01

的解決方案 泛林集團(tuán)通過其獨(dú)有的Durendal?工藝解決這一問題。該工藝可以產(chǎn)出優(yōu)質(zhì)、光滑的大型銅柱頂部表面,整個(gè)晶圓上的大型銅柱高度也非常均勻。整套Durendal?工藝可以在SABRE? 3D設(shè)備上

2020-07-07 11:04:42

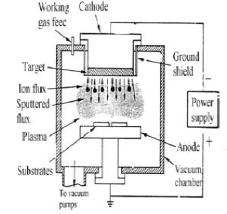

)110100100010-910-310-410-510-610-710-110-210-310-410-510110-110-210-3103102101 另一方面,在濺射工藝中,沉積速率一般比蒸發(fā)低2個(gè)數(shù)量級(jí),而壓力比蒸發(fā)高4個(gè)數(shù)量級(jí),因此所沉積的薄膜含有較高的氧。正是這個(gè)原因?yàn)R射不像蒸發(fā)那樣被認(rèn)為是一種清潔的薄膜制備方法

2016-12-08 11:08:43

。表面微加工是采用薄膜沉積、光刻以及刻蝕工藝,通過在犧牲層薄膜上沉積結(jié)構(gòu)層薄膜,然后去除犧牲層釋放結(jié)構(gòu)層實(shí)現(xiàn)可動(dòng)結(jié)構(gòu)。除了上述兩種微加工技術(shù)以外,MEMS制造還廣泛地使用多種特殊加工方法,其中常見的方法

2016-12-09 17:46:21

。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微納結(jié)構(gòu)的樣品制備,包括:TEM樣品制備、材料微觀截面截取

2017-06-29 14:16:04

。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微納結(jié)構(gòu)的樣品制備,包括:TEM樣品制備、材料微觀截面截取

2017-06-29 14:20:28

。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微納結(jié)構(gòu)的樣品制備,包括:TEM樣品制備、材料微觀截面截取

2017-06-29 14:24:02

。光刻膠的圖案通過蝕刻劑轉(zhuǎn)移到晶片上。沉積:各種材料的薄膜被施加在晶片上。為此,主要使用兩種工藝,物理氣相沉積 (PVD) 和化學(xué)氣相沉積 (CVD)。制作步驟:1.從空白晶圓開始2.自下而上構(gòu)建

2021-07-08 13:13:06

:MacEtch 是一種濕法蝕刻工藝,可提供對(duì)取向、長(zhǎng)度、形態(tài)等結(jié)構(gòu)參數(shù)的可控性,此外,它是一種制造極高縱橫比半導(dǎo)體納米結(jié)構(gòu)的簡(jiǎn)單且低成本的方法。 3 該工藝利用了在氧化劑(例如過氧化氫 (H2O2))和酸(例如

2021-07-06 09:33:58

的作用:1.通過減薄/研磨的方式對(duì)晶片襯底進(jìn)行減薄,改善芯片散熱效果。2.減薄到一定厚度有利于后期封裝工藝。氣相外延爐氣相外延是一種單晶薄層生長(zhǎng)方法。是化學(xué)氣相沉積的一種特殊方式,其生長(zhǎng)薄層的晶體結(jié)構(gòu)

2018-09-03 09:31:49

Down機(jī)、制程異常…等。工程人員解決以上所發(fā)生的問題,使這些"故障"消弭于無形謂之Trouble Shooting。241) Tungsten 鎢一種金屬。用以連接上下兩層金屬線

2020-02-17 12:20:00

10-3103102101 另一方面,在濺射工藝中,沉積速率一般比蒸發(fā)低2個(gè)數(shù)量級(jí),而壓力比蒸發(fā)高4個(gè)數(shù)量級(jí),因此所沉積的薄膜含有較高的氧。正是這個(gè)原因?yàn)R射不像蒸發(fā)那樣被認(rèn)為是一種清潔的薄膜制備

2016-06-17 14:40:12

推出Dual Beam FIB-SEM制樣業(yè)務(wù),并介紹Dual Beam FIB-SEM在材料科學(xué)領(lǐng)域的一些典型應(yīng)用,包括透射電鏡( TEM)樣品制備,材料微觀截面截取與觀察、樣品微觀刻蝕與沉積以及

2017-06-28 16:45:34

。 5.納米操縱手:用于超薄樣品(納米級(jí))固定轉(zhuǎn)移及精細(xì)加工。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微

2017-06-28 16:40:31

。 5.納米操縱手:用于超薄樣品(納米級(jí))固定轉(zhuǎn)移及精細(xì)加工。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微

2017-06-28 16:50:34

轉(zhuǎn)移及精細(xì)加工。 6.氣相沉積系統(tǒng)(GIS):FIB加工前為材料提供保護(hù)層,或用于材料精加工。 Dual Beam FIB-SEM制樣: FIB主要用于材料微納結(jié)構(gòu)的樣品制備,包括:TEM樣品制備、材料

2017-06-29 14:08:35

太陽(yáng)能電池可分為三類:?jiǎn)尉Ч杼?yáng)能電池、多晶硅太陽(yáng)能電池和薄膜太陽(yáng)能電池三種。非晶硅薄膜就是相對(duì)于單晶硅和多晶硅來說的。薄膜太陽(yáng)電池作為一種新型太陽(yáng)能電池,由于其原材料來源廣泛、生產(chǎn)成本低、便于大規(guī)模

2016-01-29 15:46:43

應(yīng)用材料((Applied Materials Inc., AMAT)公司日前宣布在Endura Volta CVD Cobalt系統(tǒng)中通過化學(xué)氣相沉積方法,在銅互連工藝中成功實(shí)現(xiàn)鈷薄膜沉積。這一

2014-07-12 17:17:04

材料,應(yīng)用于此工藝的材料黏度較高。如Loctite FP640l,其黏度在室溫時(shí)達(dá)300 000~ 600000Cps。局部填充工藝的特點(diǎn)是: ·底部填充材料被沉積在基板上元件角落處或四周

2018-09-06 16:40:03

`哪位了解LCVD激光氣相沉積設(shè)備,想買一臺(tái)用來做補(bǔ)線用。如圖,沉積出寬10um左右的金屬線。求大神指點(diǎn)!`

2014-01-17 10:36:02

)設(shè)備投資不大,廢物處理更簡(jiǎn)單,工藝成本比沉銅低;(3)藥水與流程相對(duì)減少,時(shí)效性可達(dá) 48H,更便于維護(hù)與管理。缺點(diǎn):(1)在導(dǎo)電性能方面,導(dǎo)電碳粉會(huì)弱于沉積銅層;(2)其適用性不如沉銅廣,因此,雖然

2022-06-10 16:05:21

相關(guān)專業(yè),5年以上相關(guān)工作經(jīng)驗(yàn);2.熟練掌握一種主流OLED光學(xué)、電學(xué)仿真軟件的使用;3.數(shù)量掌握一種力學(xué)仿真軟件。2、ALD工藝工程師崗位職責(zé):1. 負(fù)責(zé)原子層沉積設(shè)備評(píng)估,完成設(shè)備比對(duì)表及設(shè)備招標(biāo)

2016-12-16 11:45:29

沉積到PCB焊盤表面的一種工藝。這種方法通過在焊盤表面用銀( Ag )置換銅( Cu ),從而在其上沉積一層銀鍍層。

優(yōu)點(diǎn)與缺點(diǎn)并存,優(yōu)點(diǎn)是可焊性、平整度高,缺點(diǎn)是存儲(chǔ)要求高,易氧化。

沉金板

沉金

2023-12-12 13:35:04

請(qǐng)問一下8寸 原子層沉積設(shè)備ALD,單晶片。國(guó)內(nèi)設(shè)備大約在什么價(jià)位啊?

2023-06-16 11:12:27

,而且往往會(huì)充填到板厚度的100%以上。本章的網(wǎng)板設(shè)計(jì)部分將提供用于焊接定位孔的另一種可 行方法。 根據(jù)生產(chǎn)的特定組件,可使用不同的工藝步驟。最便利和最高成本效益的工藝是設(shè)計(jì)一個(gè)同時(shí)適合 SMC和異形

2018-11-22 11:01:02

采用濺射技術(shù), 對(duì)薄膜沉積的相關(guān)工藝參數(shù)進(jìn)行了優(yōu)化, 獲得了電阻溫度系數(shù)TCR≤±10×10- 6ö℃的錳銅薄膜。該項(xiàng)技術(shù)為錳銅傳感器的薄膜化奠定了基礎(chǔ), 同時(shí)也可用于制作錳銅薄膜

2009-06-27 09:32:16 19

19 用脈沖激光(Nd:YAG 激光)沉積技術(shù)在硅基上沉積富硅SiO2薄膜(SiOx,x<2),沉積時(shí)氧氣壓力分別為1.33,2.66,3.99,5.32,6.65,7.98Pa,膜的厚度約為300nm。隨后,在氬(Ar)氣中1000℃的溫度下對(duì)

2010-08-03 16:24:35 0

0 半導(dǎo)體制程之薄膜沉積

在半導(dǎo)體組件工業(yè)中,為了對(duì)所使用的材料賦與某種特性,在材料表面上常以各種方法形成被膜而加以使用,假如

2009-03-06 17:14:58 5558

5558

硅單晶(或多晶)薄膜的沉積

硅(Si)單晶薄膜是利用氣相外延(VPE)技術(shù),在一塊單晶Si 襯底上沿其原來的結(jié)晶軸方向,生長(zhǎng)一層導(dǎo)電類型

2009-03-09 13:23:41 6889

6889 PZT厚膜的電射流沉積研究_王大志

2017-03-19 18:58:18 0

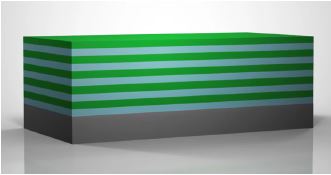

0 由于低溫沉積、薄膜純度以及絕佳覆蓋率等固有優(yōu)點(diǎn),ALD(原子層淀積)技術(shù)早從21世紀(jì)初即開始應(yīng)用于半導(dǎo)體加工制造。DRAM電容的高k介電質(zhì)沉積率先采用此技術(shù),但近來ALD在其它半導(dǎo)體工藝領(lǐng)域也已發(fā)展

2018-02-13 03:16:00 25903

25903 進(jìn)入投資。將來也會(huì)采用其他的物理沉積技術(shù)。”Crowley說,原子層沉積(atomic layer desposition,ALD)工藝更昂貴,但優(yōu)點(diǎn)是便于控制,且薄膜厚度更薄,厚度通常是納米級(jí)而不是微米級(jí)。

2018-11-09 08:57:11 5182

5182 在等離子增強(qiáng)化學(xué)氣相沉積法PECVD沉積 SiO2和 SiN掩蔽層過程中!分解等離子體中濃度較高的H原子使MG受主鈍化!同時(shí)在P-GaN材料表面發(fā)生反應(yīng)形成淺施主特性的N空位。

2018-12-17 08:00:00 17

17 CMOS器件是在硅材料上逐層制作而成的。雖然蝕刻和沉積是標(biāo)準(zhǔn)工藝,但它們主要使用光刻和等離子蝕刻在裸片上創(chuàng)建圖案。另一方面,MEMS是采用體硅加工工藝嵌入到硅中,或通過表面微加工技術(shù)在硅的頂部形成。

2020-09-01 11:21:32 3490

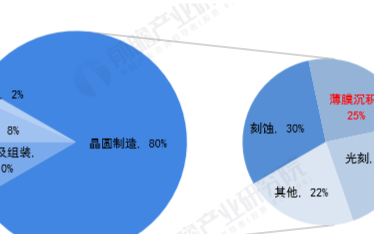

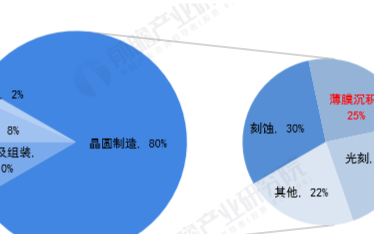

3490 沉積是半導(dǎo)體制造工藝中的一個(gè)非常重要的技術(shù),其是一連串涉及原子的吸附、吸附原子在表面擴(kuò)散及在適當(dāng)?shù)奈恢孟戮劢Y(jié),以漸漸形成薄膜并成長(zhǎng)的過程。在一個(gè)新晶圓投資建設(shè)中,晶圓廠80%的投資用于購(gòu)買設(shè)備。其中,薄膜沉積設(shè)備是晶圓制造的核心步驟之一,占據(jù)著約25%的比重。

2020-09-07 15:50:10 6019

6019

不久前,MEMS 蝕刻和表面涂層方面的領(lǐng)先企業(yè) memsstar 向《電子產(chǎn)品世界》介紹了 MEMS 與傳統(tǒng) CMOS 刻蝕與沉積工藝的關(guān)系,對(duì)中國(guó)本土 MEMS 制造工廠和實(shí)驗(yàn)室的建議

2022-12-13 11:42:00 1674

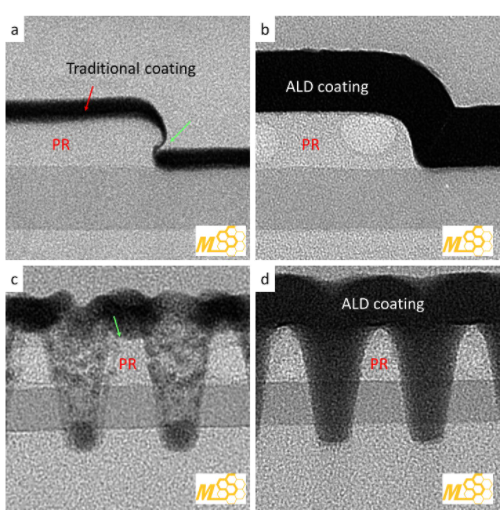

1674 )及化學(xué)氣相沉積(CVD)工藝已經(jīng)無法滿足極小尺寸下良好的臺(tái)階覆蓋要求,而控制納米級(jí)別厚度的高質(zhì)量超薄膜層制備也成為技術(shù)難點(diǎn)。 原子層沉積(ALD)是一種可以將物質(zhì)以單原子膜的形式,一層一層鍍?cè)诨妆砻娴南冗M(jìn)沉積技術(shù)。一個(gè)

2021-04-17 09:43:21 16607

16607

“國(guó)家智能傳感器創(chuàng)新中心和思銳智能都青睞‘智能’兩個(gè)字,都對(duì)超越摩爾產(chǎn)業(yè)情有獨(dú)鐘,雙方就以原子層沉積(ALD)設(shè)備及技術(shù)作為起點(diǎn),建立戰(zhàn)略合作伙伴關(guān)系,未來將在制造工藝設(shè)備的國(guó)產(chǎn)化,以及新材料、新工藝、新器件、新應(yīng)用等方面展開合作研究

2021-05-30 09:02:24 3898

3898

業(yè)界主流的薄膜沉積工藝主要有原子層沉積(ALD)、物理式真空鍍膜(PVD)和化學(xué)式真空鍍膜(CVD)等,其中ALD屬于CVD的一種,屬于當(dāng)下最先進(jìn)的薄膜沉積技術(shù)。

2021-09-03 11:12:42 1149

1149

薄膜集成電路是使用了薄膜工藝在藍(lán)寶石、石英玻璃、陶瓷、覆銅板基片上制作電路元、器件及其接線,最后進(jìn)行封裝而成的。 集成電路薄膜沉積工藝可以分為三類,為物理氣相沉積(PVD)、化學(xué)氣相沉積(CVD

2021-12-22 16:41:06 7760

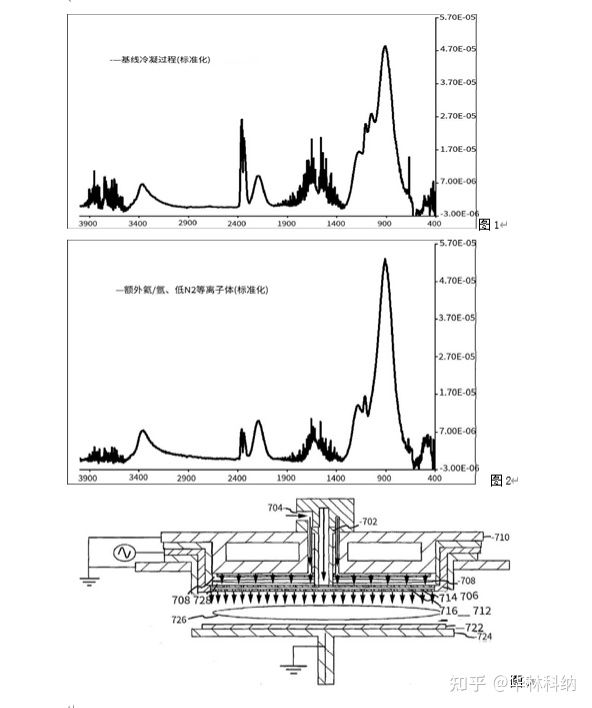

7760 摘要 丁二烯、氫和氬的三元混合物在平行板等離子體反應(yīng)器中沉積了類金剛石碳膜。這些薄膜的蝕刻量為02,cf4/02等離子體放電。推導(dǎo)出了沉積氣體混合物的組成與根據(jù)蝕刻和沉積速率定義的無量綱數(shù)(EN

2022-01-07 16:19:11 1028

1028

本文提供了在襯底表面上沉積碳化硅薄膜的方法。這些方法包括使用氣相碳硅烷前體,并且可以釆用等離子體增強(qiáng)原子層沉積工藝。該方法可以在低于600“C的溫度下進(jìn)行,例如在大約23丁和 大約200V之間

2022-02-15 11:11:14 3427

3427

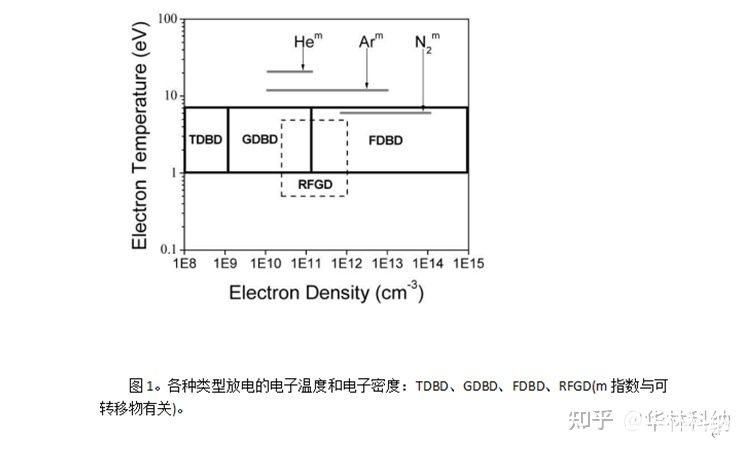

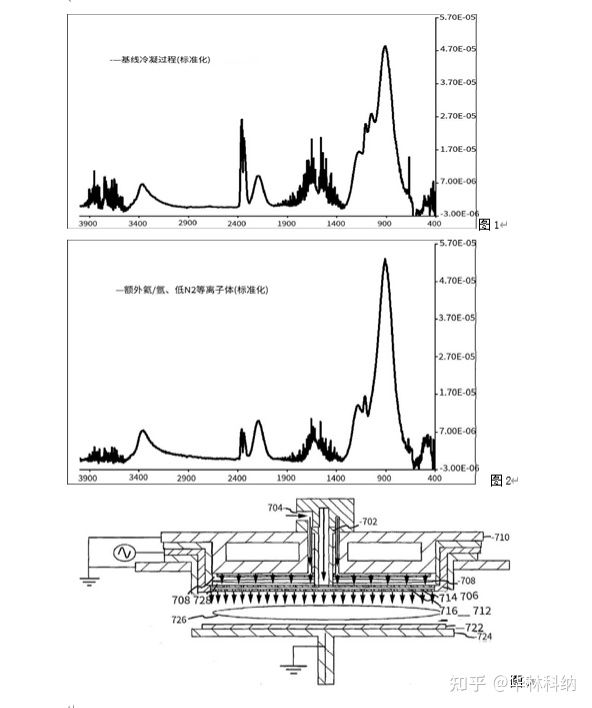

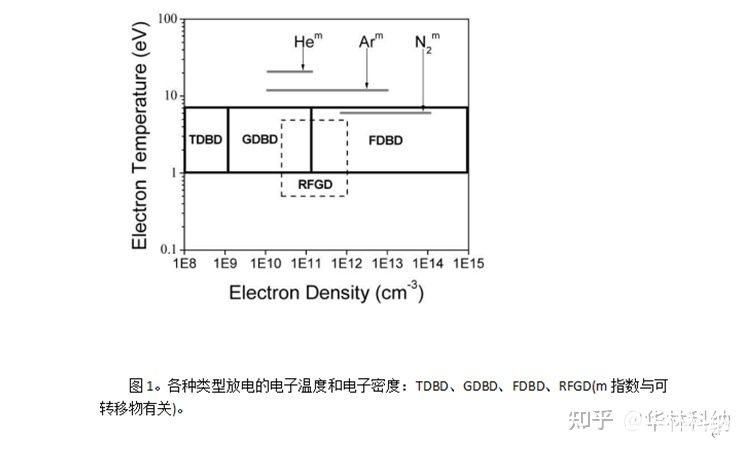

摘要 本文的目的是建立科技鎖的技術(shù)水平,必須打開科技鎖才能將直接大氣壓等離子體增強(qiáng)化學(xué)氣相沉積(AP-PECVD)視為工業(yè)應(yīng)用的可行選擇。總結(jié)了理解和優(yōu)化等離子體化學(xué)氣相沉積工藝的基本科學(xué)原理。回顧

2022-02-21 16:50:11 1900

1900

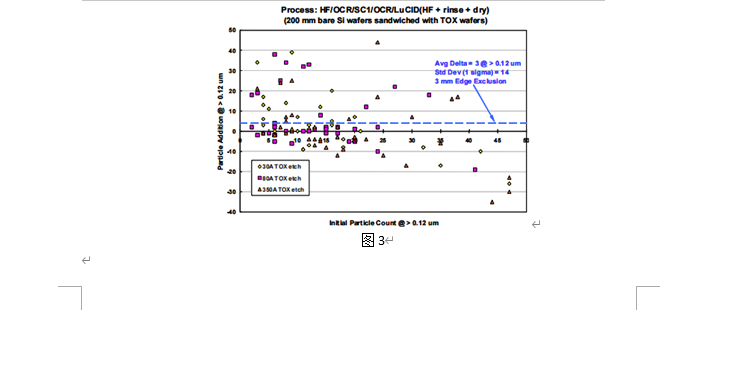

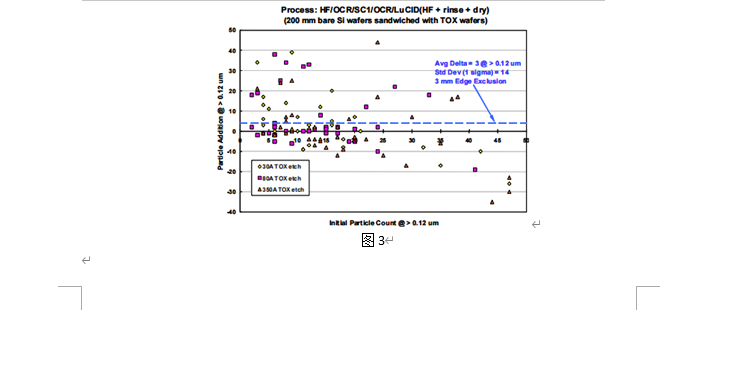

半導(dǎo)體晶片上的粒子沉積是集成電路制造中的一個(gè)重要問題。隨著集成電路的特征尺寸接近亞微米的尺寸,晶片上的顆粒沉積是造成產(chǎn)品損失的主要原因。我們開發(fā)了一種用于檢測(cè)半導(dǎo)體晶片上顆粒沉積的靈敏方法。該方法

2022-02-22 15:17:09 905

905

嵌入式硅鍺在最近的技術(shù)節(jié)點(diǎn)中被應(yīng)用于互補(bǔ)金屬氧化物半導(dǎo)體中,以提高器件性能并實(shí)現(xiàn)擴(kuò)展。本文發(fā)現(xiàn)硅鍺表面相對(duì)于溝道的位置對(duì)功率因數(shù)校正閾值電壓和器件可變性有顯著影響。因此,嵌入式硅鍺的凹槽蝕刻和沉積必須得到很好的控制。我們展示了器件對(duì)填充工藝的敏感性,并描述了用于優(yōu)化外延控制的前饋和反饋技術(shù)。

2022-02-23 10:08:14 2280

2280

Fraunhofer ISIT的PowderMEMS是一項(xiàng)新研發(fā)的創(chuàng)新技術(shù),用于在晶圓級(jí)上從多種材料中創(chuàng)建三維微結(jié)構(gòu)。該技術(shù)基于通過原子層沉積(ALD)工藝在空腔中將微米級(jí)粉末顆粒粘合在一起。

2022-03-17 09:46:23 2011

2011 本文研究了外延沉積前原位工藝清洗的效果,該過程包括使用溶解的臭氧來去除晶片表面的有機(jī)物,此外,該過程是在原位進(jìn)行的,沒有像傳統(tǒng)上那樣將晶圓從工藝轉(zhuǎn)移到?jīng)_洗罐。結(jié)果表明,與不使用溶解臭氧作為表面處理

2022-04-12 13:25:49 559

559

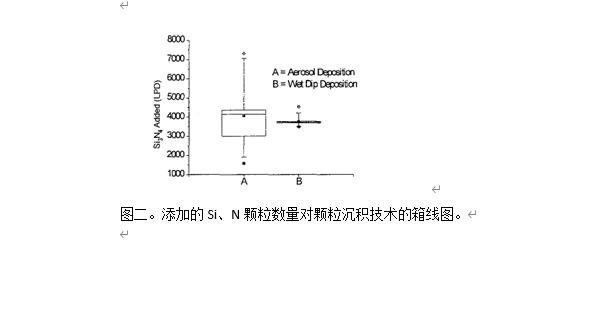

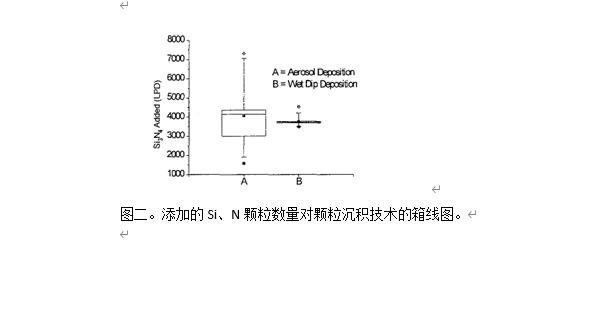

評(píng)估各種清洗技術(shù)的典型方法是在晶片表面沉積氮化硅(Si,N4)顆粒,然后通過所需的清洗工藝處理晶片。國(guó)家半導(dǎo)體技術(shù)路線圖規(guī)定了從硅片上去除顆粒百分比的標(biāo)準(zhǔn)挑戰(zhàn),該挑戰(zhàn)基于添加到硅片上的“>

2022-05-25 17:11:38 1242

1242

薄膜沉積設(shè)備介紹

2022-06-22 15:22:17 10

10 ALD是Atomic Layer Deposition(原子層沉積)的縮寫,是通過重復(fù)進(jìn)行材料供應(yīng)(前體)和排氣,利用與基板之間的表面反應(yīng),分步逐層沉積原子的成膜方式。

2022-10-11 10:04:00 1339

1339 在一起。然而,隨著芯片特征變得更小,現(xiàn)有材料可能無法在所需厚度下實(shí)現(xiàn)相同性能,從而可能需要新的材料。 泛林集團(tuán)發(fā)明了一種名為 SPARC 的全新沉積技術(shù),用于制造具有改進(jìn)電絕緣性能的新型碳化硅薄膜。重要的是,它可以沉積超薄層,

2022-10-14 17:12:59 505

505

盛美半導(dǎo)體設(shè)備(上海)股份有限公司對(duì)其300mm Ultra Fn立式爐干法工藝平臺(tái)進(jìn)行了功能擴(kuò)展,研發(fā)出新型Ultra Fn A立式爐設(shè)備。該設(shè)備的熱原子層沉積(ALD)功能豐富了盛美上海立式爐系列設(shè)備的應(yīng)用。首臺(tái)Ultra Fn A立式爐設(shè)備已于9月底運(yùn)往中國(guó)一家先進(jìn)的邏輯制造商。

2022-11-01 09:18:15 1466

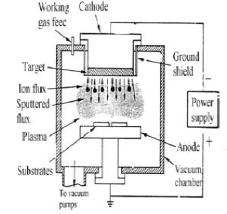

1466 物理氣相沉積(Physical Vapor Deposition, PVD)工藝是指采用物理方法,如真空蒸發(fā)、濺射 (Sputtering)鍍膜、離子體鍍膜和分子束外延等,在圓片表面形成薄膜。

2022-11-03 15:32:20 4187

4187 化學(xué)氣相沉積 (Chemical Vapor Deposition, CVD)是指不同分壓的多種氣相狀態(tài)反應(yīng)物在一定溫度和氣壓下發(fā)生化學(xué)反應(yīng),生成的固態(tài)物質(zhì)沉積在襯底材料表面,從而獲得所需薄膜的工藝技術(shù)。

2022-11-04 10:56:06 7439

7439 由于 ALD 技術(shù)逐層生長(zhǎng)薄膜的特點(diǎn),所以 ALD 薄膜具有極佳的合階覆蓋能力,以及極高的沉積均勻性和一致性,同時(shí)可以較好她控制其制備薄膜的厚度、成分和結(jié)構(gòu),因此被廣泛地應(yīng)用在微電子領(lǐng)域。

2022-11-07 10:43:16 5138

5138 Hannover(簡(jiǎn)稱:LZH)合作開發(fā)了一種新的空間ALD系統(tǒng),該系統(tǒng)實(shí)現(xiàn)“以前所未有的速度在復(fù)雜形狀的光學(xué)元件上涂覆薄膜層”。 Beneq的ALD系統(tǒng)(稱為C2R)可實(shí)現(xiàn)高達(dá)200 rpm的速度,沉積速率高達(dá)1 μm/h。LZH指出,ALD是一種自限性和各向同性工藝,每個(gè)周期產(chǎn)生大約1埃的層厚度。這

2022-12-22 16:30:24 2866

2866 現(xiàn)有的原子層沉積技術(shù)氮摻雜過程需要在氮?dú)獾入x子體的高溫條件下進(jìn)行,但是高溫環(huán)境下的薄膜生長(zhǎng)會(huì)引起電池正極和負(fù)極材料的相變和分解。雖然有研究指出低溫條件下在氨氣環(huán)境中可以實(shí)現(xiàn)氮摻雜的原子層沉積,但是同時(shí)會(huì)顯著增加氨氣尾氣處理的設(shè)備成本和維護(hù)難度以及安全風(fēng)險(xiǎn)。

2023-01-16 14:09:13 644

644 薄膜沉積是晶圓制造的三大核心步驟之- - ,薄膜的技術(shù)參數(shù)直接影響芯片性能。

半導(dǎo)體器件的不斷縮小對(duì)薄膜沉積工藝提出了更高要求,而ALD技術(shù)憑借沉積薄膜厚度的高度可控性、優(yōu)異的均勻性和三E維保形性,在半導(dǎo)體先進(jìn)制程應(yīng)用領(lǐng)域彰顯優(yōu)勢(shì)。

2023-02-16 14:36:54 555

555 濺射鍍膜(Vacuum Sputtering)基本原理是充氬(Ar)氣的真空條件下,使氬氣進(jìn)行輝光放電,這時(shí)氬(Ar)原子電離成氬離子(Ar+),氬離子在電場(chǎng)力的作用下加速轟擊以鍍料制作的陰極靶材,靶材會(huì)被濺射出來而沉積到工件表面。

2023-02-24 09:51:09 2595

2595 ALD技術(shù)是一種將物質(zhì)以單原子膜的形式逐層鍍?cè)诨妆砻娴姆椒ǎ軌驅(qū)崿F(xiàn)納米量級(jí)超薄膜的沉積。

2023-04-25 16:01:05 2442

2442

近日,中微半導(dǎo)體設(shè)備(上海)股份有限公司(以下簡(jiǎn)稱“中微公司”,上交所股票代碼:688012)推出自主研發(fā)的12英寸低壓化學(xué)氣相沉積(LPCVD)設(shè)備Preforma Uniflex CW。這是中微公司深耕高端微觀加工設(shè)備多年、在半導(dǎo)體薄膜沉積領(lǐng)域取得的新突破,也是實(shí)現(xiàn)公司業(yè)務(wù)多元化增長(zhǎng)的新動(dòng)能。

2023-05-17 17:08:41 831

831 。 PVD 沉積工藝在半導(dǎo)體制造中用于為各種邏輯器件和存儲(chǔ)器件制作超薄、超純金屬和過渡金屬氮化物薄膜。最常見的 PVD 應(yīng)用是鋁板和焊盤金屬化、鈦和氮化鈦襯墊層、阻擋層沉積和用于互連金屬化的銅阻擋層種子沉積。 PVD 薄膜沉積工藝需要一個(gè)高真空的平臺(tái),在

2023-05-26 16:36:51 1751

1751 在了解芯片沉積工藝之前,先要闡述下薄膜(thin film)的概念。薄膜材料是厚度介于單原子到幾毫米間的薄金屬或有機(jī)物層。

2023-06-08 11:00:12 2192

2192

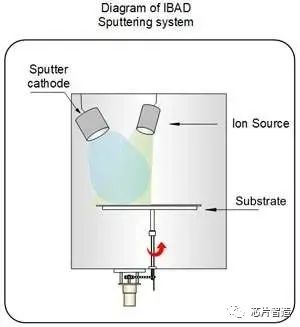

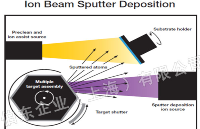

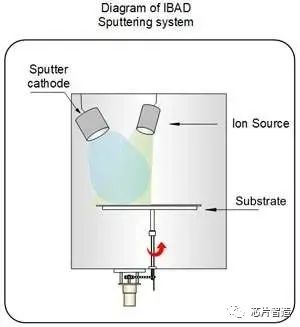

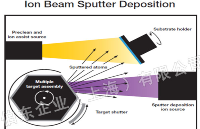

離子束輔助沉積 (IBAD) 是一種薄膜沉積技術(shù),可與濺射或熱蒸發(fā)工藝一起使用,以獲得具有出色工藝控制和精度的最高質(zhì)量薄膜。

2023-06-08 11:10:22 986

986

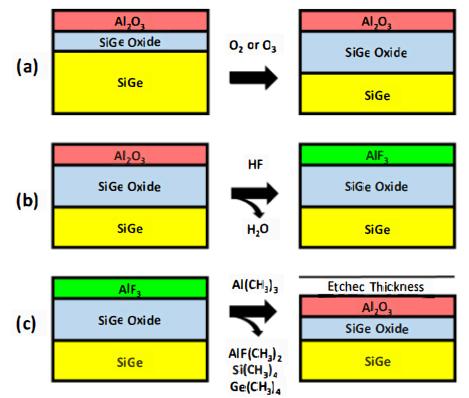

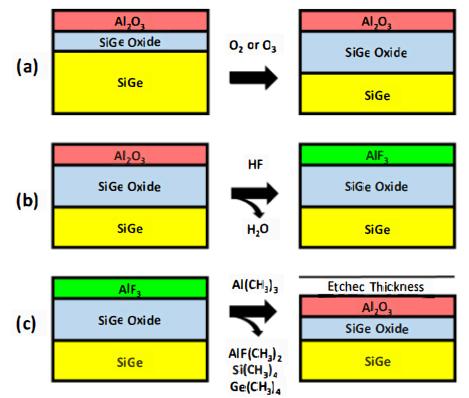

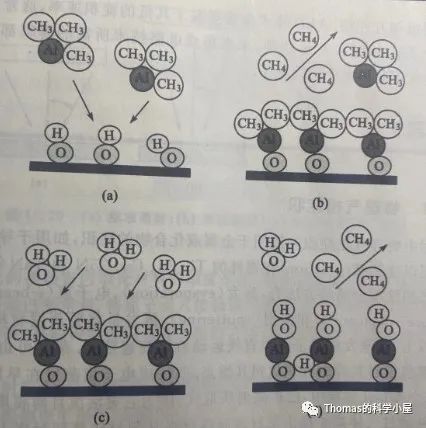

器件尺寸的不斷縮小促使半導(dǎo)體工業(yè)開發(fā)先進(jìn)的工藝技術(shù)。近年來,原子層沉積(ALD)和原子層蝕刻(ALE)已經(jīng)成為小型化的重要加工技術(shù)。ALD是一種沉積技術(shù),它基于連續(xù)的、自限性的表面反應(yīng)。ALE是一種蝕刻技術(shù),允許以逐層的方式從表面去除材料。ALE可以基于利用表面改性和去除步驟的等離子體或熱連續(xù)反應(yīng)。

2023-06-15 11:05:05 526

526

原子層沉積(Atomic layer deposition,ALD)是一種可以沉積單分子層薄膜的特殊的化學(xué)氣相沉積技術(shù)。

2023-06-15 16:19:21 2038

2038

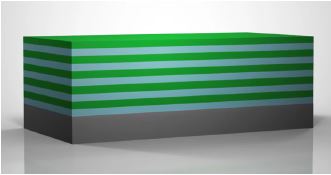

3D NAND 工藝通過堆疊存儲(chǔ)單元, 提供更高的比特密度, 上海伯東日本 Atonarp Aston? 質(zhì)譜分析儀適用于先進(jìn)半導(dǎo)體工藝(如沉積和蝕刻)所需的定量氣體分析. 沉積應(yīng)用中: 實(shí)時(shí)過程

2023-06-21 10:09:13 197

197

韞茂科技成立于2018年,致力于成為平臺(tái)形態(tài)的納米級(jí)薄膜沉積設(shè)備制造企業(yè)。目前擁有ald原子層沉積系統(tǒng)、pvd物理氣體沉積系統(tǒng)、cvd化學(xué)氣體沉積系統(tǒng)、uhv超高真空涂層設(shè)備等12種產(chǎn)品。

2023-06-28 10:41:03 540

540 近日,泛林集團(tuán)推出了Coronus DX產(chǎn)品,這是業(yè)界首個(gè)晶圓邊緣沉積解決方案,旨在更好地應(yīng)對(duì)下一代邏輯、3D NAND和先進(jìn)封裝應(yīng)用中的關(guān)鍵制造挑戰(zhàn)。隨著半導(dǎo)體芯片關(guān)鍵尺寸的不斷縮小,其制造變得

2023-06-29 10:08:27 650

650 在半導(dǎo)體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實(shí)也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨(dú)要強(qiáng)調(diào)“沉積”工藝呢?

2023-06-29 16:58:37 404

404

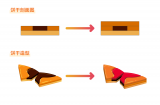

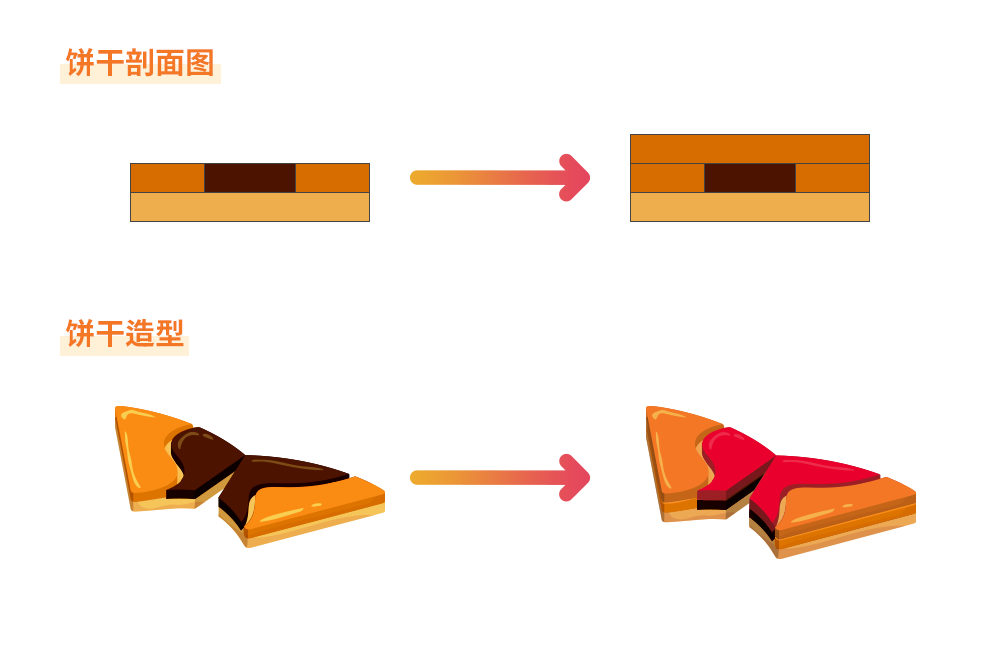

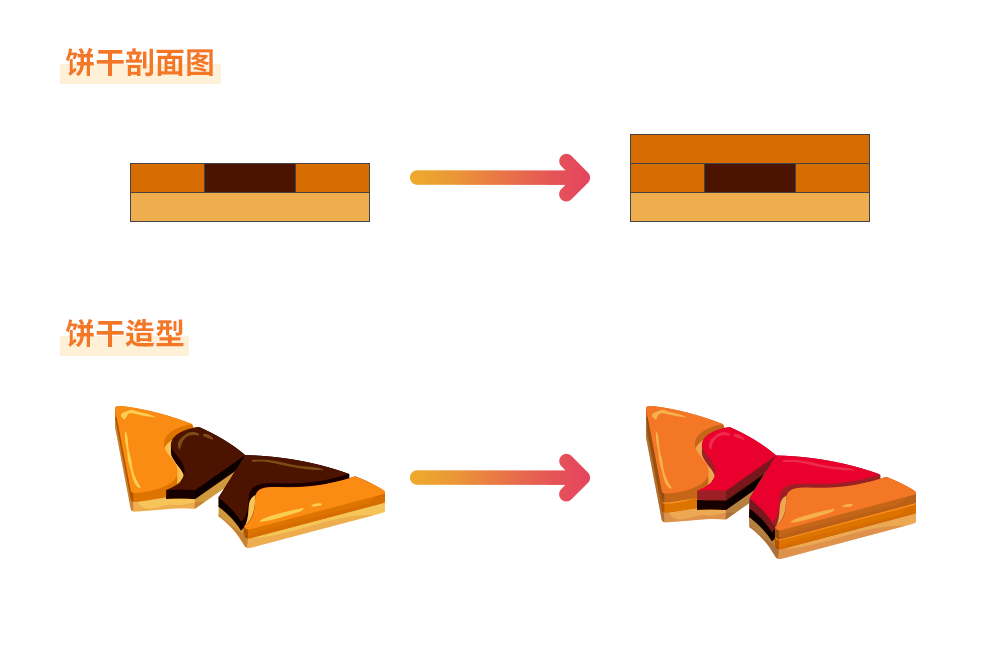

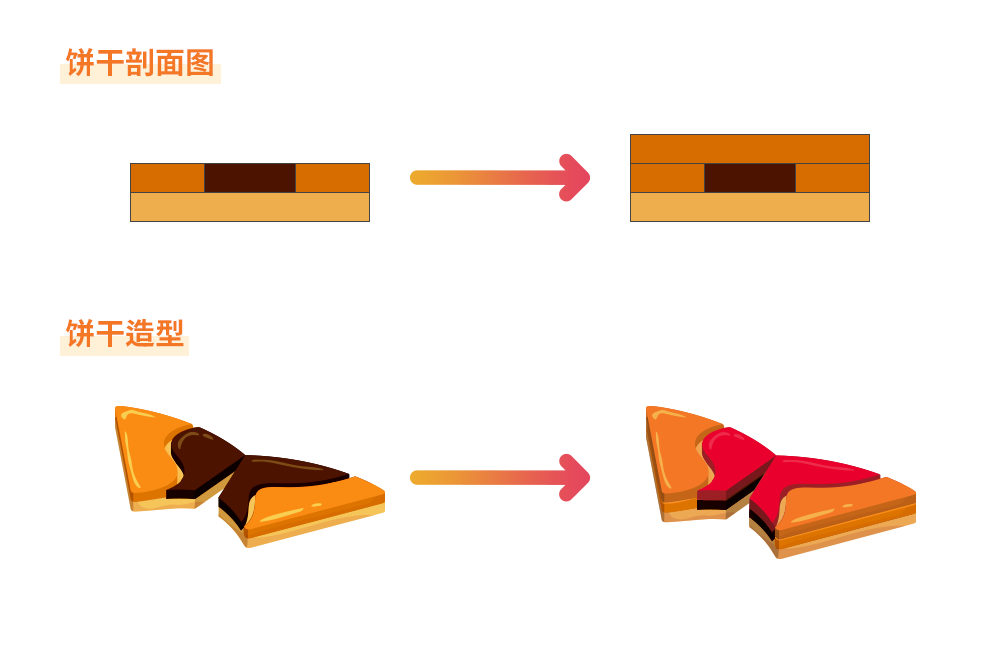

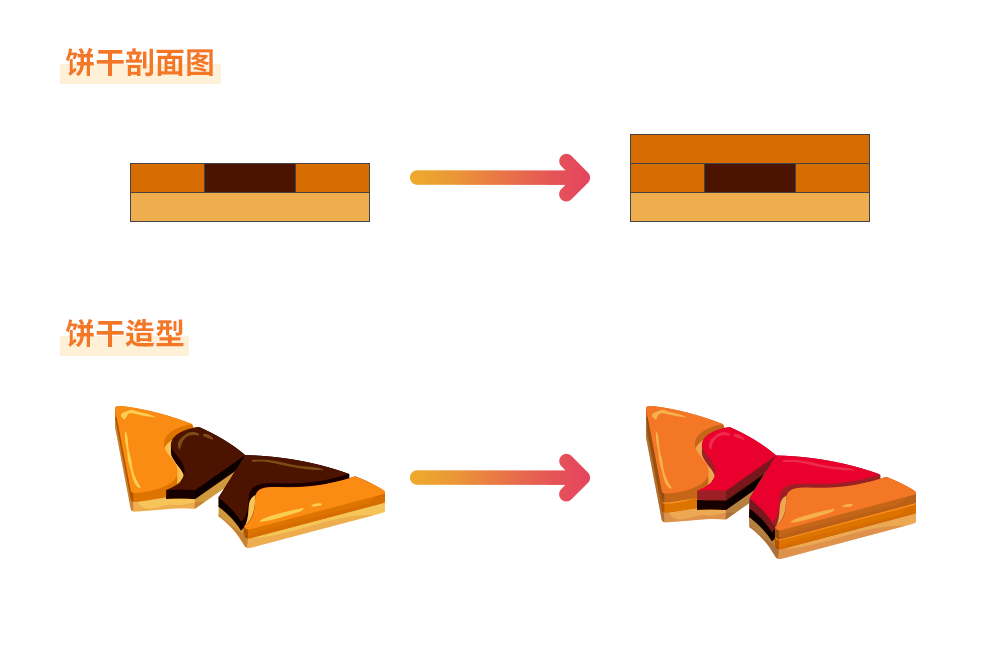

在前幾篇文章(點(diǎn)擊查看),我們一直在借用餅干烘焙過程來形象地說明半導(dǎo)體制程 。在上一篇我們說到,為制作巧克力夾心,需通過“刻蝕工藝”挖出餅干的中間部分,然后倒入巧克力糖漿,再蓋上一層餅干層。“倒入巧克力糖漿”和“蓋上餅干層”的過程在半導(dǎo)體制程中就相當(dāng)于“沉積工藝”。

2023-06-29 16:56:17 830

830

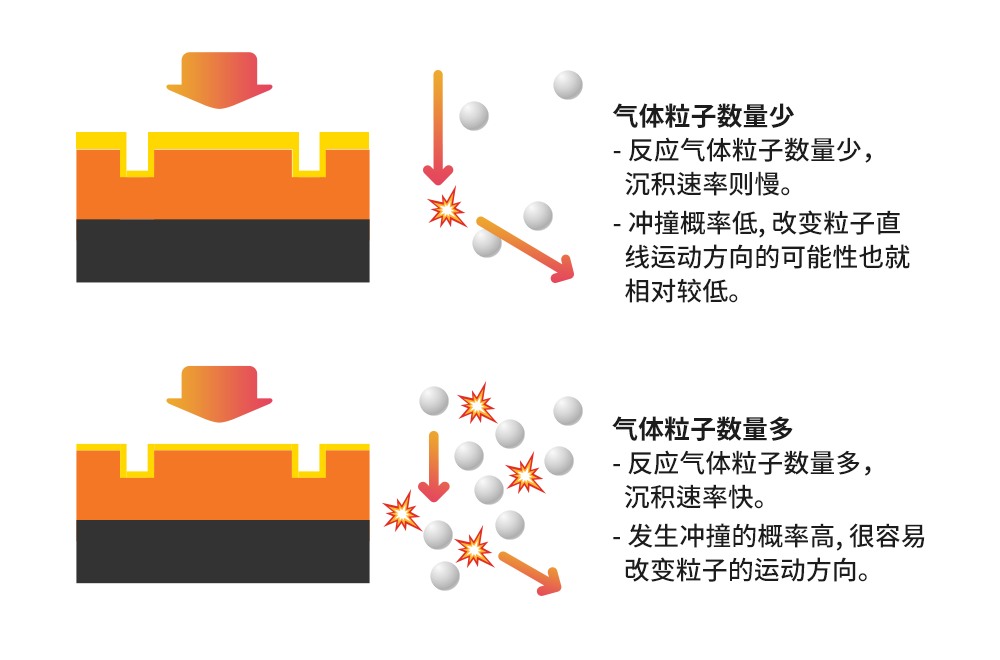

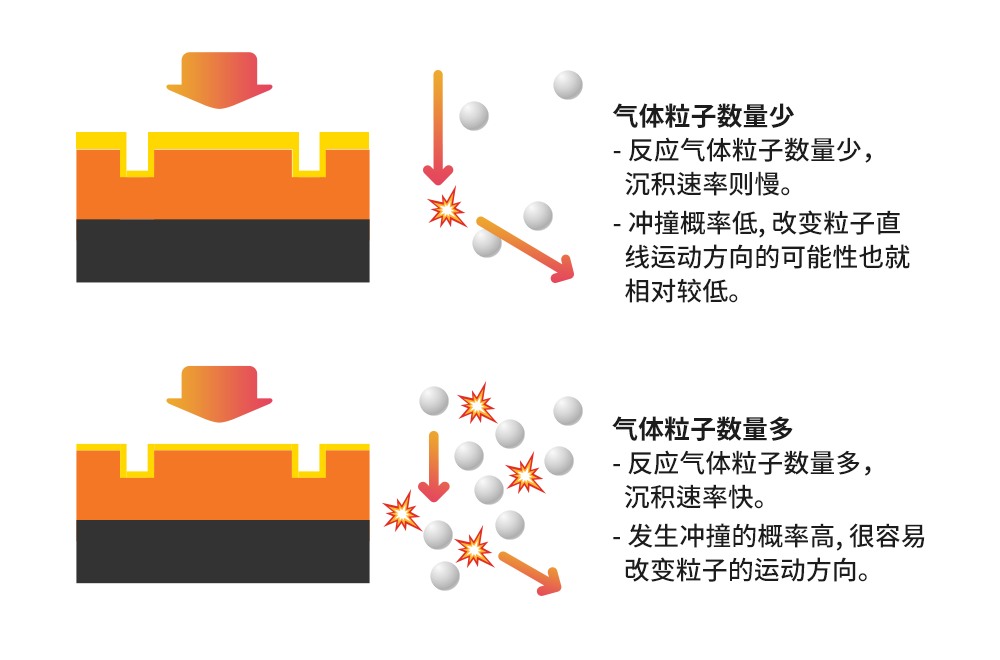

和在刻蝕工藝中一樣,半導(dǎo)體制造商在沉積過程中也會(huì)通過控制溫度、壓力等不同條件來把控膜層沉積的質(zhì)量。例如,降低壓強(qiáng),沉積速率就會(huì)放慢,但可以提高垂直方向的沉積質(zhì)量。因?yàn)椋瑝簭?qiáng)低表明設(shè)備內(nèi)反應(yīng)氣體粒子

2023-07-02 11:36:40 1214

1214

近日,泛林集團(tuán) (Nasdaq: LRCX) 推出了Coronus DX產(chǎn)品,這是業(yè)界首個(gè)晶圓邊緣沉積解決方案,旨在更好地應(yīng)對(duì)下一代邏輯、3D NAND和先進(jìn)封裝應(yīng)用中的關(guān)鍵制造挑戰(zhàn)。隨著半導(dǎo)體芯片

2023-07-05 00:39:29 422

422 薄膜沉積是指在基底上沉積特定材料形成薄膜,使之具有光學(xué)、電學(xué)等方面的特殊性能。

2023-07-13 09:10:48 7776

7776

該研究首次應(yīng)用紫外光輔助原子層沉積(UV-ALD)技術(shù)于石墨烯表面,并展示了利用UV-ALD沉積Al2O3薄膜在石墨烯場(chǎng)效應(yīng)晶體管(GFETs)中的應(yīng)用。在ALD過程中進(jìn)行5秒最佳紫外照射,導(dǎo)致在石墨烯表面上沉積出更加致密平滑的Al2O3薄膜

2023-08-16 15:52:37 282

282

在半導(dǎo)體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實(shí)也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨(dú)要強(qiáng)調(diào)“沉積”工藝呢?

2023-08-17 15:33:27 370

370

上海伯東美國(guó) KRi 考夫曼品牌 RF 射頻離子源, 無需燈絲提供高能量, 低濃度的寬束離子束, 離子束轟擊濺射目標(biāo), 濺射的原子(分子)沉積在襯底上形成薄膜, IBSD 離子束濺射沉積 和 IBD 離子束沉積是其典型的應(yīng)用.

2023-05-25 10:18:34 501

501

由于異質(zhì)結(jié)電池不同于傳統(tǒng)的熱擴(kuò)散型晶體硅太陽(yáng)能電池,因此在完成對(duì)其發(fā)射極以及BSF的注入后,下一個(gè)步驟就是在異質(zhì)結(jié)電池的正反面沉積ITO薄膜,ITO薄膜能夠彌補(bǔ)異質(zhì)結(jié)電池在注入發(fā)射極后的低導(dǎo)電性

2023-09-21 08:36:22 407

407

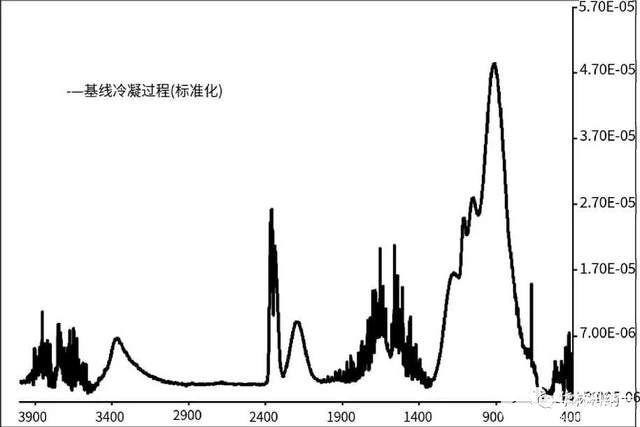

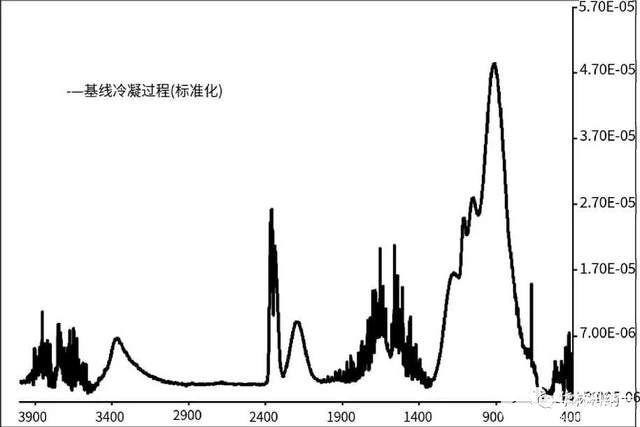

PECVD作為太陽(yáng)能電池生產(chǎn)中的一種工藝,對(duì)其性能的提升起著關(guān)鍵的作用。PECVD可以將氮化硅薄膜沉積在太陽(yáng)能電池片的表面,從而有效提高太陽(yáng)能電池的光電轉(zhuǎn)換率。但為了清晰客觀的檢測(cè)沉積后太陽(yáng)能電池

2023-09-27 08:35:49 1775

1775

在鈣鈦礦太陽(yáng)能電池的生產(chǎn)工藝中,ITO薄膜沉積是能夠提升鈣鈦礦太陽(yáng)能電池光電轉(zhuǎn)換率的關(guān)鍵步驟,其中,真空蒸鍍沉積技術(shù)可較為便捷的制備高純度、高質(zhì)量的ITO薄膜,是沉積工藝中的一項(xiàng)核心技術(shù)

2023-10-10 10:15:53 649

649

邑文電子科技有限公司副總經(jīng)理葉國(guó)光。葉總主要研究方向?yàn)榛衔锇雽?dǎo)體器件與ALD原子層沉積技術(shù),在LED,LD,HEMT與VCSEL的技術(shù)開發(fā)與ALD應(yīng)用于半導(dǎo)體器件的技術(shù)領(lǐng)域頗具權(quán)威。本報(bào)告主要從半導(dǎo)體

2023-10-18 11:33:44 2992

2992

牛津儀器(Oxford Instruments)推出PlasmaPro ASP系統(tǒng),這是其Atomfab?產(chǎn)品系列中的一款高速原子層沉積(ALD)研究系統(tǒng)。PlasmaPro ASP受益于新的專利

2023-10-23 16:20:07 487

487

半導(dǎo)體設(shè)備系列研究-薄膜沉積設(shè)備

2023-01-13 09:06:52 6

6 黎微明博士指出,傳統(tǒng)的PVD和CVD在鍍膜方面具有局限性。ALD技術(shù)特點(diǎn)在于可在復(fù)雜形貌上,完成原子層精度控制能力的高質(zhì)量薄膜沉積工藝。具體來看,ALD技術(shù)具有三維共形性,可廣泛適用于不同形狀的基底。

2023-11-02 17:27:05 435

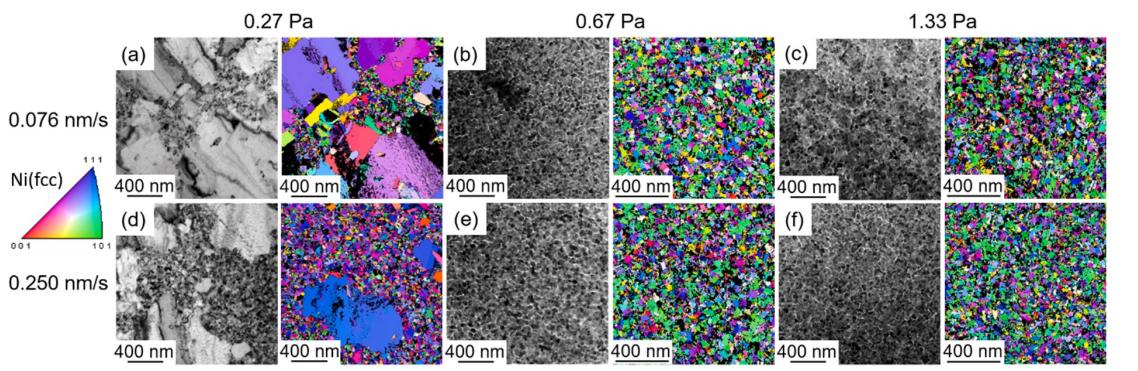

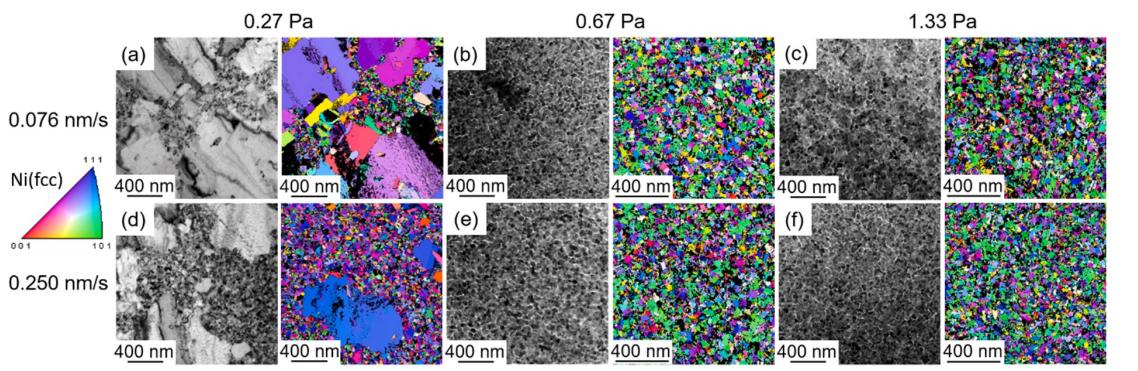

435 眾所周知,材料的宏觀性質(zhì),例如硬度、熱和電傳輸以及光學(xué)描述符與其微觀結(jié)構(gòu)特征相關(guān)聯(lián)。通過改變加工參數(shù),可以改變微結(jié)構(gòu),從而能夠控制這些性質(zhì)。在薄膜沉積的情況下,微結(jié)構(gòu)特征,例如顆粒尺寸和它們的顆粒

2023-11-22 10:20:59 214

214

半導(dǎo)體前端工藝(第五篇):沉積——“更小、更多”,微細(xì)化的關(guān)鍵

2023-11-27 16:48:42 217

217

薄膜沉積技術(shù)主要分為CVD和PVD兩個(gè)方向。 PVD主要用來沉積金屬及金屬化合物薄膜,分為蒸鍍和濺射兩大類,目前的主流工藝為濺射。CVD主要用于介質(zhì)/半導(dǎo)體薄膜,廣泛用于層間介質(zhì)層、柵氧化層、鈍化層等工藝。

2023-12-05 10:25:18 997

997 金屬柵極的沉積方法主要由HKMG的整合工藝決定。為了獲得穩(wěn)定均勻的有效功函數(shù),兩種工藝都對(duì)薄膜厚度的均勻性要求較高。另外,先柵極的工藝對(duì)金屬薄膜沒有臺(tái)階覆蓋性的要求,但是后柵極工藝因?yàn)樾枰匦?b class="flag-6" style="color: red">填充原來多晶硅柵極的地方,因此對(duì)薄膜的臺(tái)階覆蓋 性及其均勻度要求較高。

2023-12-11 09:25:31 659

659

在太陽(yáng)能電池的薄膜沉積工藝中,具有化學(xué)氣相沉積(CVD)與物理氣相沉積(PVD)兩種薄膜沉積方法,電池廠商在沉積工藝中也需要根據(jù)太陽(yáng)能電池的具體問題進(jìn)行針對(duì)性選擇,并在完成薄膜沉積工藝后通過

2023-12-26 08:33:01 312

312

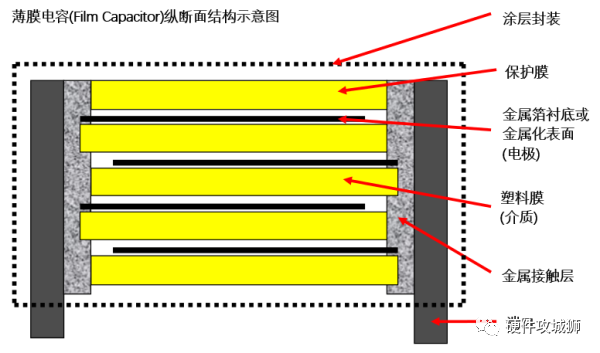

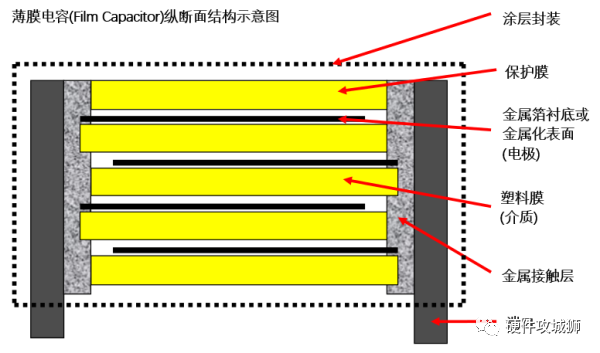

薄膜電容是一種常見的電子元件,其具有體積小、重量輕、容量大、可靠性高等優(yōu)點(diǎn),廣泛應(yīng)用于各種電子設(shè)備中。薄膜電容的工藝與結(jié)構(gòu)對(duì)其性能和可靠性有著重要的影響。本文將對(duì)薄膜電容的工藝與結(jié)構(gòu)進(jìn)行詳細(xì)的介紹

2024-01-10 15:41:54 444

444

優(yōu)化硅的形態(tài)與沉積方式是半導(dǎo)體和MEMS工藝的關(guān)鍵,LPCVD和APCVD為常見的硅沉積技術(shù)。

2024-01-22 09:32:15 433

433

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論