介紹

深度亞微米技術的進步,以及增加多種功能以降低成本,結合現(xiàn)有操作規(guī)模,意味著SoC的設計變得更加復雜。

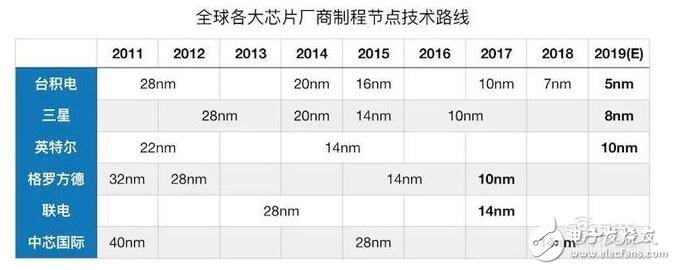

低于16納米工藝節(jié)點的最大驅(qū)動因素是這些先進節(jié)點更高的晶體管密度所帶來的功率下降和性能提高。然而,這樣做會給物理實現(xiàn)和時序/功率收斂帶來挑戰(zhàn)。特別是高速IP,如SerDes、DDR、PCIE在大型SoC中的集成,需要仔細的floor planning,以減少項目時間,并實現(xiàn)定時/功率簽收。在這篇文章中,我們將探討由于5納米技術以及SoC中新的額外功能而帶來的新挑戰(zhàn)。我們將展示解決floor planning和時序問題的方法,以減少物理實施的迭代。

方法

大型、復雜的IP集成的實施需要一種方法,以有效地完成 floorplansignoff 標準,并在后期階段防止大量的時序違規(guī)。

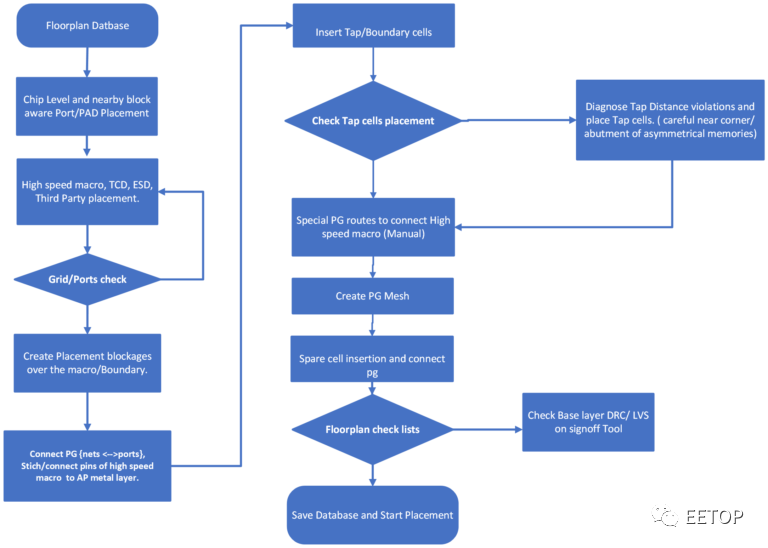

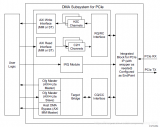

圖 1:Custom FloorplanMethodology

5nm 物理設計的挑戰(zhàn)

沿著從 SoC 到高級封裝技術(如 InFo/Feveros/X-Cube)的路徑,需要一種整體方法來同時解決項目的規(guī)劃、編輯和優(yōu)化環(huán)境問題。以及向后考慮決策路徑的影響。例如,通過在工藝早期迭代放置凸塊(bump )、PAD 和macros,可以縮短周轉(zhuǎn)時間。

另一個在流程需要早期考慮和規(guī)劃的是放置和布線之前的熱效應,以便通過設計出可能導致故障的熱點來提高產(chǎn)量和可靠性。例如,以高密度封裝的標準單元會產(chǎn)生熱點。這是因為,在14/16納米節(jié)點,使用三到四個鰭片來為每個柵極提供結構穩(wěn)定性,但在7納米以下,使用了兩個。這些都是較高的,以補償鰭片數(shù)量的減少,并仍然提供所需的加固。然而,應注意標準單元的放置,因為被電介質(zhì)(柵極氧化物)包圍的鰭片具有較差的導熱性,因此不能像預期的那樣進行散熱,從而產(chǎn)生一個熱點。因此,在早期階段進行功率分析(動態(tài)/靜態(tài))有助于防止在后期的功率signoff階段出現(xiàn)熱點意外。

最后,在較低的幾何形狀下,工藝和電壓變化強度更高。為了解決這個問題,由于噪聲和轉(zhuǎn)換要求,PT-ECO signoff通常需要對大型復雜塊進行 12 次以上的迭代。

集成高速模塊的挑戰(zhàn)

由于模擬團隊對硬IP的不斷改進,部分硬IP具有較高的變動性。這可以通過使用為不同設計階段量身定做的模型來解決,隨著我們接近流片,模型的復雜程度和完整程度會越來越高。在這個過程中,盡快獲得IP交付物清單對迅速和成功的整合至關重要。

最后,F(xiàn)loorplanning、DFT 集成、自定義時鐘樹和時序/功率 signoff 的設計復雜性都需要腳本知識和基本的 IP 理解來調(diào)整實施。

Floorplan挑戰(zhàn)

在最近的設計中,代工廠提供了一個multi-height庫,最初,很難通過網(wǎng)格檢查。問題是我們使用高效能庫來實現(xiàn)我們的設計,但是第三方 IP 位于高性能庫上。因此,兩種庫類型的放置必須在最小公倍數(shù) (LCM) 行上。問題是,我們正在使用一個高效的庫來實現(xiàn)我們的設計,但第三方IP是在高性能庫上。因此,這兩種庫類型必須放置在最小公共多行(LCM)上。

需要注意的是:

避免在模擬信號路徑的特殊區(qū)域插入分接單元和邊界單元。

Power Grid ?(PG) 連接對于多電源域設計以及模擬 VDD 以及第三方 IP VDD 非常重要。

連接 PG 網(wǎng)絡/引腳必須根據(jù)模擬團隊/第三方 IP 可交付成果定義的指南。

根據(jù)代工廠定義的功率鉗位實現(xiàn)規(guī)則連接 TCD/ESD IP。

插入備用單元后需要進行合法性檢查:網(wǎng)格檢查負責 IP 放置的合法性。

在芯片級集成塊時,集成檢查符合頂層floorplan DRC。

終端/端口放置檢查,因為這是初始設計集成中的一項重要檢查。

PG 設計規(guī)則檢查 (DRC),例如 PG Via 和電源條布線,加上宏到宏和宏到邊界間距規(guī)則檢查以避免 DRC。

Floorplan 規(guī)劃目標

這是為了有一個干凈的設計規(guī)則檢查 (DRC) 和布局與原理圖 (LVS) 設計,遵循設計實施指南以及時序/擁塞感知宏布局。

這些是如何通過改進floorplan來實現(xiàn)這一目標的階段。注意,此示例中使用了 Synopsys Fusion編譯器。

1、由于第三方IP有多個供應商,需要創(chuàng)建網(wǎng)格,因此生成網(wǎng)格提供了互連的統(tǒng)一性:

create_grid-type block -x_step $cell_site_pitch -y_step $cell_row_pitch -orientations “R0MX” Macro_wrapper set_block_grid_references-grid [get_grids Macro_wrapper ] -design Macro_Wrapper

set_snap_setting-class macro_Cell -snap block -user_grid Macro_wrapp

## 宏封裝器需要對齊到 7.752um、9.576um,它是單元站點 0.051 和單元行高 0.028 的倍數(shù)(1 個軌道距離)

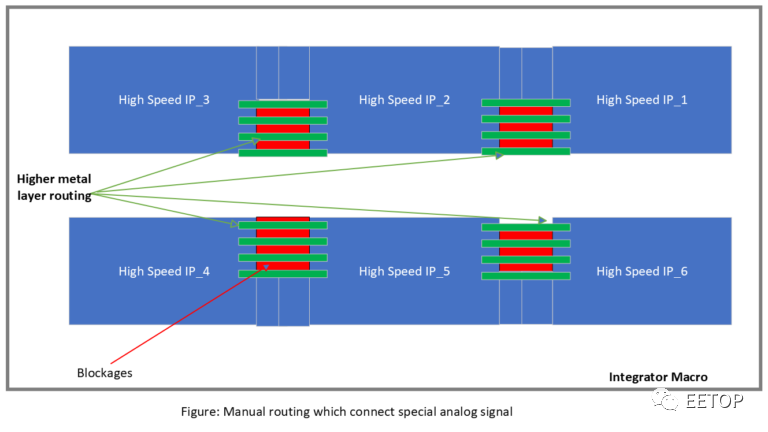

2、當您進行floorplan時,您需要手動對高速信號進行布線。您將需要通過使用在該區(qū)域上創(chuàng)建阻塞來避免任何布局或布線

· create_routing_blockage

· create_placement_blockage

例如:

·?create_placement_blockage -name $blk_name -boundary [get_attr [get_attr$blk_poly poly_rects] point_list]

· create_routing_blockage -name SNRG#${blk_name} -boundary [get_attr[get_attr $blk_poly poly_rects] point_list] -layers [get_layers -filterfull_name!~*G*] -zero_spacing

圖 2:高速宏上的塊和信號路由

3、Power Grid (PG) 連接要求 PG 網(wǎng)狀路由遵循實現(xiàn)定義的預連接命令。因此,我們需要連接模擬 PG 端口和 BUMP 連接以及數(shù)字電源/接地連接。

示例:

Connect_pg_net –net VDD [get_pins BUMPS_VDD_*/BUMP]

Connect_pg_net–net VSS [get_pins BUMPS_VSS_*/BUMP]

#特殊PG連接

foreach v“VDDAVSSA VDDM”{

Connect_pg_net–net $v [get_pins High_speed_IP_*/[string tolower $v]]

Connect_pg_net–net $v [get_pins Monitor*/[string tolower $v]]

}

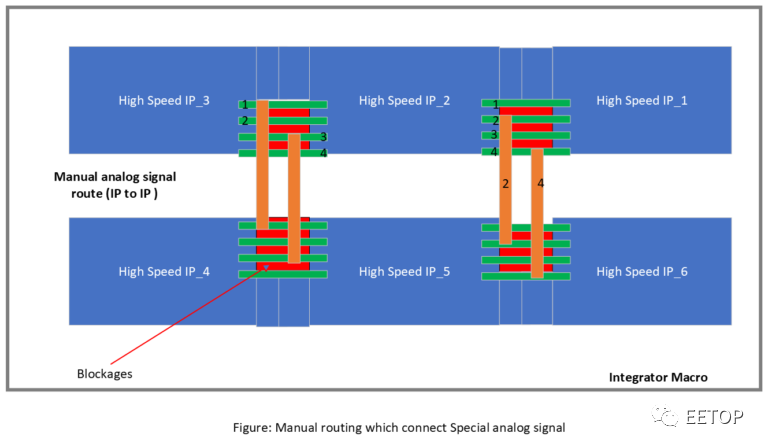

4、當您沒有足夠或不完整的庫交換格式 (LEF) 但必須檢查塊級和芯片級布局與原理圖 (LVS) 時,模擬團隊定義的在塊級連接的額外信號和特殊連接可能具有挑戰(zhàn)性。

例子:

圖 3:連接特殊模擬信號的手動路由

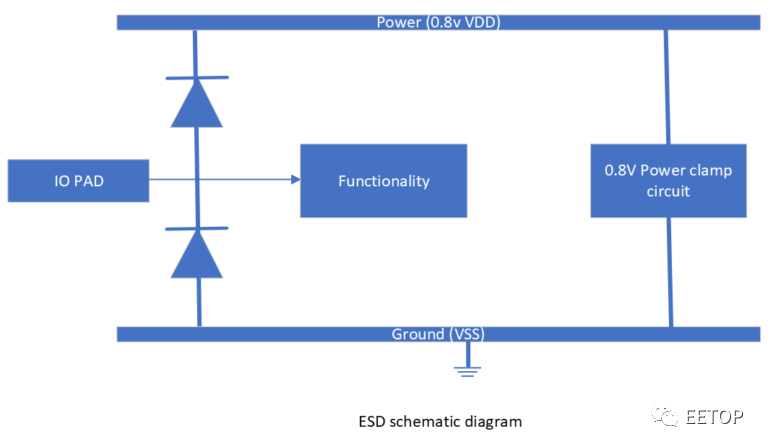

5、需要進行 ESD 單元和 TCD(Test-key Critical Dimension)檢查。需要靜電放電宏來保護高速模擬宏。TCD單元用于監(jiān)控最小線寬等關鍵尺寸。同時檢查單元的關鍵尺寸以確保制造過程中的布局均勻性以提高良率。

注意:我們將 ESD 單元放置在 Hard IP 附近,并提供與 Hard IP 所需的電壓相同的電壓以提高效率。

圖4 示意圖

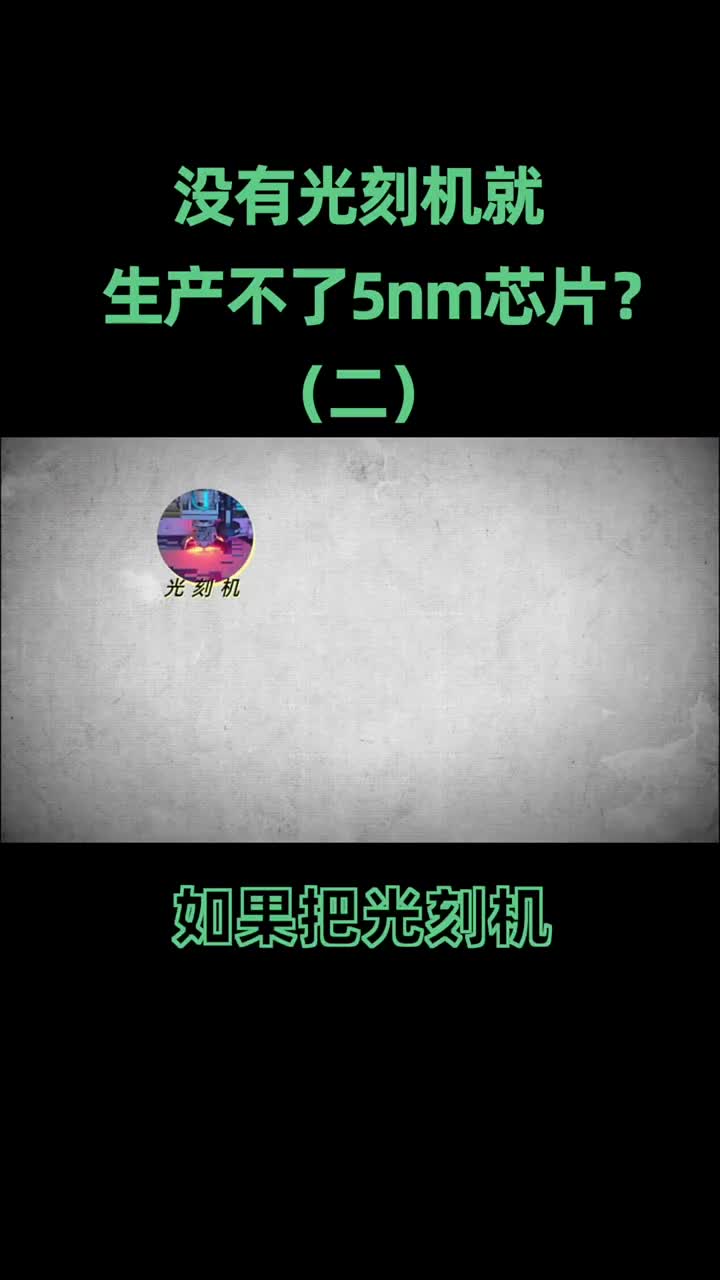

6、終端/端口放置檢查。這些是用于發(fā)現(xiàn)錯誤的平面布置圖的常見且簡單的檢查。

示例:要檢查的違規(guī)行為

7、Power Grid設計規(guī)則檢查:寫出 PG DRC 報告并將實施工具 PG DRC 與 ICV/Calibre 的平面圖signoff(規(guī)則甲板感知)DRC 進行比較。如果 DRC 違規(guī),例如非法重疊、寬度不足、最小金屬寬度最小金屬面積、非法形狀或最小金屬邊緣,請嘗試通過插入腳本調(diào)試 PG 網(wǎng)格腳本和手動 PG。

注意:在暫定signoff迭代期間進一步執(zhí)行下一步之前,應該清理 PG 上的 Shorts 和 Opens。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論