以前做業務的時候,經常問同事,集成電路的工程師到底關注晶圓或者器件的什么性質,哪些性質是通過實驗設備測得的,哪些可以是通過模擬仿真獲得的。同事就說去看WAT或者集成電路參數手冊。后來,一聽還要動腦子去找相關資料,就不愿意去干了,不知道如何以及從何處搜索資料。正好最近在研究集成電路制造工藝相關的資料,就看到了讓人心中一動的資料。

什么是WAT呢?WAT的英文全稱是Wafer Acceptance Test,WAT。中文有人翻譯為晶圓接受測試,有人翻譯為晶圓可接受測試等等翻譯。這里讓人想起一個事情,就是以前去新能源行業交流的時候,客戶總是問我們,為什么你們拿出來展示的資料都是英文版的。我們說我們做的幾個行業分別是半導體和鋰離子電池,很多半導體行業縮略語翻譯成中文的話,不太好翻譯,另外,就是我自己比較懶,也不太愿意去翻譯和折騰。這里我們接下來就不糾結于中文的翻譯了,咱們還是以WAT直接來說吧。

WAT定義

WAT是英文Wafer Acceptance Test的縮寫,意思是晶圓接受測試,業界也稱WAT為工藝控制監測(Process Control Monitor,PCM)[1]。WAT是在晶圓產品流片結束之后和品質檢驗之前,測量特定測試結構的電性參數。WAT的目的是通過測試晶圓上特定測試結構的電性參數,檢測每片晶圓產品的工藝情況,評估半導體制造過程的質量和穩定性,判斷晶圓產品是否符合該工藝技術平臺的電性規格要求。WAT數據可以作為晶圓產品交貨的質量憑證,另外WAT數據還可以反映生產線的實際生產情況,通過收集和分析WAT數據可以監測生產線的情況,也可以判斷生產線變化的趨勢,對可能發生的情況進行預警。

WHY?為什么要用WAT?

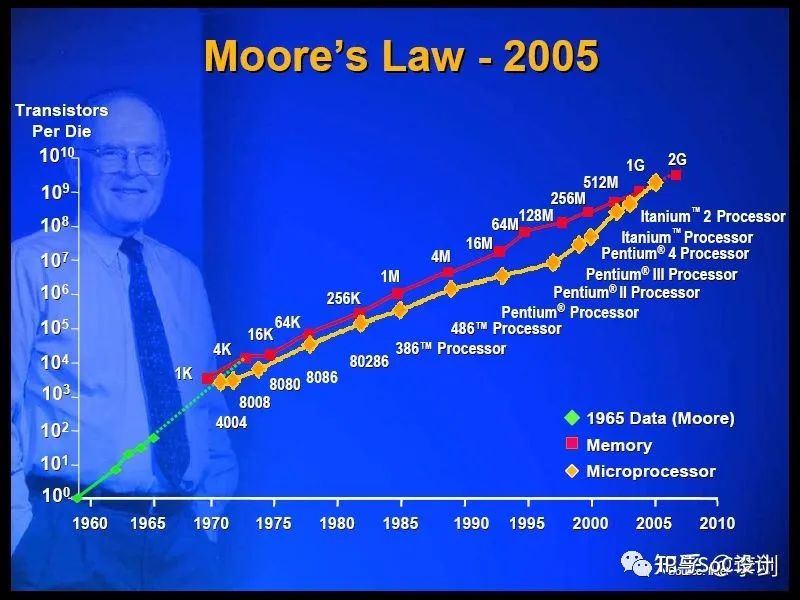

摩爾定律

集成電路的設計十分復雜,動輒使用數百萬到數十億個邏輯門數量(gate count),每一個邏輯門和其他器件的電性參數必須同時達到標準,否則芯片可能無法正常運作。一片晶圓通常有數十到數萬個芯片,保持制程的均一性相當重要。不但要監控關鍵的電性和物性,使其在整個晶圓的范圍內達到一定標準(SPEC);還得讓每一片生產的晶圓都達到這一標準。因此必須引入統計制程管制來完善質量監控[2]。

目前主流的生產系統是8英寸和12英寸[3]的工廠,12英寸晶圓較8英寸大了2.25倍,制程的控制難度也更大;然而工廠把大的晶圓使用在高階的制程,對控制的要求反而更高。由于工序相當繁復,從投片到產出可能包含近千個步驟,耗時一到三個月,必需使用制造流程(process flow)控制各階段制程的質量。

中國大尺寸硅片布局盤點

芯片在出廠前要進行各項檢測,以確認整個生產流程能達到上述要求。出廠檢測包含器件電性參數的量測(Wafer Acceptance Test,WAT),WAT量測包含大多數使用器件的參數,如電阻器的阻值、MOS的柵極氧化層電容值、MOSFET的特性等。這些電性參數可以反應制程工藝是否正常,而掌握工藝對電性的影響更是制程研發的關鍵。

WAT處于一個芯片制造的什么位置

首先,咱們得知道芯片的制造流程。關于芯片的制造工藝,大家都知道隨著先進技術節點的發展,目前芯片的制造工序已經達到上千道工序。而集成電路本身又是技術密集型和資金密集型的行業。所以,對于集成電路芯片制造的良率以及可靠性等內容,是集成電路制造廠以及相關產業鏈角色極為關注的內容。

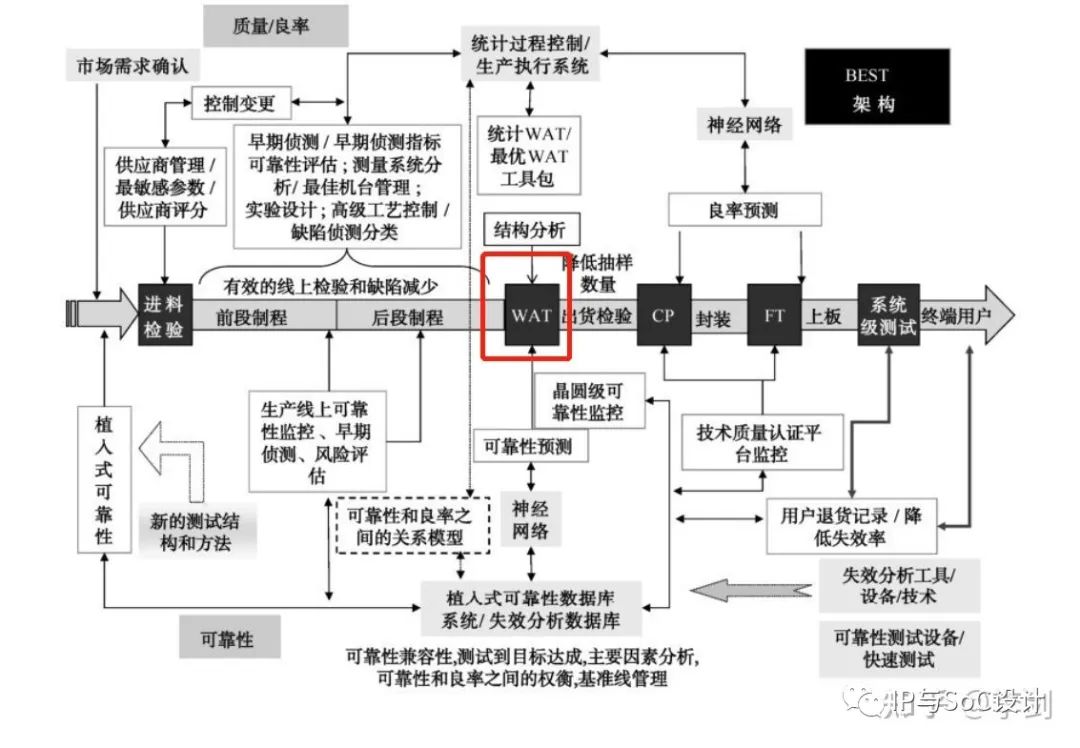

參考簡維廷等人編著的《半導體制造中的質量可靠性與創新》一書,咱們從可靠性以及良率的角度來看看WAT到底處于芯片制造流程中的哪一個環節。下圖即為從質量與可靠性管理的角度來繪制的芯片制造主要流程。

圖片根據《半導體制造中的質量可靠性與創新》一書插圖進行修改,紅色框線代表WAT所在位置

上圖中紅色框線所代表的內容即為WAT。根據上述內容即可以發現,芯片制造流程的主要干線為:原物料檢驗(Incoming Quality Assurance,IQA)、晶圓前段工藝(FEOL)監控、晶圓后段工藝(BEOL)監控、晶圓驗收測試(Wafer Acceptance Test,WAT)、晶圓出貨檢驗(Outgoing Quality Asurance,OQA)、晶圓良率測試(Chip Probing或Circuit Probing,CP)、芯片封裝工藝監控、芯片最終測試(Final Test,FT)、芯片上板工藝監控(On-board Test)、系統級測試(System Level Test,SLT)和終端用戶使用[4]。

主干線以上部分,是質量與良率(Yield)管理中需要用到的主要系統和方法;主干線以下部分,則是可靠性管理工作中所要用到的主要手法及管理要點。

上圖中的主干線就是將芯片的制造分割為這些主要的過程,并且每個過程都有輸出的參數,用于監控。主干線上下所列舉的,是在每一階段,質量與可靠性管理所需要用到的重要系統和方法。實際上,監控并不是越多越好、覆蓋越廣越好,一味地追求數據的完整性。因為任何生產都是需要考慮成本的,而監控的數據越多,系統越龐雜,所需要投入的初始成本和運營成本也將越高。質量與可靠性需要的是更合適、更先進的技術方法,能夠幫助企業提升產品質量與可靠性的同時,達到提高成本利潤率的目的。

WAT是晶圓制造的一個重要站點,它是用來檢測(也稱檢驗)已經制造完成的晶圓上,各種器件的各方面電學性能(Electrical Performance)是否滿足規格要求。如果某些重要參數沒有符合要求,晶圓將會被報廢,不會進入下一階段。

WAT簡介

WAT testkey

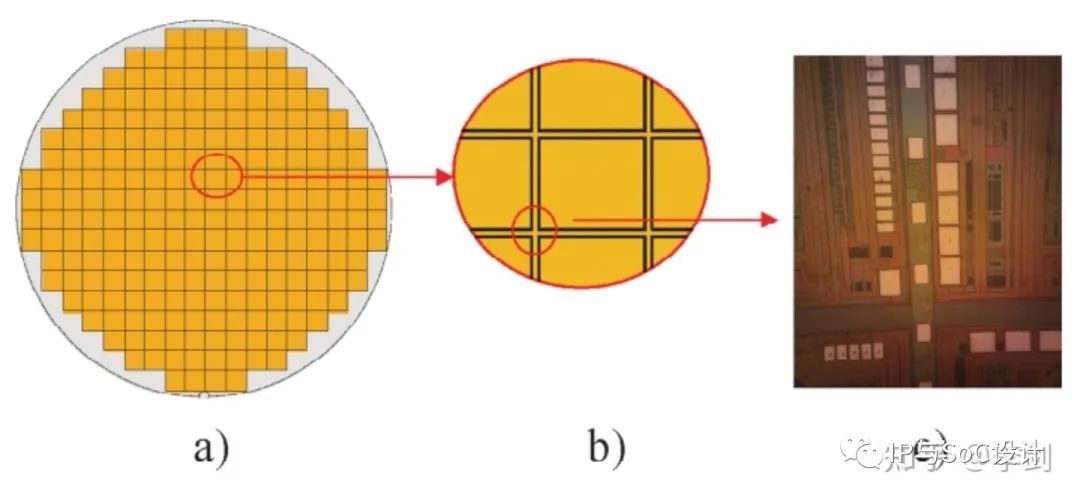

晶圓上用于收集WAT數據的測試結構稱為WAT測試結構(WAT testkey)[1]。WAT測試結構并不是設計在實際產品芯片內部的,因為設計在芯片內部要占用額外的芯片面積,而額外的芯片面積會增加芯片的成本,芯片代工廠僅僅把WAT測試結構設計在晶圓上芯片(die)之間的劃片槽(Scribe Line)。劃片槽的寬度可以從最小的60μm做到150μm,芯片代工廠依據芯片切割機器(Die Saw)的精度要求制定劃片槽的寬度設計要求,力求做到最小寬度及最小面積。

圖 劃片槽中的WAT測試結構

上圖所示為劃片槽中的WAT測試結構,圖a是整塊晶圓產品上的芯片,每一個小格子代表一顆芯片;圖b是放大后的圖形,可以看到芯片間的劃片槽;圖c是顯微鏡下的芯片劃片槽,白色的方塊區域是頂層金屬窗口,通常稱為封裝金屬窗口(Bonding PAD),WAT測試結構在PAD與PAD之間,很多不同的測試結構組成一組測試模組,芯片代工廠會給每組測試模組定義一個名稱,每一片晶圓會包含很多這樣的不同的WAT測試模組。

WAT測試在大多數情況下,都是利用晶圓切割道(Scribe Lane)上專門設計的測試結構(Test Pattern或Test Structure)完成的。通過這些測試結構的組合和測試結果的分析,我們基本上可以監控到晶圓制造的每一道工序。但是某些特殊的產品,如功率器件(Power IC),為了充分利用晶圓的面積,增加每片晶圓上晶粒的數目,會盡量壓縮切割道的面積,從而導致切割道太小,無法放置測試結構。當然,這類產品的制造工藝和電路設計一般都比較簡單,所以不需要浪費面積設計測試結構,而是可以通過直接測試晶粒來完成WAT。對它們來說,WAT測試項目和良率測試項目是相同的,所謂的WAT只是預先抽樣進行良率測試而已。有的時候甚至會選擇不做WAT,直接進行良率測試。在切割道上不放置WAT測試結構的另外一個好處,是可以降低晶圓封裝時的切割難度。對于采用90nm 以下先進工藝制造的產品,切割道上測試結構的設計會影響晶圓切割質量的現象,已經成為眾所周知的事情。在芯片與封裝交互作用的研究中,這也成為了一個重要的課題。液晶顯示器驅動芯片(Liquid Crystal Display Driver,LCD Driver)是另一類不會在切割道上放置測試結構的產品。因其形狀又長又窄,而又不能預先減薄晶圓,所以在整體考慮質量控制的策略之后,通常會選擇不在切割道上放置測試結構。其實,很多的案例也表明,復雜的切割道測試結構設計,不僅會給封裝切割帶來困難,同時也會給晶圓的制造帶來很多額外的風險。比如,因為負載效應(Loading Effect),切割道上大塊的銅金屬結構會導致附近晶粒邊緣的銅線磨不均勻,而容易出現短路(Short)或者斷路(Open)。所以在設計WAT測試結構的時候,要遵循一定的規則,同時也需要非常細心、謹慎[4]。

WAT測試結構通常包含該工藝技術平臺所有的有源器件、無源器件和特定的隔離結構。例如,有源器件包括MOS晶體管、寄生MOS晶體管、二極管和雙極型晶體管等,但是在標準的CMOS工藝技術中,僅僅把MOS晶體管和寄生MOS晶體管作為必要的WAT測試結構,而二極管和雙極型晶體管是非必要的WAT測試結構。無源器件包括方塊電阻、通孔接觸電阻、金屬導線電阻和電容等。隔離結構包括有源區(AA)之間的隔離,多晶硅之間的隔離和金屬之間的隔離。WAT參數是指有源器件、無源器件和隔離結構的電學特性參數[1]。

WAT測試是非常重要的,因為這是晶圓產品出貨前第一次經過一套完整的電學特性測試流程,通過WAT數據來檢驗晶圓產品是否符合該工藝技術平臺的電性規格要求,以及工藝制造過程是否存在異常。

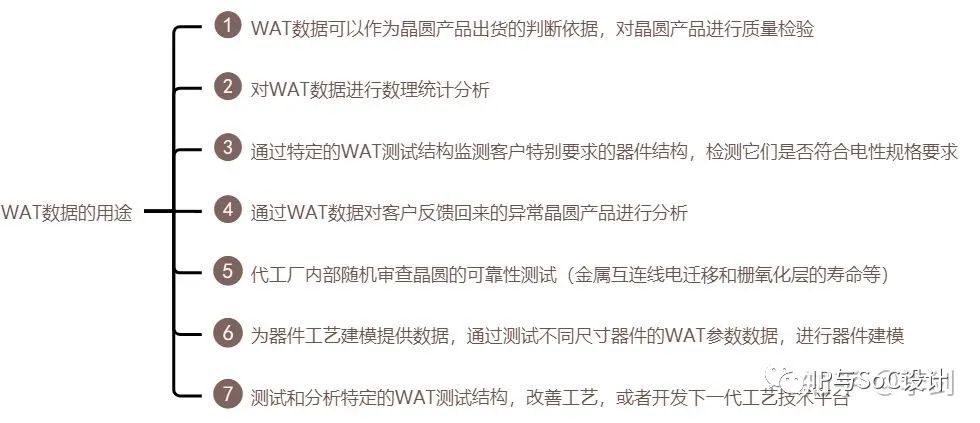

WAT數據有很多方面的用途,把它歸納為以下七大類:

WAT測試類型

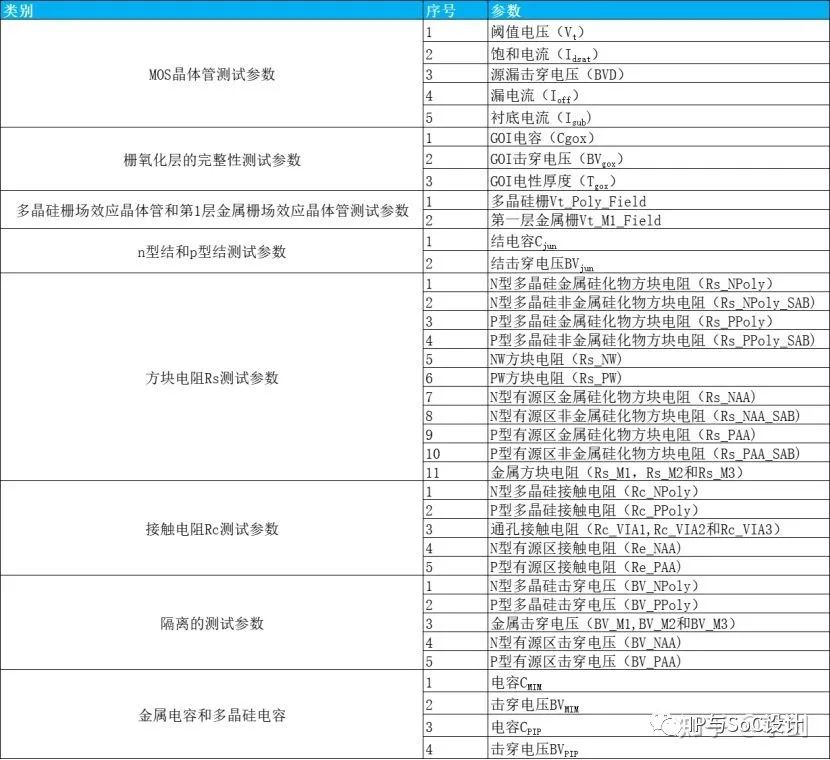

WAT的測試類型按照溫德通編著的《集成電路制造工藝與工程應用》可以分為如下8類。

WAT測試類型,根據溫德通編著《集成電路制造工藝與工程應用》一書文本類容繪制的思維導圖

上圖主要是以CMOS工藝技術平臺為例。具體測試項的部分內容如下表所示。

在參考資料中,作者不僅對要測試的內容作了綜述,同時還對影響相關測試的內容作了補充,比如影響MOS器件某一性能的影響因素都有什么,主要的工藝影響因素是什么,均作了相應的介紹。有興趣的朋友可以去看看。

參考資料:

1.溫德通編著.《集成電路制造工藝與工程應用》

2.張汝京等編著.《納米集成電路制造技術》

3.https://www.sohu.com/a/329973217_132567

4.簡維廷等著.《半導體制造中的質量可靠性與創新》

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論