摘? 要

SiC MOSFET器件的集成化、高頻化和高效化需求,對功率模塊封裝形式和工藝提出了更高的要求。本文中總結了近年來封裝形式的結構優化和技術創新,包括鍵合式功率模塊的金屬鍵合線長度、寬度和并聯數量對寄生電感的影響,直接覆銅(DBC)的陶瓷基板中陶瓷層的面積和高度對寄生電容的影響,以及采用疊層換流技術優化寄生參數等成果;綜述了雙面散熱結構的緩沖層厚度和形狀對散熱指標和應力與形變的影響;匯總了功率模塊常見失效機理和解決措施,為模塊的安全使用提供參考。最后探討了先進燒結銀技術的要求和關鍵問題,并展望了燒結封裝技術和材料的發展方向。

前? 言

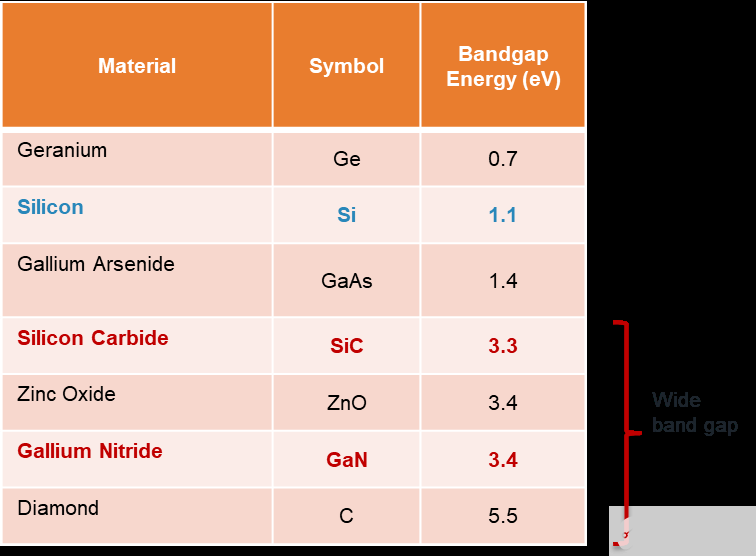

近幾十年來,以新發展起來的第3代寬禁帶功率半導體材料碳化硅(SiC)為基礎的功率半導體器件,憑借其優異的性能備受人們關注。SiC與第1代半導體材料硅(Si)、鍺(Ge)和第2代半導體材料砷化鎵(GaAs)、磷化鎵(GaP)、GaAsAl、GaAsP 等化合物相比,其禁帶寬度更寬,耐高溫特性更強,開關頻率更高,損耗更低,穩定性更好,被廣泛應用于替代硅基材料或硅基材料難以適應的應用場合。

(1)禁帶寬度更寬:SiC 的禁帶寬度比Si高3倍以上,使其能耐受的擊穿場強更高(臨界擊穿場強是Si基的10倍以上),故器件能承受的峰值電壓更高、能輸出的功率更大。相同電壓等級下,SiC功率半導體器件的漂移區可以做得更薄,可使整體功率模塊的尺寸更小,極大地提高了整個功率模塊的功率密度。另外,導通電阻R on 與擊穿場強的三次方成反比例關系,耐擊穿場強的能力高,導通電阻小,減小了器件開關過程中的導通損耗,提升了功率模塊的效率。

(2)耐溫更高:可以廣泛地應用于溫度超過600 ℃的高溫工況下,而Si基器件在600 ℃左右時,由于超過其耐熱能力而失去阻斷作用。碳化硅極大提高了功率器件的耐高溫特性。

(3)熱導率更高:SiC器件的熱導率比Si高3倍以上,高導熱率提升了器件和功率模塊的散熱能力,減低了對散熱系統的要求,有利于提高功率模塊的功率密度。

(4)載流子飽和速率更高:SiC與Si相比,其載流子飽和速率要高10倍以上,而SiC器件的開關頻率是Si基IGBT的5~10倍,增強了器件的高頻能力。SiC器件不僅導通電阻R on 小,而且開關過程損耗也低,提升了功率模塊的高頻性能。

(5)臨界位移能力更高:不僅SiC的臨界位移能力比Si高2倍以上,而且SiC器件對輻射的穩定性比Si基高10~100倍,SiC基器件具備更高的抗電磁沖擊和抗輻射破壞的能力。適合用于制作耐高溫抗輻射的大功率微波器件。

然而,現有的封裝技術大多都是沿用Si基器件的類似封裝,要充分發揮碳化硅的以上性能還有諸多關鍵問題亟待解決。

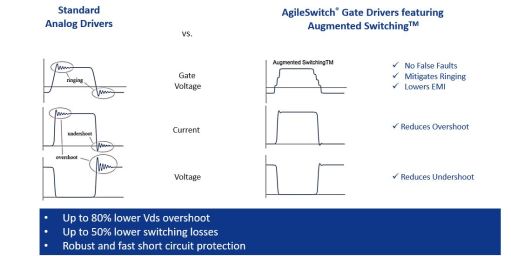

由于SiC器件的高頻特性,結電容小,柵極電荷低,開關速度快,開關過程中的電壓和電流的變化率極大,寄生電感在極大的 di/dt下,極易產生電壓過沖和振蕩現象,造成器件電壓應力、損耗的增加和電磁干擾問題。

關于在高溫、嚴寒等極端條件下可靠性急劇下降等問題,急需尋求適應不同工況的連接材料和封裝工藝,滿足不同封裝形式的熱特性要求。針對模塊內部互擾、多面散熱、大容量串并聯、制造成本和難度等問題,適當減少熱界面層數,縮減模塊體積,提升功率密度和多功能集成是未來的趨勢。采用先進散熱技術、加壓燒結工藝,設計功率半導體芯片一體化,優化多芯片布局等方式,起著一定的關鍵作用。

針對上述問題,國內外專家及其團隊研發不同封裝技術,用于提升模塊性能,降低雜散參數,增強高溫可靠性。

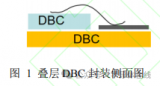

美國 Wolfspeed 公司研發出結溫超過 225 ℃的高溫SiC功率模塊,并將功率模塊的寄生電感降低到5 nH。美國GE公司的全球研究中心設計了一種疊層母線結構,構造與模塊重疊并聯的傳導路徑,使回路電感降至4. 5 nH。德國賽米控公司采用納米銀燒結和SKiN布線技術,研發出SiC功率模塊的高溫、低感封裝方法。德國英飛凌公司采用壓接連接技術,研制出高壓 SiC 功率模塊。德國Fraunholfer 研究所采用 3D 集成技術研制出高溫(200 ℃)、低感(≤1 nH)SiC功率模塊。瑞士ABB公司采用3D封裝布局,研制出大功率低感SiC功率模塊。瑞士ETH采用緊湊化設計,優化功率回路,研制出寄生電感≤1 nH 的低電感 SiC 功率模塊。日本尼桑公司基于雙層直接敷銅板(direct bonded copper,DBC)封裝,研制出低感 SiC 功率模塊,應用于車用電機控制器。

上述碳化硅的優良特性,只有通過模塊封裝布局的可靠性設計、封裝材料的選型、參數的優化、信號的高效和封裝工藝的改善,才能得以充分發揮。

本文中重點聚焦典型封裝結構下,低雜散參數、雙面散熱模塊下緩沖層的影響和功率模塊失效機理等關鍵技術內容的梳理總結,最后展望了未來加壓燒結封裝技術和材料的發展。

1 .模塊封裝形式

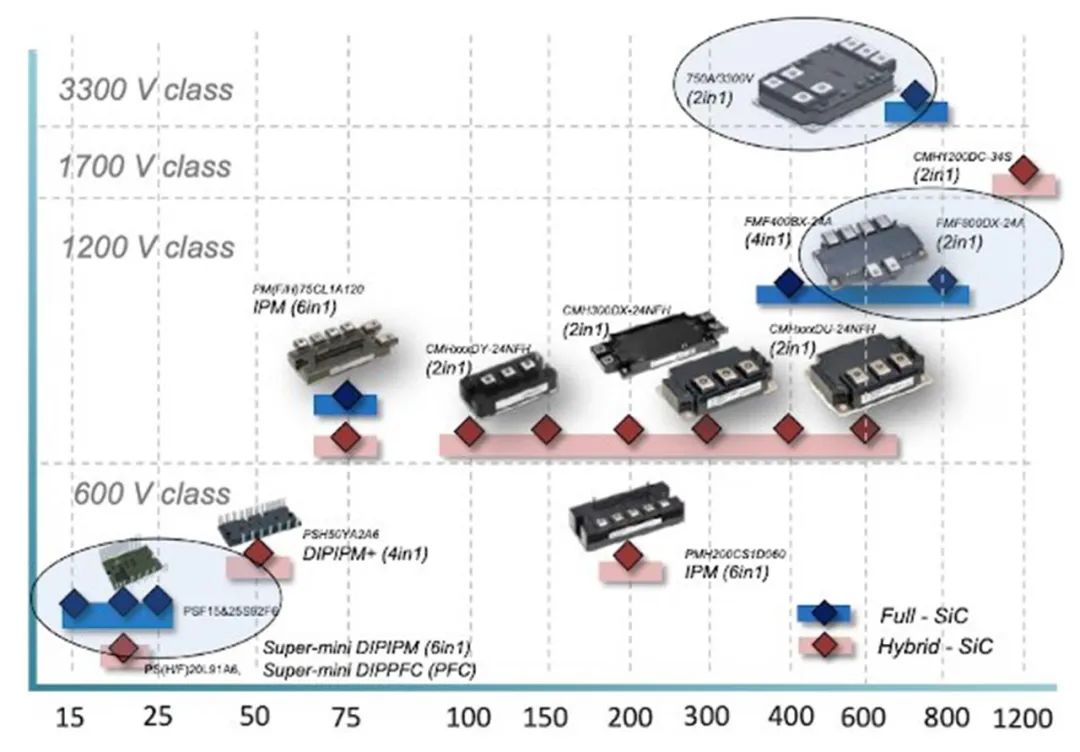

隨著新興戰略產業的發展對第3代寬禁帶功率半導體碳化硅材料和芯片的應用需求,國內外模塊封裝技術也得到迅速發展,追求低雜散參數、小尺寸的封裝技術成為封裝的密切關注點,國內外科研團隊和半導體產業設計了結構各異的高性能功率模塊,提升了SiC基控制器的性能。

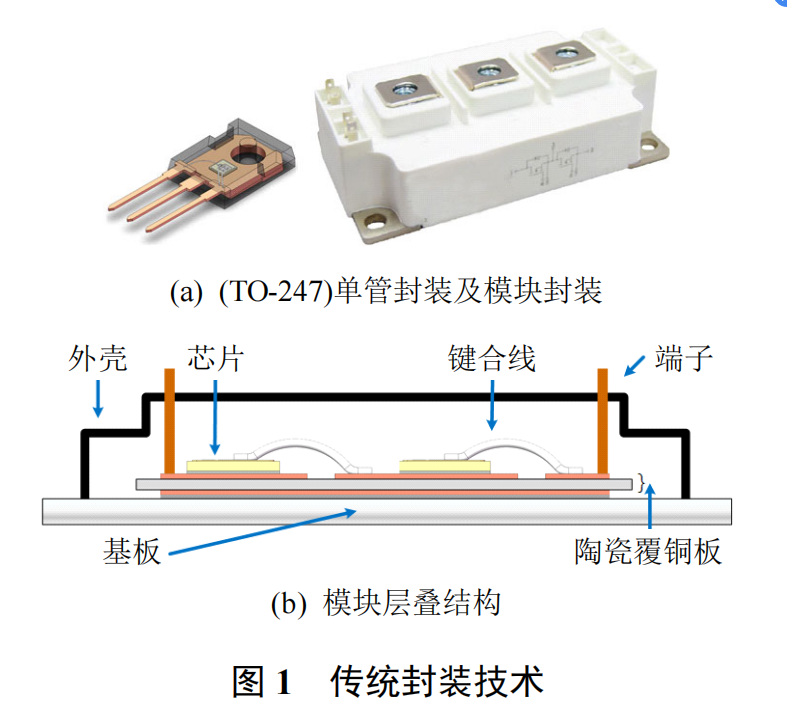

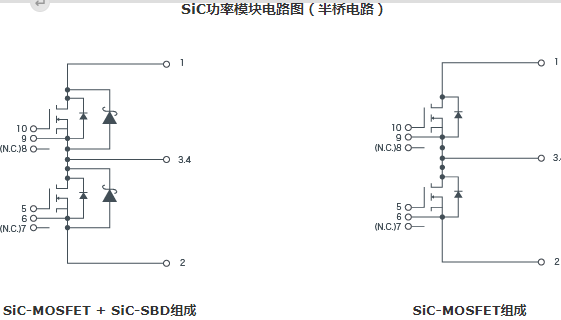

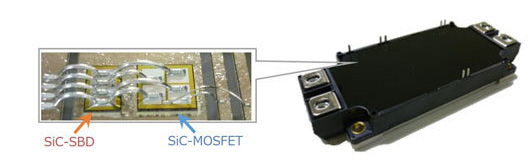

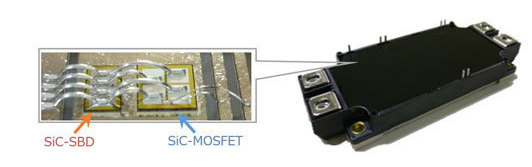

(1)傳統封裝:Wolfspeed、Rohm 和 Semikron 等制造商大多延用傳統Si基封裝方式,功率等級較低,含有金屬鍵合線,雜散電感較大。

(2)DBC+PCB 混合封裝:Cha 等和 Seal 等把DBC和PCB板進行整合,通過鍵合線連接芯片和PCB板,研創出DBC+PCB混合封裝。實現了直接在PCB層間控制換流回路,縮減換流路徑來減小寄生電感。

(3)SKiN封裝:德國Semikron公司采用納米銀燒結和SKiN布線技術,采用柔性 PCB板取代鍵合線實現芯片的上下表面電氣連接,模塊內部回路寄生電感僅為1. 5 nH。

(4)平面互連封裝:通過消除金屬鍵合線,將電流回路從DBC板平面布局拓展到芯片上下平面的層間布局,顯著減小了回路面積,降低了雜散電感參數,如Silicon Power公司采用端子直連(DLB) 、IR的Cu-Clip IGBT和Siemens的SiPLIT技術等。

(5)雙面焊接(燒結)封裝:在功率芯片兩側焊接DBC散熱基板,為芯片上下表面提供散熱通道;或者使用銀燒結技術將芯片一面焊接DBC,另一面連接鋁片。雙面散熱既能優化基板邊緣場強,還能夠降低電磁干擾(EMI),減小橋臂中點的對地寄生電容,使其具有損耗低、熱性能好、制造成本低等優點。橡樹嶺實驗室、中車時代電氣、天津大學和CPES等可以將寄生電感降低至5 nH。同時,銅燒結作為一種更低成本的芯片連接方案更被視為是未來幾年的研究熱點。目前雙面散熱技術主要應用在新能源電動車內部模塊。

(6)壓接封裝:壓接型器件各層組件界面間依靠壓力接觸實現電熱傳導,分為凸臺式和彈簧式兩類。與焊接型器件相比,壓接封裝結構模塊具有高功率密度、雙面散熱、低通態損耗、抗沖擊能力強、耐失效短路和易于串聯等優點,而且采用數量較少的壓接型模塊便可滿足換流時電壓等級和容量需求,但由于密封等要求多采用LTCC陶瓷設計,成本較高,且壓接封裝結構復雜,目前只用于高壓模塊的制造,具有一定的應用市場。但離汽車領域的實際應用尚有一定的差距。

(7)三維(3D)封裝:Tokuyama等和Herbsommer等將SiC模塊的上橋臂直接疊加在下橋臂上,由于SiC模塊的結構是垂直型的,可以大幅縮短換流回路的物理長度,以進一步減少與 di/dt相關的問題。

目前該封裝技術最大的優勢是可以將模塊寄生電感降至1 nH以下。還有將電壓波動最大的端子放置在三維夾心結構的中間,使端子與散熱器之間的寄生 電容 急劇 降低,進 而抑 制了 電磁 干擾噪聲。

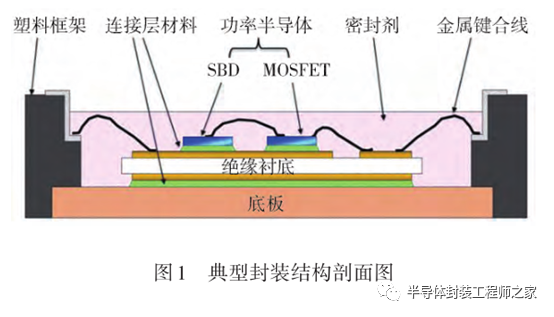

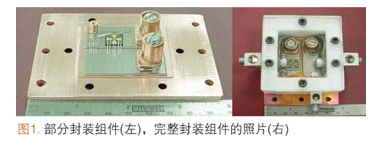

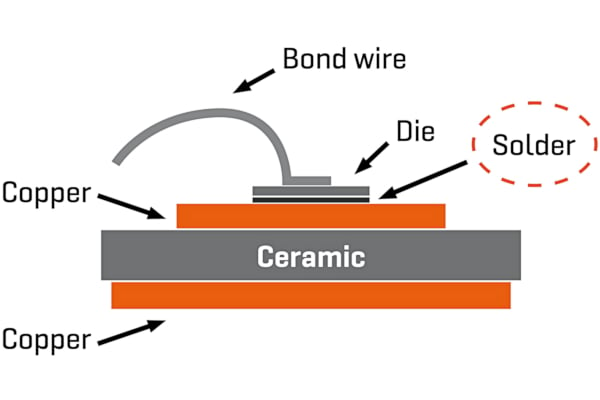

功率模塊的典型封裝結構剖面圖如圖1所示。

2.低雜散電感封裝技術

目前,引線鍵合分為線材和帶材兩類,根據金屬特性不同,主要有Al、Cu和Au。鋁線是最基本的鍵合方式,鋁帶通流能力更強,強度更高,Au由于其成本較高,應用相對較少,銅帶是未來的趨勢。其中柔性箔、鋁涂層銅線和頂部DBC-銅夾技術也具有一定的應用市場。

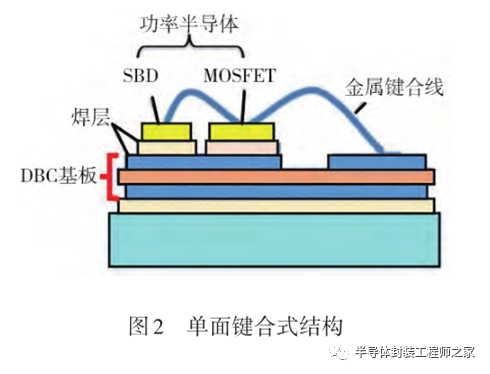

對于金屬引線鍵合式模塊的3維封裝結構,通過降維處理,可以極大簡化功率模塊結構的仿真時間,將三維立體結構轉換為2D平面結構的研究為整體功率模塊的研究應用奠定了基礎,如圖2所示。

本文中采用 ANSYS Q3D仿真軟件進行模型寄生參數提取,以單條金屬鍵合線的長度l和直徑d作為待優化參數,仿真分析l和d對寄生電感的影響特性,如圖3所示。

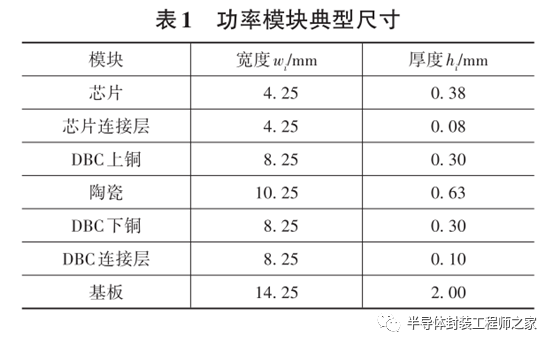

各層的厚度 h 1 -h 7 和邊距 a 1 -a 3 為優化參數,其中,a 3 是DBC結構上層銅距離陶瓷層邊沿的距離,因為絕緣性能、DBC小坑和阻焊等工藝的需求,a 3 普遍等于1 mm。傳統典型2維封裝結構模塊各層寬度w和厚度h的具體尺寸如表1所示。

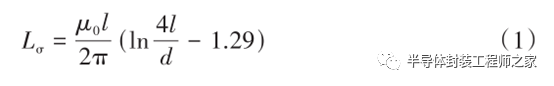

對于金屬引線鍵合式焊接的封裝結構,寄生電感主要來自于鍵合線,其寄生電感可近似表示為

式中:l為鍵合線長度,l= w 1 /2+a 1 ;μ 0 = 4 × 10 -7 ,是真空磁導率;d為鋁鍵合線的直徑。

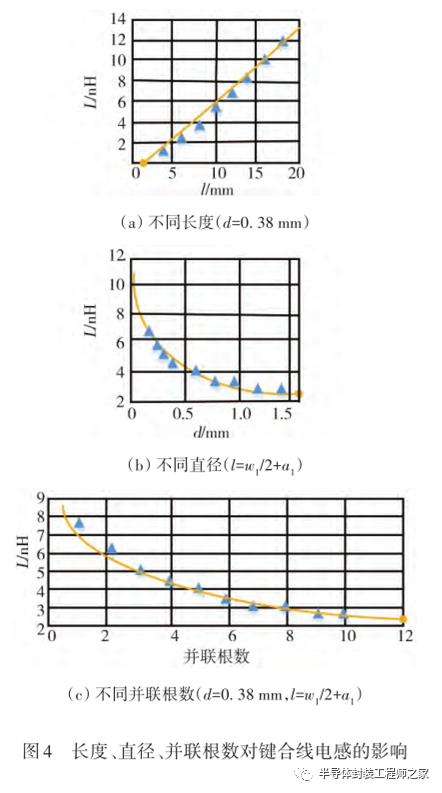

參照文獻對鍵合線進行仿真,結果如圖4所示。經驗證與式(1)的數據擬合結果基本一致。

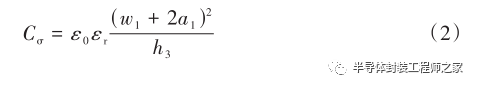

曾正等的研究表明,芯片功率回路的寄生電容主要由DBC陶瓷層的寄生電容決定,可表示為

式中:ε 0 = 8.85 × 10 -12 F/m ,表示真空介電常數;ε r =9 ,表示Al 2 O 3 陶瓷相對介電常數,對于陶瓷AIN和陶瓷Si 3 N 4 ,相對介電常數分別等于8. 8和6. 7。

寄生參數分布仿真結果如圖5所示,經驗證與式(1)和式(2)的數據擬合結果基本一致。

由圖4和圖5還可明顯看出各個關鍵變量對寄生參數的影響規律。鍵合線長度越短、直徑越大,寄生電感越小,其中鍵合線長度對寄生電感影響更顯著;陶瓷層越厚、面積越小,寄生電容越小,其中陶瓷層厚度對寄生電容影響更顯著。

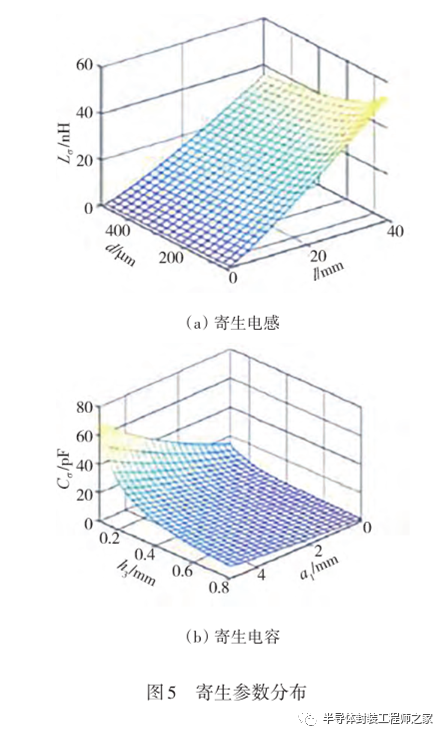

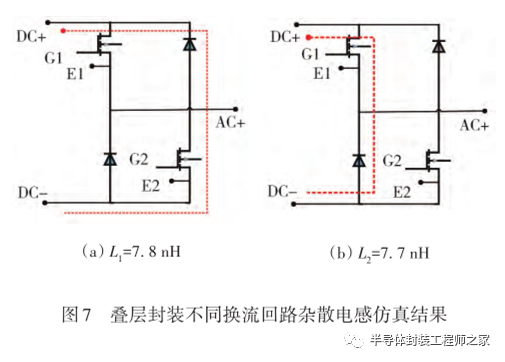

降低開關器件換流回路中電流流通路徑所通過的面積,可以減小雜散電感,將上半橋SiC MOSFET的續流二極管和下半橋的SiC MOSFET進行位置互換,減小換流路徑的導通面積,可降低雜散電感,如圖6所示,其仿真結果如圖7所示。

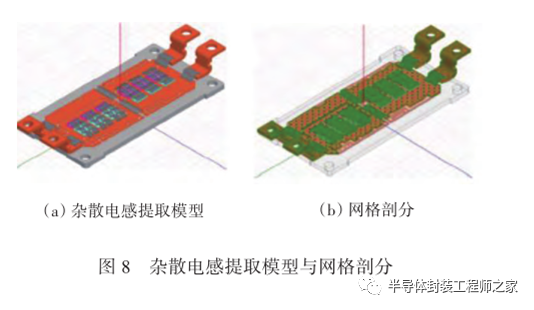

將功率模塊的封裝模型導入雜散參數提取軟件ANSYS. Q3D,依次采取網絡剖分、工況定義的步驟,設置激勵源(Source)和接地(Sink),并且分別把激勵源添加到功率模塊端子的表面,注意激勵源可以設置多個,但是接地只能一個,圖8是SiC模型的網格剖分圖。

牛利剛等研究表明,利用ANSYS. Q3D提取半橋功率模塊的寄生電感為20. 6 nH,實際檢測結果是21. 23 nH,相差為0. 63 nH,即相對誤差為3%,證明了疊層功率模塊雜散電感的仿真提取方法的準確性。

金屬鍵合線的寄生電感越小,寄生振蕩越輕微,開關關斷過程中的電壓沖擊越小,開關速率越高,開關損耗越小;與此同時,鍵合線的寄生電容也應盡可能小,以抑制電磁干擾的影響。

L σ和 C σ 共同決定電磁干擾(EMI)噪聲的轉折頻率 f r :

3. 雙面散熱技術

雙面散熱的功率模塊封裝結構可以通過取消金屬鍵合線,增加緩沖層并對緩沖層的形狀、材料、尺寸的優化,可減小雜散電感,增加散熱途徑,降低功率模塊中芯片所承受的長時間高溫危害,提高模塊的使用壽命。

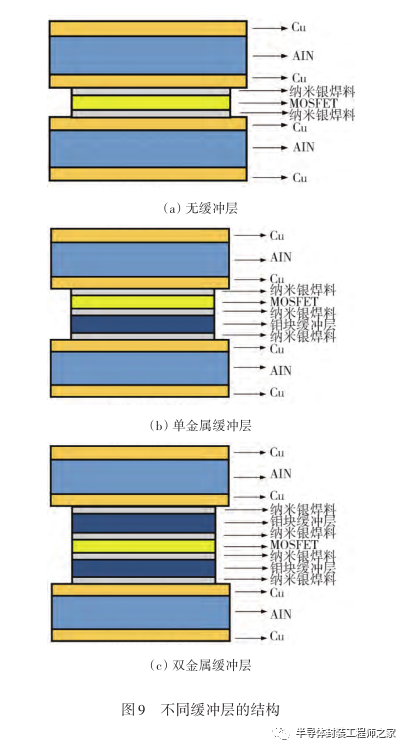

根據雙面散熱結構緩沖層的數量,分為無緩沖層、單層緩沖層、雙緩沖層3種,如圖9所示,其中無緩沖層和雙層緩沖層均為對稱結構。緩沖層可有不同形式,其中有的采用金屬墊塊。文獻中研究了芯片發熱狀態下3種模塊所受最高結溫和金屬墊塊結構所承受的熱應力分布情況。

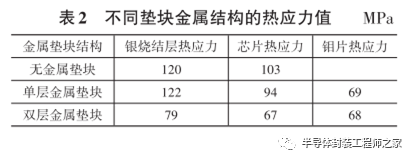

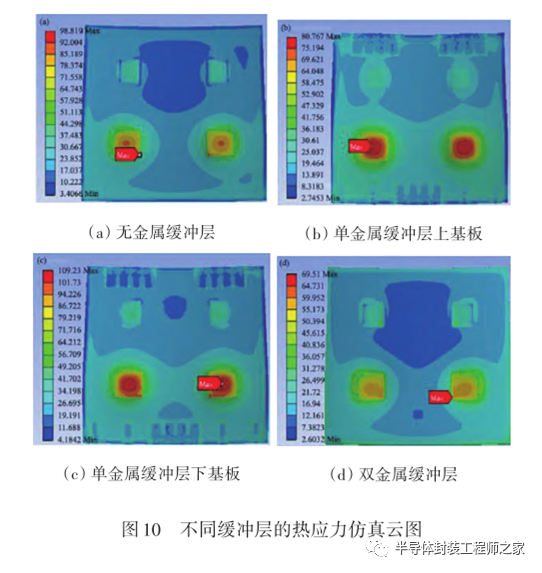

楊寧等的研究發現,不同金屬構造的各部分熱應力值如表2所示,而對應的仿真云圖如圖10所示。其中單層金屬緩沖層因結構的不對稱性,對其上下應力層需要單獨分析。

從仿真云圖中不難看出:無金屬墊塊緩沖層的雙面散熱結構的最大等效熱應力為99 MPa;單層金屬墊塊緩沖層的雙面散熱結構的上基板最大等效熱應力是109 MPa,下基板最大等效熱應力是70 MPa,上下基板的最大等效應力結果相差較大,主要與芯片和金屬層的熱膨脹系數、溫度差異有關;雙金屬層墊塊緩沖層的最大等效熱應力為81 MPa。

陸國權等研究表明,隨著鉬塊厚度的增加,應力緩沖效果明顯,應變減小。雙面互連的 SiC MOSFET芯片最大von Mises應力和納米銀互連層的最大塑性應變均減小。同時,在緩沖層和上基板間燒結銀互連層中增加1 mm銀墊片可進一步降低雙面互連結構的芯片應力和互連層應變,提高雙面散熱SiC模塊的熱機械可靠性。

與方形緩沖層對比,圓柱形緩沖層可有效消除芯片和納米銀互連層應力集中效應,大幅降低 SiC芯片所承受的最大 von Mises應力和燒結銀互連層的最大塑性應變。采用圓柱形緩沖層時,納米銀層塑性應變比采用方形緩沖層時的納米銀層的塑性應變值減少了47. 5%。這主要是因為圓柱形緩沖層邊緣過渡圓潤,應力分布更均勻,而方形緩沖層的邊緣或尖角易造成芯片和燒結銀互連層出現應力集中,造成局部熱應力劇增。

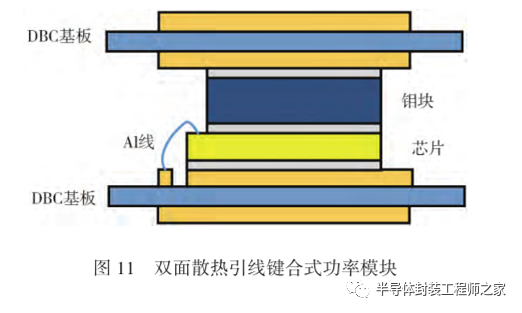

雙面散熱引線鍵合式功率模塊如圖 11 所示。Nakatsu等研究表明,雙面散熱功率模塊的熱阻值比引線鍵合功率模塊約小50%;另外,它還具有優異的電學性能。

Liang等研究表明,雙面散熱功率模塊的開關損耗降低到商業功率模塊的10%,由于鍵合引線會使寄生參數數值較大,所以無鍵合線模塊,寄生參數數值大幅減小,SiC芯片的耐高溫、高頻特性優勢得到極大發揮。

模塊封裝中的材料都具有一定的臨界熱應力點,超過這一數值,就會出現斷裂失效的危險。SiC功率模塊的襯底尺寸主要取決于芯片的面積大小,絕緣襯底常規厚度在0. 03 mm,翹曲率在3 mil/in,陶瓷材料用作絕緣襯底采用直接覆銅技術。金屬層邊緣采用臺階狀可有效減小應力,臺階高度應為銅層的一半。

基板主要趨勢是使用高性能材料,減少層數和界面的數量,同時保持電、熱和機械特性。絕緣金屬基板(IMS)和IMB基板僅用于中低功率模塊,如EV/HEV等。主流材料正逐漸從直接覆銅(DBC)轉向活性金屬釬焊(AMB),并采用高性能基材。雙面冷卻結構將促進在模塊的頂部使用第2個陶瓷基板/引線框架。

直接冷卻的基板,如銷鰭基板,減少熱界面的數量,避免使用熱界面材料(TIM)。基板和冷卻系統的集成以及冷卻模塊設計的部署和減少熱接口數量將是一個強大的趨勢,為未來幾年提供新的解決方案。封裝技術還需要具備高溫可靠性的陶瓷基板和金屬底板等相應套件。

目前能適應碳化硅設備更高運行溫度的硅膠和環氧材料正在研發中。為了實現復雜和緊湊的模塊設計,在包括EV/HEV等許多應用中,硅膠由于其低廉的價格,使用范圍更廣泛。環氧樹脂材料的應用,仍受到高溫下可靠性的限制。

4.失效方式匯總

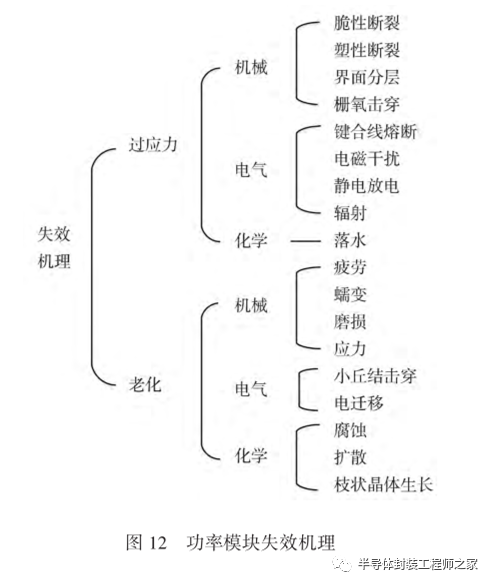

功率模塊的失效機理主要集中在電氣、溫度、材料、化學等各個方面,如圖12所示。

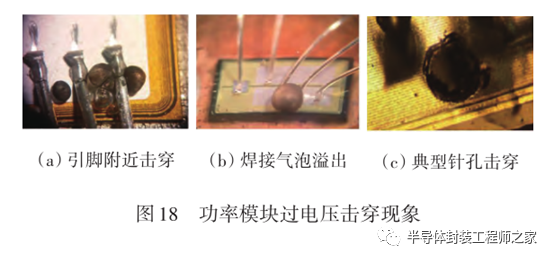

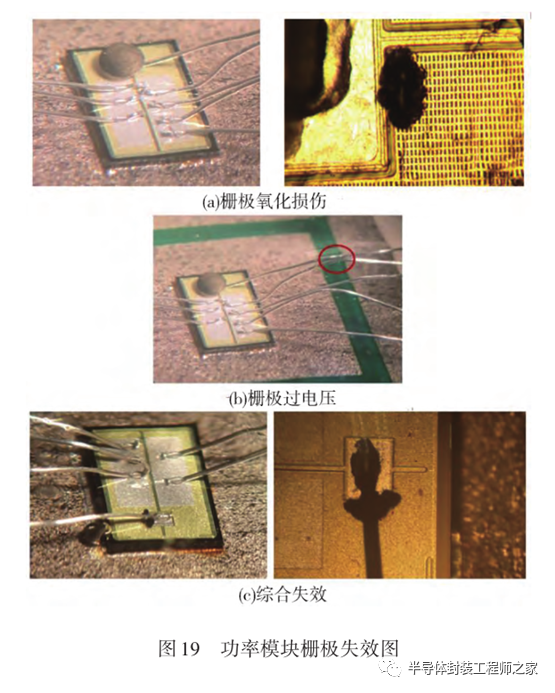

功率模塊常見的損壞有過流損壞、過熱損壞和過壓損壞等,過流損壞為流經功率模塊的電流超過耐流值,過流沖擊導致芯片發熱嚴重,超過結溫耐溫值,從而損壞芯片。過壓損壞為加在SiC MOSFET的漏極(G)和源極(S)間電壓 U GS 大于耐壓值,使得器件極間擊穿損壞。

保障功率模塊的安全運行,不僅要考慮功率模塊電流電壓的可承受范圍,還須考慮驅動信號添加后,避免導通電路出現短路問題和上下橋臂直通等故障。因此,可以通過增加檢測保護電路和對控制程序進行優化來保障功率模塊的安全運行。

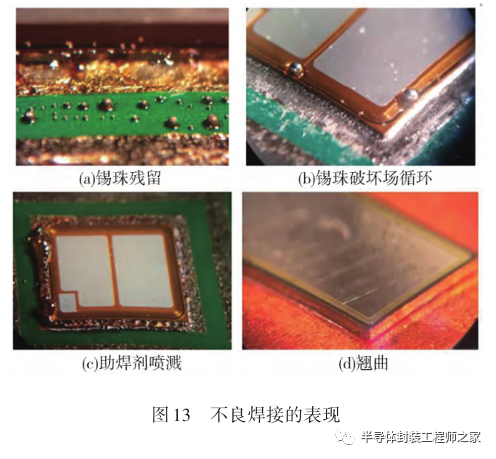

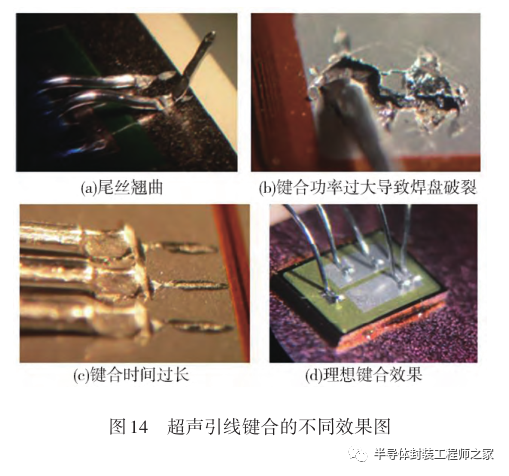

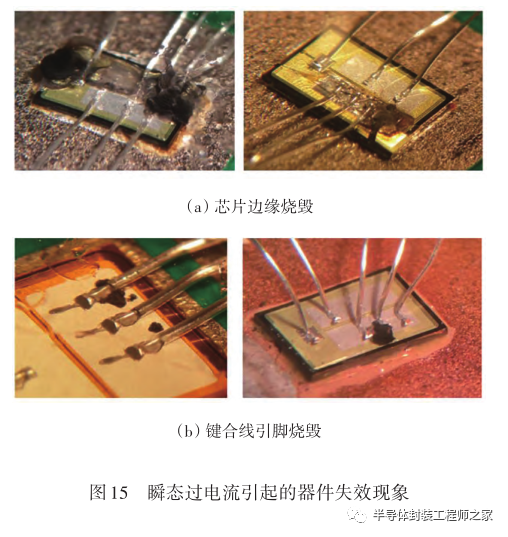

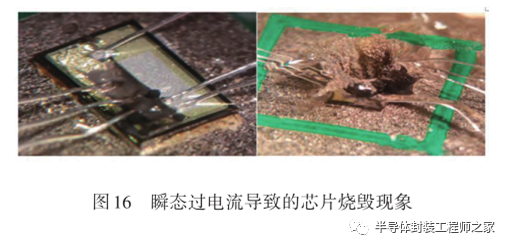

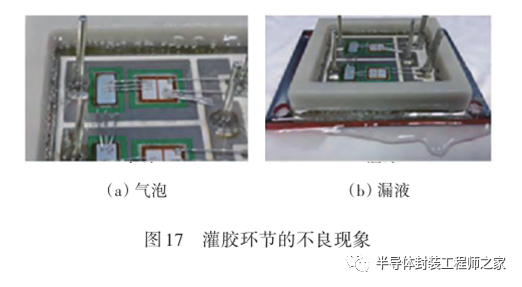

各種原因導致的功率模塊的真實失效現象如圖13~圖19所示。其中功率模塊里的續流二極管發生短路和集電極-發射極擊穿燒斷等是常見的失效現象。

對功率模塊通過均勻涂抹導熱硅脂作為熱界面材料(TIM)已經不能滿足要求,采用金屬燒結等方法是下一步的研究方向,另外增加散熱器、風扇和溫度傳感器等可有效防止過熱問題。增加電流互感器檢測器件與RC緩沖電路和對程序驅動算法進行優化等措施可有效解決過流問題。通過母線電壓采集,進行對比保護等可有效解決過壓問題。

5.先進技術展望

基于焊接與引線鍵合的傳統材料工藝存在熔點低、高溫蠕變失效、引線纏繞、寄生參數等無法解決的問題,新型互連材料正從焊接向壓接、燒結技術發展。

與焊接式功率模塊相比,壓接式模塊的優勢具體有以下幾點。

(1)焊接通過引線連接芯片和PCB板,在多次功率循環后容易老化脫落,造成模塊失效。而且,焊接層空洞增加熱阻,降低可靠性。壓接借助壓力將芯片壓在基板上,電流從銅板直接流過,提高可靠性。

(2)傳統焊接式多為單面散熱,而壓接式多為雙面散熱,可提升散熱性能,有利于器件性能的充分發揮。

(3)鍵合線和焊接層引入雜散參數,高頻特性下,電壓和電流易產生較大波動,影響芯片串聯特性。

考慮到納米銀焊膏具有高導電率、高導熱性和優良的延展性,且熔點顯著高于傳統焊料,相關科研團隊利用納米銀焊膏將芯片和集電極鉬層燒結在一起,成功開發出銀燒結壓接封裝器件,顯示出其在壓接型功率模塊的封裝應用中具有一定優勢。

銀燒結封裝可以降低壓接型器件的導通電壓和通態損耗,減緩芯片與發射極鉬層間的接觸磨損,提升器件使用壽命。

目前燒結封裝技術在發展中仍然存在著不能忽略的問題,同時也提出如下一些可行性方案。

(1)由于銀和SiC芯片背面材料熱膨脹系數不同引起的問題,可通過添加金屬緩沖層來改善互連性能,但會增加功率模塊封裝工藝的復雜性和成本。采用滿足性能指標和可靠性的燒結層代替緩沖層,成為研發的可行性方案。

(2)銀層的電遷移現象,不利于功率電子器件長期可靠應用。銅燒結既能滿足減少電遷移現象,又能夠降低成本,使其成為高溫模具連接材料的一種很有前途的替代品。

(3)優化燒結工業,創新燒結方案,縮減預熱、燒結時長,提升生產效率;流水線工作,提升可制造性和生產設計的靈活性。

(4)與無壓燒結相比,低壓燒結可靠度和散熱性能較好。雖然部分廠商已解決壓力問題,但是燒結過程中的致密性、連接層的溫控和極限環境中性能退化問題還尚待解決。

上述問題的解決需要產業鏈上下游的聯動協調攻關,部分問題隨著技術進步將逐步得到解決。盡管當前模塊封裝幾乎全是以連線鍵合方式為主,預計未來3~5年銀燒結封裝技術會是功率模塊互連的主流技術。由于銀離子遷移對互聯結構有負面影響,加之成本和熱應力適配需求,與銀燒結技術類似的瞬時液相燒結(TLPS)、銀銅燒結、銅燒結技術和相應的焊漿材料也在快速發展,部分技術瓶頸有望在近幾年突破。芯片貼裝、基板連接、模塊與散熱器的連接等都是燒結技術潛在的應用范圍。

6 . 結論

本文重點分析和綜述了碳化硅功率模塊封裝中的 4 個關鍵問題:(1)總結歸納了結構各異的低雜散參數模塊封裝形式,列舉闡述各模塊性能優勢;(2)聚焦典型封裝結構下,分析概括鍵合式功率模塊的金屬鍵合線長度、寬度和并聯根數對寄生電感影響,直接覆銅(DBC)陶瓷基板中陶瓷層的面積、高度對寄生電容的影響,以及采用疊層換流技術優化寄生參數等成果;(3)在封裝模塊散熱方面,綜述了雙面散熱結構的緩沖層厚度和形狀對散熱和應力形變的影響;(4)匯總了功率模塊常見失效圖譜和解決措施,為模塊的安全使用提供參考。最后探討了先進燒結銀技術的需求和關鍵問題,并展望了燒結封裝技術和材料發展方向。

作者:蔡蔚?楊茂通?劉洋?李道會

(哈爾濱理工大學電氣與電子工程學院 哈爾濱理工大學材料學院上海蔚來汽車有限公司)

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論