本文從關(guān)于固晶的挑戰(zhàn)、如何選用鍵合線材、瓷嘴與焊線參數(shù)等幾個方面向大家闡述在微小化的趨勢下關(guān)于LED小芯片封裝技術(shù)難點解析。

2016-03-17 14:29:33 3663

3663 一些后處理步驟,例如研磨、化學(xué)機械研磨(CMP)、SiC外延、注入、檢測、化學(xué)氣相沉積(CVD)和物理氣相沉積(PVD)。SiC晶圓因其半透明性質(zhì)和材料硬度而面臨許多挑戰(zhàn),這需要對關(guān)鍵工藝步驟設(shè)備進行

2019-05-12 23:04:07

小弟想知道8寸晶圓盒的制造工藝和檢驗規(guī)范,還有不知道在大陸有誰在生產(chǎn)?

2010-08-04 14:02:12

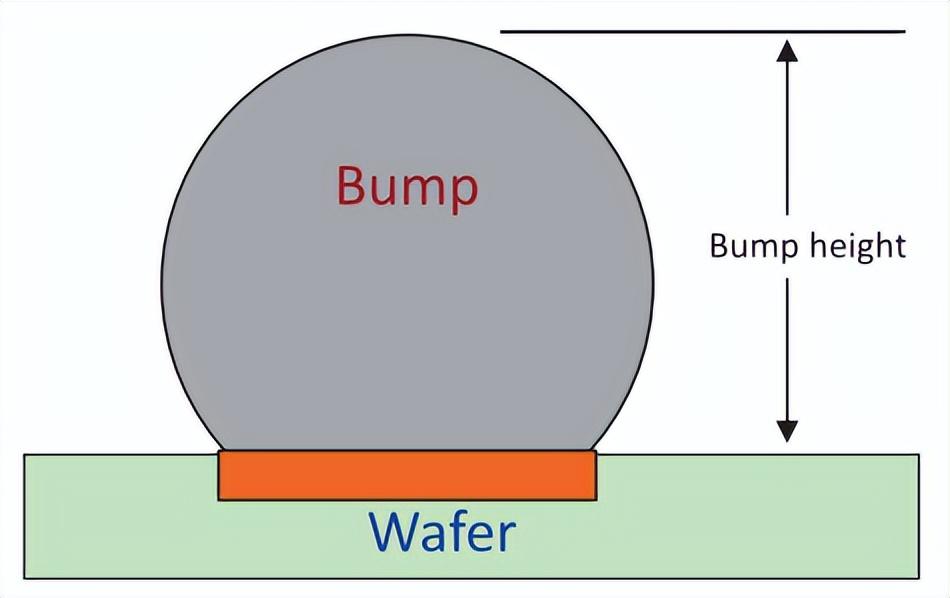

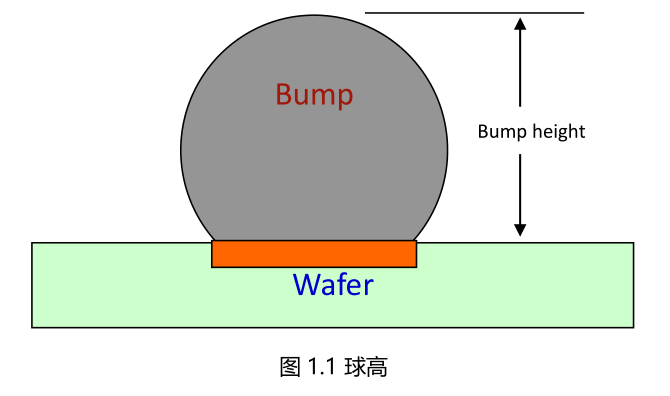

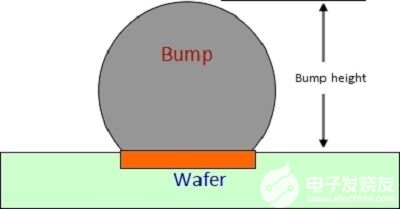

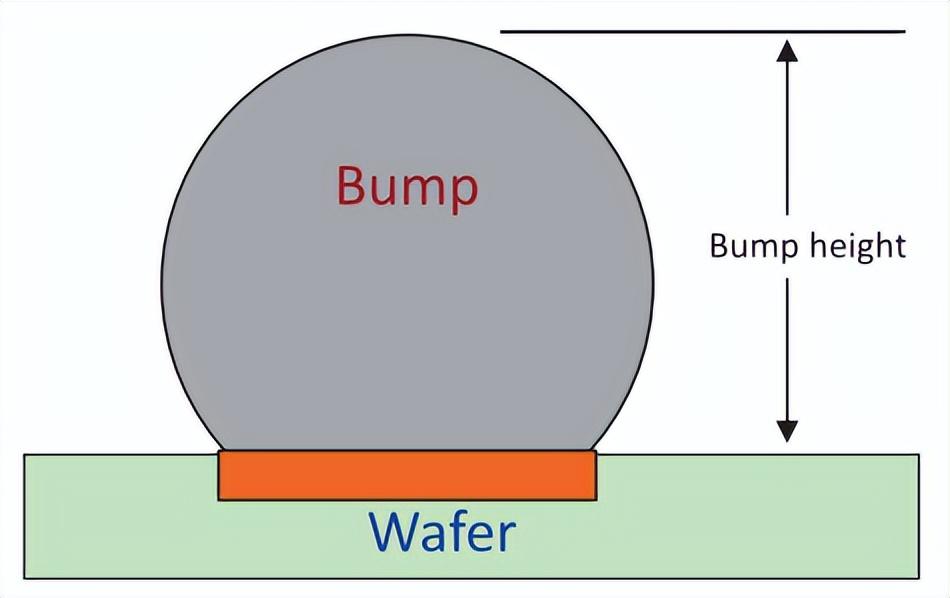

Bump Mapping通過改變幾何體表面各點的法線,使本來是平的東西看起來有凹凸的效果,是一種欺騙眼睛的技術(shù).具體在封裝工藝中倒裝芯片(Flip-chip IC)封裝技術(shù),不但能夠滿足芯片大量

2021-07-23 06:59:24

安森美半導(dǎo)體全球制造高級副總裁Mark Goranson最近訪問了Mountain Top廠,其8英寸晶圓廠正慶祝制造8英寸晶圓20周年。1997年,Mountain Top點開設(shè)了一個新建的8英寸

2018-10-25 08:57:58

。該方法與晶圓微調(diào)法相似,通過調(diào)整輸入級上的電阻器來校正失調(diào)電壓。但是在這種應(yīng)用實例中,調(diào)整工作是在器件最終封裝后完成。調(diào)整方法通常是在最后封裝級制造測試過程中將數(shù)字信號應(yīng)用于輸出。微調(diào)完成后,微調(diào)

2018-09-18 07:56:15

`晶圓制造總的工藝流程芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構(gòu)裝工序(Packaging)、測試工序(Initial

2011-12-01 15:43:10

圓比人造鉆石便宜多了,感覺還是很劃算的。硅的純化I——通過化學(xué)反應(yīng)將冶金級硅提純以生成三氯硅烷硅的純化II——利用西門子方法,通過三氯硅烷和氫氣反應(yīng)來生產(chǎn)電子級硅 二、制造晶棒晶體硅經(jīng)過高溫成型,采用

2019-09-17 09:05:06

`微晶片制造的四大基本階段:晶圓制造(材料準(zhǔn)備、長晶與制備晶圓)、積體電路制作,以及封裝。晶圓制造過程簡要分析[hide][/hide]`

2011-12-01 13:40:36

晶圓制造的基礎(chǔ)知識,適合入門。

2014-06-11 19:26:35

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合,即是通過化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達到密封效果。如下

2021-02-23 16:35:18

晶圓級封裝技術(shù)Wafer Level Package Technology Board Mounting Application Note for 0.800mm pitch

2009-06-12 23:57:22

晶圓級封裝技術(shù)源自于倒裝芯片。晶圓級封裝的開發(fā)主要是由集成器件制造廠家(IBM)率先啟動。1964年,美國IBM公司在其M360計算器中最先采用了FCOB焊料凸點倒裝芯片器件。

2020-03-06 09:02:23

晶圓級封裝類型及涉及的產(chǎn)品

2015-07-11 18:21:31

晶圓級CSP的返修工藝包括哪幾個步驟?晶圓級CSP對返修設(shè)備的要求是什么?

2021-04-25 08:33:16

晶圓級CSP的元件如何重新貼裝?怎么進行底部填充?

2021-04-25 06:31:58

細(xì)間距的晶圓級CSP時,將其當(dāng)做倒裝晶片并采用助焊劑浸蘸的方法進行組裝,以取代傳統(tǒng)的焊膏印刷組裝,如圖2所示,首先將晶圓級CSP浸蘸在設(shè)定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關(guān)于錫膏裝配和助焊劑裝配的優(yōu)缺點。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

; ·尺寸和位置精度受阻焊膜窗口的影響,不適合密間距元件的裝配。 NSMD焊盤的尺寸和位置不受阻焊膜窗口的影響,在焊盤和阻焊膜之間有一定空隙,如圖2和圖3所示。對于 密間距晶圓級CSP,印刷電路板上的焊盤

2018-09-06 16:32:27

晶圓級CSP裝配回流焊接工藝控制,看完你就懂了

2021-04-25 06:28:40

晶圓級CSP的裝配對貼裝壓力控制、貼裝精度及穩(wěn)定性、照相機和影像處理技術(shù)、吸嘴的選擇、助焊劑應(yīng) 用單元和供料器,以及板支撐及定位系統(tǒng)的要求類似倒裝晶片對設(shè)備的要求。WLCSP貼裝工藝的控制可以參

2018-09-06 16:32:18

經(jīng)底部填充的CSP裝配,其穩(wěn)健的機械連接強度得到很大的提升。在二級裝配中,由于底部填充,其抵御 由于扭轉(zhuǎn)、振動和熱疲勞應(yīng)力的能力得以加強。但經(jīng)過底部填充的CSP如何進行返修成了我們面臨

2018-09-06 16:32:17

先進封裝發(fā)展背景晶圓級三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

晶圓級芯片封裝技術(shù)是對整片晶圓進行封裝測試后再切割得到單個成品芯片的技術(shù),封裝后的芯片尺寸與裸片一致。

2019-09-18 09:02:14

` 晶圓級封裝是一項公認(rèn)成熟的工藝,元器件供應(yīng)商正尋求在更多應(yīng)用中使用WLP,而支持WLP的技術(shù)也正快速走向成熟。隨著元件供應(yīng)商正積極轉(zhuǎn)向WLP應(yīng)用,其使用范圍也在不斷擴大。 目前有5種成熟

2011-12-01 14:33:02

在硅晶圓被蝕刻入的晶體管起不了任何作用,這一切是由于制造技術(shù)限制而造成的,任何一個存在上面問題的芯片將因不能正常工作而被報廢。上圖中,一塊硅晶圓中蝕刻了16個晶體管,但其中4個晶體管存在缺陷,因此我們

2011-12-01 16:16:40

本人想了解下晶圓制造會用到哪些生產(chǎn)輔材或生產(chǎn)耗材

2017-08-24 20:40:10

晶圓的制造過程是怎樣的?

2021-06-18 07:55:24

` 硅是由石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造積體電路的石英半導(dǎo)體的材料,經(jīng)過照相制版,研磨,拋光,切片等程序,將多晶硅融解拉出單晶硅晶棒

2011-09-07 10:42:07

測試晶格:指晶圓表面具有電路元件及特殊裝置的晶格,在晶圓制造期間,這些測試晶格需要通過電流測試,才能被切割下來 4 邊緣晶格:晶圓制造完成后,其邊緣會產(chǎn)生部分尺寸不完整的晶格,此即為邊緣晶格,這些

2011-12-01 15:30:07

晶圓針測制程介紹 晶圓針測(Chip Probing;CP)之目的在于針對芯片作電性功能上的 測試(Test),使 IC 在進入構(gòu)裝前先行過濾出電性功能不良的芯片,以避免對不良品增加制造

2020-05-11 14:35:33

,、WAFER承載料盒、晶圓提籃,芯片盒,晶圓包裝盒,晶圓包裝,晶圓切片,晶圓生產(chǎn),晶圓制造,晶圓清洗,晶圓測試,晶圓切割,晶圓代工,晶圓銷售,晶圓片測試,晶圓運輸用包裝盒,晶圓切割,防靜電IC托盤(IC

2020-07-10 19:52:04

及LED器件,這樣就很大程度上降低了LED晶圓的產(chǎn)出效率。激光加工是非接觸式加工,作為傳統(tǒng)機械鋸片切割的替代工藝,激光劃片切口非常小,聚焦后的激光微細(xì)光斑作用的晶圓表面迅速氣化材料,在LED有源區(qū)之間制造

2011-12-01 11:48:46

C語言要點解析(含便于理解的備注)C語言要點解析(含便于理解的備注).pdf 2016-10-27 17:59 上傳 點擊文件名下載附件 1.08 MB, 下載次數(shù): 8

2018-07-19 09:15:26

應(yīng)力會使光器件和光纖之間的對準(zhǔn)發(fā)生偏移。在高精度加速度計和陀螺儀中,封裝需要和MEMS芯片隔離以優(yōu)化性能(見圖1)。圖1 常規(guī)晶圓級封裝(WLP)結(jié)構(gòu)示意圖根據(jù)生產(chǎn)的MEMS器件類型的不同,電子性能

2010-12-29 15:44:12

晶圓級芯片級封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

工藝,制造出各種性能優(yōu)異、價格低廉、微型化的傳感器、執(zhí)行器、驅(qū)動器和微系統(tǒng)。SITIME MEMS電子發(fā)燒友振是由MEMS電子發(fā)燒友圓與CMOS晶圓上下疊加而成,而CMOS晶圓則包括了NON

2017-04-06 14:22:11

SPI_NSS的知識點解析,絕對實用

2022-02-17 08:08:10

SiC SBD 晶圓級測試 求助:需要測試的參數(shù)和測試方法謝謝

2020-08-24 13:03:34

小,擊穿電壓穩(wěn)定,良率高,鉗位 電壓一般,電容有低容,普容和高容,6寸可以做回掃型ESD產(chǎn)品;第三代TVS主要以8寸晶圓流片為主,以CSP晶圓級封裝為主(DFN),這種產(chǎn)品是高性能的ESD,采用8寸的先進制造

2020-07-30 14:40:36

everspin生態(tài)系統(tǒng)和制造工藝創(chuàng)新

2021-01-01 07:55:49

subdev/video列表的知識點解析,絕對實用

2022-03-10 06:25:41

。光刻膠的圖案通過蝕刻劑轉(zhuǎn)移到晶片上。沉積:各種材料的薄膜被施加在晶片上。為此,主要使用兩種工藝,物理氣相沉積 (PVD) 和化學(xué)氣相沉積 (CVD)。制作步驟:1.從空白晶圓開始2.自下而上構(gòu)建

2021-07-08 13:13:06

圓制造相關(guān)工作經(jīng)驗. 3-5年(資深),5-7年(主任)?良好的語言表達能力及溝通協(xié)調(diào)能力?良好的分析和解決問題的技巧?具團隊合作精神?良好的自我驅(qū)動能力?至少英語CET-4級.良好的英語書面和口語能力有興趣的請加QQ:77346561 或者發(fā)送簡歷至郵箱:77346561@qq.com

2017-08-14 18:36:23

:面議【六寸晶圓制造領(lǐng)班】崗位職責(zé):1.落實本工序生產(chǎn)計劃,跟蹤生產(chǎn)進度;保證質(zhì)量、交期;2.負(fù)責(zé)本工序在制品數(shù)量的準(zhǔn)確;工治具的管理;設(shè)備的維護與保養(yǎng);勞動紀(jì)律、工藝執(zhí)行的監(jiān)督檢查;3.本工序生產(chǎn)日報表

2016-10-08 09:55:38

`晶圓是如何生長的?又是如何制備的呢?本文的主要內(nèi)容有:沙子轉(zhuǎn)變?yōu)榘雽?dǎo)體級硅的制備,再將其轉(zhuǎn)變成晶體和晶圓,以及生產(chǎn)拋光晶圓要求的工藝步驟。這其中包括了用于制造操作晶圓的不同類型的描述。生長

2018-07-04 16:46:41

的用于保護不被刻蝕區(qū)域的光刻膠將被移除。 封裝在一塊晶圓上制造出芯片需要經(jīng)過上千道工序,從設(shè)計到生產(chǎn)需要三個多月的時間。為了把芯片從晶圓上取出來,要用金剛石鋸將其切成單個芯片。這些被稱為“裸晶”的芯片

2022-04-08 15:12:41

效應(yīng)和功耗。因此,三維系統(tǒng)集成技術(shù)在性能、功能和形狀因素等方面都具有較大的優(yōu)勢。用于三維集成的先進晶圓級技術(shù)晶圓級封裝技術(shù)已在許多產(chǎn)品制造中得到廣泛應(yīng)用。目前正在開發(fā)晶圓級封裝的不同工藝技術(shù),以滿足在提高

2011-12-02 11:55:33

納米到底有多細(xì)微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

。二氧化硅礦石經(jīng)由電弧爐提煉,鹽酸氯化,并經(jīng)蒸餾后,制成了高純度的多晶硅,其純高達99.999999999%。晶圓制造廠再把此多晶硅融解,再于融液里種入籽晶,然后將其慢慢拉出,以形成圓柱狀的單晶硅晶棒

2011-12-01 11:40:04

`晶圓級封裝(WLP)就是在其上已經(jīng)有某些電路微結(jié)構(gòu)(好比古董)的晶片(好比座墊)與另一塊經(jīng)腐蝕帶有空腔的晶片(好比玻璃罩)用化學(xué)鍵結(jié)合在一起。在這些電路微結(jié)構(gòu)體的上面就形成了一個帶有密閉空腔的保護

2011-12-01 13:58:36

的輔助。 測試是為了以下三個目標(biāo)。第一,在晶圓送到封裝工廠之前,鑒別出合格的芯片。第二,器件/電路的電性參數(shù)進行特性評估。工程師們需要監(jiān)測參數(shù)的分布狀態(tài)來保持工藝的質(zhì)量水平。第三,芯片的合格品與不良品

2011-12-01 13:54:00

1、為什么晶圓要做成圓的?如果做成矩形,不是更加不易產(chǎn)生浪費原料?2、為什么晶圓要多出一道研磨的工藝?為什么不能直接做成需求的厚度?

2014-01-20 15:58:42

單晶的晶圓制造步驟是什么?

2021-06-08 06:58:26

今日分享晶圓制造過程中的工藝及運用到的半導(dǎo)體設(shè)備。晶圓制造過程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴散等。這幾個主要步驟都需要若干種半導(dǎo)體設(shè)備,滿足不同的需要。設(shè)備中應(yīng)用較為廣泛

2018-10-15 15:11:22

作者:ADI公司 Dust Networks產(chǎn)品部產(chǎn)品市場經(jīng)理 Ross Yu,遠程辦公設(shè)施經(jīng)理 Enrique Aceves問題 對半導(dǎo)體晶圓制造至關(guān)重要的是細(xì)致、準(zhǔn)確地沉積多層化學(xué)材料,以形成

2019-07-24 06:54:12

目晶圓提高了設(shè)計效率,降低了開發(fā)成本,為設(shè)計人員提供了實踐機會,并促進了集成電路設(shè)計成果轉(zhuǎn)化,對IC設(shè)計人才的培訓(xùn),及新產(chǎn)品的開發(fā)研制均有相當(dāng)?shù)拇龠M作用。隨著制造工藝水平的提高,在生產(chǎn)線上制造芯片

2011-12-01 14:01:36

晶圓劃片 (Wafer Dicing )將晶圓或組件進行劃片或開槽,以利后續(xù)制程或功能性測試。提供晶圓劃片服務(wù),包括多項目晶圓(Multi Project Wafer, MPW)與不同材質(zhì)晶圓劃片

2018-08-31 14:16:45

是什么推動著高精度模擬芯片設(shè)計?如何利用專用晶圓加工工藝實現(xiàn)高性能模擬IC?

2021-04-07 06:38:35

對視頻圖像及其顯示的知識點解析,看完你就懂了

2021-06-04 06:59:12

)技術(shù),及其主要的工藝流程。這四種加成制造技術(shù)都不使用焊料,無高溫回流工藝,可實現(xiàn)高可靠性、高性能和高密度的三維封裝制造,同時也屬于綠色制造技術(shù),所以具有廣闊的發(fā)展前景。【關(guān)鍵詞】:嵌入式;;電子制造

2010-04-24 10:08:17

)技術(shù),及其主要的工藝流程。這四種加成制造技術(shù)都不使用焊料,無高溫回流工藝,可實現(xiàn)高可靠性、高性能和高密度的三維封裝制造,同時也屬于綠色制造技術(shù),所以具有廣闊的發(fā)展前景。【關(guān)鍵詞】:嵌入式;;電子制造

2010-04-24 10:08:51

怎么選擇晶圓級CSP裝配工藝的錫膏?

2021-04-25 08:48:29

過處理之后成為光罩 這些就是最后完成的晶圓成品 接下來看晶圓切割 形成成品之后的晶圓還要經(jīng)過切割才能成為應(yīng)用于芯片制造。 這里演示的就是晶圓切割 放大觀看 接下來是演示經(jīng)過切割的晶圓的一些應(yīng)用。 可以應(yīng)用于芯片制造、液晶顯示屏制造或者手機芯片制造等。 ``

2011-12-01 15:02:42

固態(tài)圖像傳感器要求在環(huán)境大氣中得到有效防護。第一代圖像傳感器安裝在帶玻璃蓋的標(biāo)準(zhǔn)半導(dǎo)體封裝中。這種技術(shù)能使裸片得到很好的密封和異常堅固的保護,但體積比較龐大,制造成本也比較高。引入晶圓級封裝后

2018-12-03 10:19:27

招聘6/8吋晶圓測試工藝工程師/主管1名工作地點:無錫工資:面議要求:1. 工藝工程師:晶圓測試經(jīng)驗3年以上,工藝主管:晶圓測試經(jīng)驗5年以上;2. 精通分立器件類產(chǎn)品晶圓測試,熟悉IC晶圓測試尤佳

2017-04-26 15:07:57

激光用于晶圓劃片的技術(shù)與工藝 激光加工為無接觸加工,激光能量通過聚焦后獲得高能量密度,直接將硅片

2010-01-13 17:01:57

?工藝提供了一種經(jīng)濟高效的方式進行單個晶片堆疊,并能產(chǎn)出高良率以及穩(wěn)固可靠的連接。在未來,我們期待Durendal?工藝能促進扇出型晶圓級封裝在單個晶片堆疊中得到更廣泛的應(yīng)用。

2020-07-07 11:04:42

`什么是硅晶圓呢,硅晶圓就是指硅半導(dǎo)體積體電路制作所用的硅晶片。晶圓是制造IC的基本原料。硅晶圓和晶圓有區(qū)別嗎?其實二者是一個概念。集成電路(IC)是指在一半導(dǎo)體基板上,利用氧化、蝕刻、擴散等方法

2011-12-02 14:30:44

芯片制造全工藝流程詳情

2020-12-28 06:20:25

是由石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造集成電路的石英半導(dǎo)體的材料,將其切片就是芯片制作具體需要的晶圓。晶圓越薄,成產(chǎn)的成本越低,但對工藝就要

2016-06-29 11:25:04

石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造集成電路的石英半導(dǎo)體的材料,將其切片就是芯片制作具體需要的晶圓。晶圓越薄,成產(chǎn)的成本越低,但對工藝就要

2018-08-16 09:10:35

SRAM中晶圓級芯片級封裝的需求

2020-12-31 07:50:40

如題,或者其他圓片級封裝的工藝,謝謝。

2012-11-02 10:20:12

要求。 用于固態(tài)圖像傳感器的第三代晶圓級封裝的關(guān)鍵區(qū)別是裸片反面的玻璃板被特殊配方的聚合體所替代。對封裝結(jié)構(gòu)和工藝流程做少許修改就可以使這種聚合體聯(lián)接到正面玻璃上,從而使器件的整個外圍獲得良好的密封效果

2018-10-30 17:14:24

晶圓測溫系統(tǒng),晶圓測溫?zé)犭娕迹?b class="flag-6" style="color: red">晶圓測溫裝置一、引言隨著半導(dǎo)體技術(shù)的不斷發(fā)展,晶圓制造工藝對溫度控制的要求越來越高。熱電偶作為一種常用的溫度測量設(shè)備,在晶圓制造中具有重要的應(yīng)用價值。本文

2023-06-30 14:57:40

大型風(fēng)力發(fā)電機轉(zhuǎn)軸加工工藝難點解析_王艷芳

2017-01-01 16:24:03 0

0 (Low Noise Amplifier)、濾波器(Filter)、無源器件等集成為一個模組,從而提高性能,并減小封裝體積。然而,受限于國外專利以及設(shè)計水平等因素,國產(chǎn)濾波器的份額相當(dāng)?shù)汀T谀K集成化

2023-01-13 15:57:47 1415

1415

)、濾波器(Filter)、無源器件等集成為一個模組,從而提高性能,并減小封裝體積。然而,受限于國外專利以及設(shè)計水平等因素,國產(chǎn)濾波器的份額相當(dāng)?shù)汀T谀K集成化的趨勢下,國內(nèi)射頻巨頭在布局和生產(chǎn)濾波器。聲學(xué)濾波器可分為聲表面濾波器和體聲波濾波器,

2023-03-24 17:50:54 1106

1106

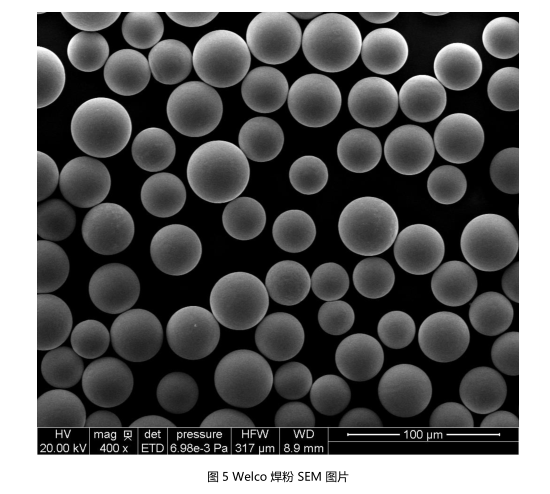

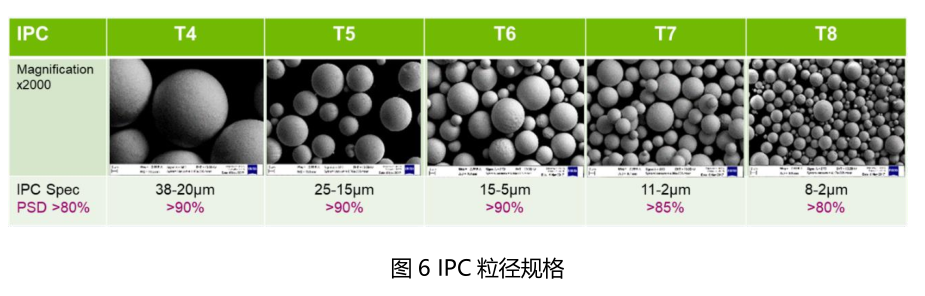

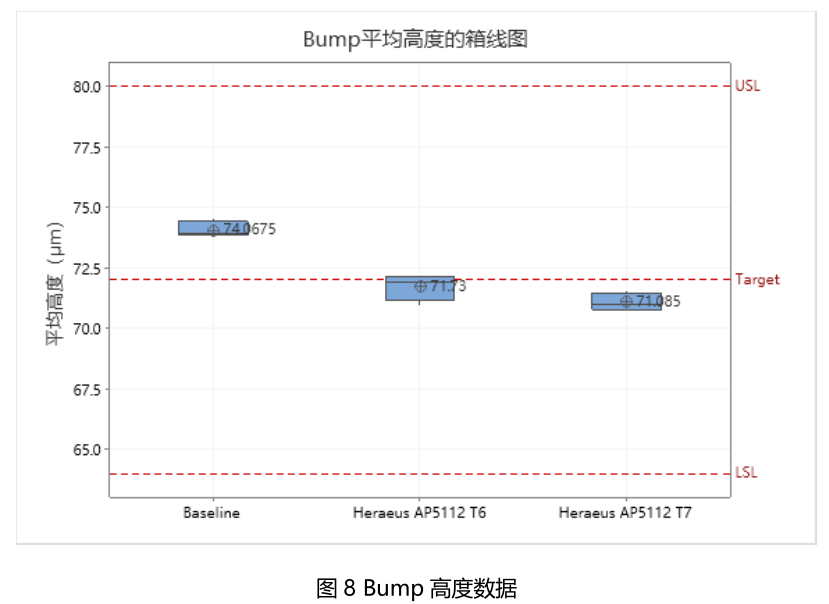

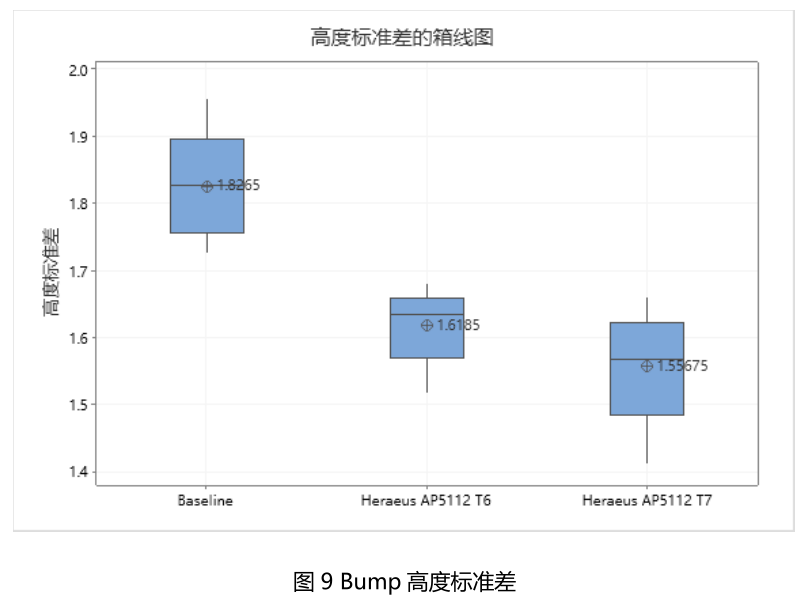

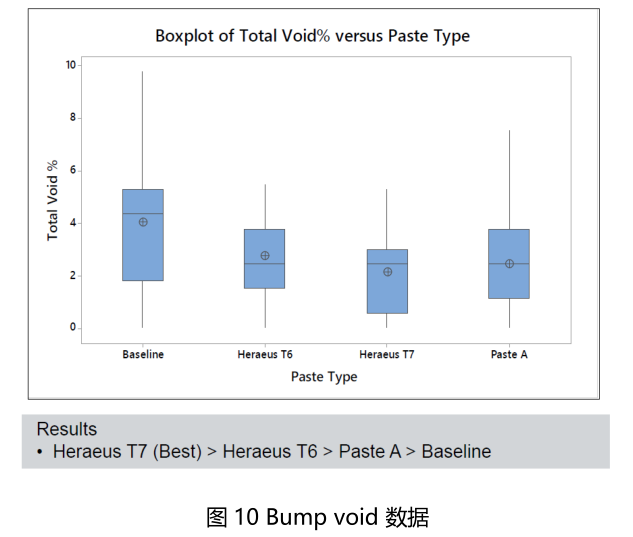

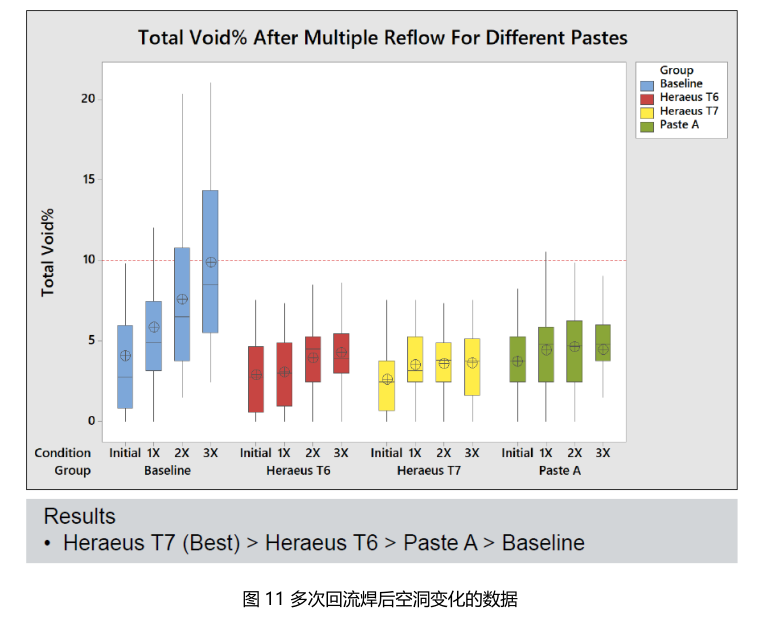

BumpMetrologysystem—BOKI_1000在半導(dǎo)體行業(yè)中,Bump、RDL、TSV、Wafer合稱先進封裝的四要素,其中Bump起著界面互聯(lián)和應(yīng)力緩沖的作用。Bump是一種金屬

2023-09-06 14:26:09 1236

1236

電子發(fā)燒友App

電子發(fā)燒友App

評論