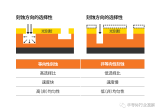

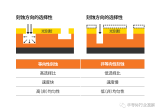

等離子體圖形化刻蝕過程中,刻蝕圖形將影響刻蝕速率和刻蝕輪廓,稱為負(fù)載效應(yīng)。負(fù)載效應(yīng)有兩種:宏觀負(fù)載效應(yīng)和微觀負(fù)載效應(yīng)。

2023-02-08 09:41:26 2467

2467 單晶硅刻蝕用來形成相鄰晶體管間的絕緣區(qū),多晶硅刻蝕用于形成柵極和局部連線。

2023-02-13 11:13:23 5905

5905

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設(shè)計(jì)好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進(jìn)行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 844

844

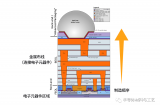

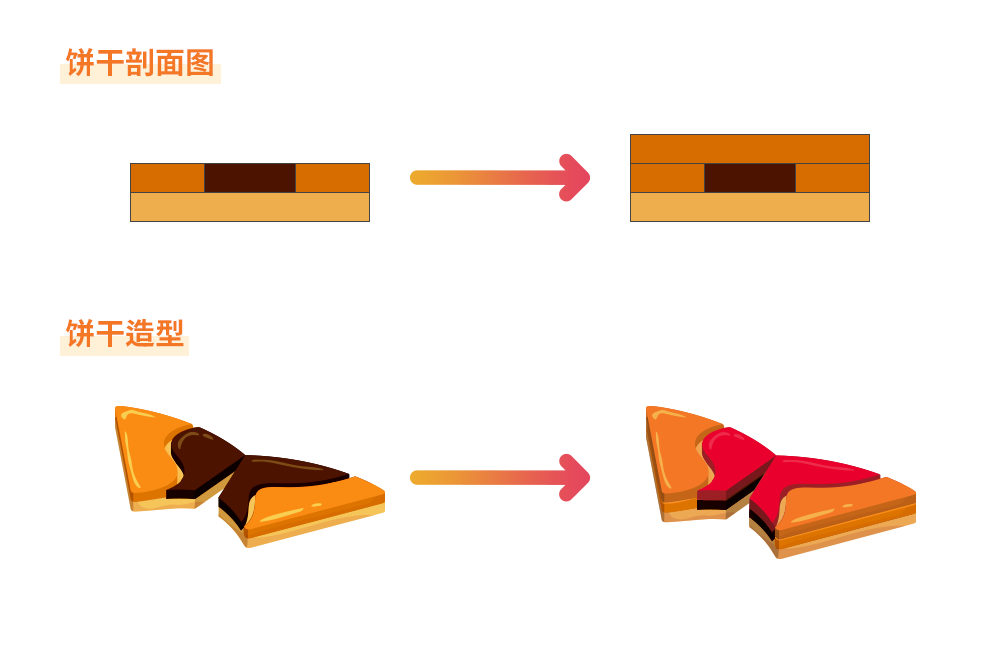

在半導(dǎo)體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點(diǎn),在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 506

506 在半導(dǎo)體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創(chuàng)建所需的微細(xì)圖案。半導(dǎo)體“刻蝕”工藝所采用的氣體和設(shè)備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 996

996

在半導(dǎo)體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現(xiàn),有著千絲萬縷的聯(lián)系,這一節(jié)介紹半導(dǎo)體刻蝕工藝。

2024-01-26 10:01:58 552

552

本人5年工作經(jīng)驗(yàn),主要負(fù)責(zé)半導(dǎo)體工藝及產(chǎn)品開發(fā)相關(guān)工作,工藝方面對拋光、切割比較精通,使用過NTS/DISCO/HANS等設(shè)備,熟悉設(shè)備參數(shù)設(shè)置,工藝改善等,產(chǎn)品開發(fā)方面熟悉新產(chǎn)品導(dǎo)入流程。目前本人已經(jīng)離職,尋找四川境內(nèi)相關(guān)工作,如有機(jī)會請與我聯(lián)系:***,謝謝!

2016-10-12 10:11:16

` 本帖最后由 firstchip 于 2015-1-20 10:54 編輯

北京飛特馳科技有限公司對外提供6英寸半導(dǎo)體工藝代工服務(wù)和工藝加工服務(wù),包括:產(chǎn)品代工、短流程加工、單項(xiàng)工藝加工等

2015-01-07 16:15:47

本帖最后由 eehome 于 2013-1-5 09:51 編輯

半導(dǎo)體工藝

2012-08-20 09:02:05

有沒有半導(dǎo)體工藝方面的資料啊

2014-04-09 22:42:37

半導(dǎo)體發(fā)展至今,無論是從結(jié)構(gòu)和加工技術(shù)多方面都發(fā)生了很多的改進(jìn),如同Gordon E. Moore老大哥預(yù)測的一樣,半導(dǎo)體器件的規(guī)格在不斷的縮小,芯片的集成度也在不斷提升,工藝制程從90nm

2020-12-10 06:55:40

業(yè)界對哪種半導(dǎo)體工藝最適合某一給定應(yīng)用存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-07-05 08:13:58

業(yè)界對哪種半導(dǎo)體工藝最適合某一給定應(yīng)用存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-20 08:01:20

半導(dǎo)體工藝講座ObjectiveAfter taking this course, you will able to? Use common semiconductor terminology

2009-11-18 11:31:10

半導(dǎo)體光刻蝕工藝

2021-02-05 09:41:23

,小米9pro,oppo Reno3以及vivo X30)分別采用了什么芯片? 3協(xié)同通信的方式有哪些? 4大數(shù)據(jù)及認(rèn)知無線電(名詞解釋) 4半導(dǎo)體工藝的4個主要步驟: 4簡敘半導(dǎo)體光刻技術(shù)基本原理 4給出4個全球著名的半導(dǎo)體設(shè)備制造商并指出其生產(chǎn)的設(shè)備核心技術(shù): 5衛(wèi)

2021-07-26 08:31:09

半導(dǎo)體制冷片是利用半導(dǎo)體材料的Peltier效應(yīng)而制作的電子元件,當(dāng)直流電通過兩種不同半導(dǎo)體材料串聯(lián)成的電偶時,在電偶的兩端即可分別吸收熱量和放出熱量,可以實(shí)現(xiàn)制冷的目的。它是一種產(chǎn)生負(fù)熱阻的制冷技術(shù),其特點(diǎn)是無運(yùn)動部件,可靠性也比較高。半導(dǎo)體制冷片的工作原理是什么?半導(dǎo)體制冷片有哪些優(yōu)缺點(diǎn)?

2021-02-24 09:24:02

在制造半導(dǎo)體器件時,為什么先將導(dǎo)電性能介于導(dǎo)體和絕緣體之間的硅或鍺制成本征半導(dǎo)體,使之導(dǎo)電性極差,然后再用擴(kuò)散工藝在本征半導(dǎo)體中摻入雜質(zhì)形成N型半導(dǎo)體或P型半導(dǎo)體改善其導(dǎo)電性?

2012-07-11 20:23:15

半導(dǎo)體制造是目前中國大陸半導(dǎo)體發(fā)展的最大瓶頸。電腦CPU、手機(jī)SOC/基帶等高端芯片,國內(nèi)已經(jīng)有替代,雖然性能與國際巨頭產(chǎn)品有差距,但是至少可以“將就著用”。而半導(dǎo)體制造是處于“0~1”的突破過程中

2020-09-02 18:02:47

半導(dǎo)體器件與工藝

2012-08-20 08:39:08

半導(dǎo)體基礎(chǔ)知識與晶體管工藝原理

2012-08-20 08:37:00

半導(dǎo)體失效分析項(xiàng)目介紹,主要包括點(diǎn)針工作站(Probe Station)、反應(yīng)離子刻蝕(RIE)、微漏電偵測系統(tǒng)(EMMI)、X-Ray檢測,缺陷切割觀察系統(tǒng)(FIB系統(tǒng))等檢測試驗(yàn)。

2020-11-26 13:58:28

半導(dǎo)體材料半導(dǎo)體的功能分類集成電路的四大類

2021-02-24 07:52:52

大家好! 附件是半導(dǎo)體引線鍵合清洗工藝方案,請參考,謝謝!有問題聯(lián)系我:*** szldqxy@163.com

2010-04-22 12:27:32

請教下以前的[半導(dǎo)體技術(shù)天地]哪里去了

2020-08-04 17:03:41

半導(dǎo)體材料從發(fā)現(xiàn)到發(fā)展,從使用到創(chuàng)新,擁有這一段長久的歷史。宰二十世紀(jì)初,就曾出現(xiàn)過點(diǎn)接觸礦石檢波器。1930年,氧化亞銅整流器制造成功并得到廣泛應(yīng)用,是半導(dǎo)體材料開始受到重視。1947年鍺點(diǎn)接觸三極管制成,成為半導(dǎo)體的研究成果的重大突破。

2020-04-08 09:00:15

蘇州晶淼半導(dǎo)體設(shè)備有限公司致力于向客戶提供濕法制程刻蝕設(shè)備、清洗設(shè)備、高端PP/PVC通風(fēng)柜/廚、CDS化學(xué)品集中供液系統(tǒng)等一站式解決方案。我們的產(chǎn)品廣泛應(yīng)用與微電子、半導(dǎo)體、光伏、光通信、LED等

2016-09-06 13:53:08

,半導(dǎo)體的重要性都是非常巨大的。大部分的電子產(chǎn)品,如計(jì)算機(jī)、移動電話或是數(shù)字錄音機(jī)當(dāng)中的核心單元都和半導(dǎo)體有著極為密切的關(guān)聯(lián)。集成電路是一種微型電子器件或部件,采用一定的工藝,把一個電路中所需的晶體管

2021-09-15 07:24:56

國際半導(dǎo)體芯片巨頭壟斷加劇半導(dǎo)體芯片產(chǎn)業(yè)呈現(xiàn)三大趨勢

2021-02-04 07:26:49

半導(dǎo)體是什么?芯片又是什么?半導(dǎo)體芯片是什么?半導(dǎo)體芯片內(nèi)部結(jié)構(gòu)是由哪些部分組成的?

2021-07-29 09:18:55

` 誰來闡述一下半導(dǎo)體集成電路是什么?`

2020-03-24 17:12:08

工藝流程 半導(dǎo)體純水的工藝大致分成以下幾種: 1、采用離子交換方式,其流程如下:自來水→電動閥→多介質(zhì)過濾器→活性炭過濾器→軟化水器→中間水箱→低壓泵→精密過濾器→陽樹脂床→陰樹脂床→陰陽樹脂混合床

2013-08-12 16:52:42

本帖最后由 eehome 于 2013-1-5 09:53 編輯

簡述進(jìn)局光纜成端安裝工藝及要求?

2011-10-16 20:30:14

控制;控制圖 中圖分類號:TN301 文獻(xiàn)標(biāo)識碼: A 文章編號:1003-353X(2004)03-0058-03 1 前言 近年來,半導(dǎo)體制造技術(shù)經(jīng)歷了快速的改變,技術(shù)的提升也相對地增加了工藝過程

2018-08-29 10:28:14

30 dBm,增益大于5 dB。關(guān)鍵詞:碳化硅;金屬?半導(dǎo)體場效應(yīng)晶體管;犧牲氧化;干法刻蝕;等平面工藝

2009-10-06 09:48:48

一個比較經(jīng)典的半導(dǎo)體工藝制作的課件,英文的,供交流……

2012-02-26 13:12:24

`《半導(dǎo)體制造工藝》學(xué)習(xí)筆記`

2012-08-20 19:40:32

書籍:《炬豐科技-半導(dǎo)體工藝》文章:半導(dǎo)體行業(yè)的濕化學(xué)分析——總覽編號:JFSJ-21-075作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html對液體和溶液進(jìn)行

2021-07-09 11:30:18

之間移動的電子稱為帶隙能量。絕緣體、導(dǎo)體和半導(dǎo)體的導(dǎo)電性能可以從它們帶隙的不同來理解。圖 1 和圖 2 說明了摻雜劑如何影響半導(dǎo)體的電阻率/電導(dǎo)率。在圖 1 中,摻雜劑產(chǎn)生了一個空穴,因?yàn)樗鄙倥c四價(jià)

2021-07-01 09:38:40

書籍:《炬豐科技-半導(dǎo)體工藝》文章:CMOS 單元工藝編號:JFSJ-21-027作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html晶圓生產(chǎn)需要三個一般過程:硅

2021-07-06 09:32:40

受到贊賞,通常用于廢物處理和飲用水消毒行業(yè)。最近在半導(dǎo)體濕法清洗工藝中引入臭氧引起了越來越多的興趣,因?yàn)樵摷夹g(shù)通過滿足上述需求的許多方面已被證明對工業(yè)應(yīng)用非常有前景。如圖 1 中的電位-pH 圖所示

2021-07-06 09:36:27

書籍:《炬豐科技-半導(dǎo)體工藝》文章:GaN 基板的表面處理編號:JFSJ-21-077作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html關(guān)鍵詞: GaN 襯底

2021-07-07 10:26:01

書籍:《炬豐科技-半導(dǎo)體工藝》文章:GaN、ZnO和SiC的濕法化學(xué)蝕刻編號:JFKJ-21-830作者:炬豐科技摘要寬帶隙半導(dǎo)體具有許多特性,使其對高功率、高溫器件應(yīng)用具有吸引力。本文綜述了三種

2021-10-14 11:48:31

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:GaN的晶體濕化學(xué)蝕刻[/td][td]編號:JFSJ-21-0作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html 目前

2021-07-07 10:24:07

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:IC制造工藝編號:JFSJ-21-046作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html摘要:集成電路的制造主要包括以下工藝

2021-07-08 13:13:06

書籍:《炬豐科技-半導(dǎo)體工藝》文章:III-V族半導(dǎo)體納米線結(jié)構(gòu)的光子學(xué)特性編號:JFSJ-21-075作者:炬豐科技 摘要:III-V 族半導(dǎo)體納米線 (NW) 由于其沿納米線軸對電子和光子

2021-07-09 10:20:13

書籍:《炬豐科技-半導(dǎo)體工藝》文章:用于半導(dǎo)體封裝基板的化學(xué)鍍 Ni-P/Pd/Au編號:JFSJ-21-077作者:炬豐科技 隨著便攜式電子設(shè)備的普及,BGA(球柵陣列)越來越多地用于安裝在高密度

2021-07-09 10:29:30

新加坡知名半導(dǎo)體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設(shè)備主管!此職位為內(nèi)部推薦,深刻蝕工藝工程師需要有LAM 8寸機(jī)臺poly刻蝕經(jīng)驗(yàn)。刻蝕設(shè)備主管需要熟悉LAM8寸機(jī)臺。待遇優(yōu)厚。有興趣的朋友可以將簡歷發(fā)到我的郵箱sternice81@gmail.com,我會轉(zhuǎn)發(fā)給HR。

2017-04-29 14:23:25

哪種半導(dǎo)體工藝最適合某一指定應(yīng)用?對此,業(yè)界存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-02 08:23:59

1、GaAs半導(dǎo)體材料可以分為元素半導(dǎo)體和化合物半導(dǎo)體兩大類,元素半導(dǎo)體指硅、鍺單一元素形成的半導(dǎo)體,化合物指砷化鎵、磷化銦等化合物形成的半導(dǎo)體。砷化鎵的電子遷移速率比硅高5.7 倍,非常適合

2019-07-29 07:16:49

直接影響轉(zhuǎn)換器的體積、功率密度和成本。 然而,所使用的半導(dǎo)體開關(guān)遠(yuǎn)非理想,并且由于開關(guān)轉(zhuǎn)換期間電壓和電流之間的重疊而存在開關(guān)損耗。這些損耗對轉(zhuǎn)換器工作頻率造成了實(shí)際限制。諧振拓?fù)淇梢酝ㄟ^插入額外的電抗

2023-02-21 16:01:16

1、 電子、物理、通信、材料等專業(yè),本科以上學(xué)歷,3年以上的PECVD\LPCVD沉積工作經(jīng)驗(yàn); 2、 了解半導(dǎo)體工藝、精通PECVD或LPCVD材料生長技術(shù); 3、 精通PECVD或LPCVD設(shè)備

2012-12-19 22:42:16

今日分享晶圓制造過程中的工藝及運(yùn)用到的半導(dǎo)體設(shè)備。晶圓制造過程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴(kuò)散等。這幾個主要步驟都需要若干種半導(dǎo)體設(shè)備,滿足不同的需要。設(shè)備中應(yīng)用較為廣泛

2018-10-15 15:11:22

常用的功率半導(dǎo)體器件有哪些?

2021-11-02 07:13:30

變化。SiGeBiCMOS工藝技術(shù)幾乎與硅半導(dǎo)體超大規(guī)模集成電路(VLSI)行業(yè)中的所有新技術(shù)兼容,包括絕緣體硅(SOI)技術(shù)和溝道隔離技術(shù)。不過硅鍺要想取代砷化鎵的地位還需要繼續(xù)在擊穿電壓、截止頻率

2016-09-15 11:28:41

半導(dǎo)體封裝工程師發(fā)布日期2015-02-10工作地點(diǎn)北京-北京市學(xué)歷要求碩士工作經(jīng)驗(yàn)1~3年招聘人數(shù)1待遇水平面議年齡要求性別要求不限有效期2015-04-16職位描述1、半導(dǎo)體光電子學(xué)、微電子

2015-02-10 13:33:33

,以及在下面緊貼著抗蝕膜的一層硅。刻蝕(英語:etching)是半導(dǎo)體器件制造中利用化學(xué)途徑選擇性地移除沉積層特定部分的工藝。刻蝕對于器件的電學(xué)性能十分重要。如果刻蝕過程中出現(xiàn)失誤,將造成難以恢復(fù)

2017-10-09 19:41:52

問個菜的問題:半導(dǎo)體(或集成電路)工藝 來個人講講 半導(dǎo)體工藝 集成電路工藝 硅工藝 CMOS工藝的概念和區(qū)別以及聯(lián)系吧。查了一下:集成電路工藝(integrated

2009-09-16 11:51:34

電力半導(dǎo)體器件的分類

2019-09-19 09:01:01

芯片制造-半導(dǎo)體工藝制程實(shí)用教程學(xué)習(xí)筆記[/hide]

2009-11-18 11:44:51

;2、具體半導(dǎo)體光刻、鍍膜、化學(xué)清洗、刻蝕等工藝經(jīng)歷,具有相關(guān)半導(dǎo)體設(shè)備使用經(jīng)歷。任職條件: 1、大學(xué)本科學(xué)歷(含)以上, 理工科專業(yè);2、微電子學(xué)和固體電子學(xué)、物理、化學(xué)、半導(dǎo)體器件專業(yè)優(yōu)先考慮3

2016-10-26 17:05:04

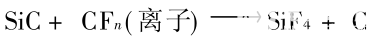

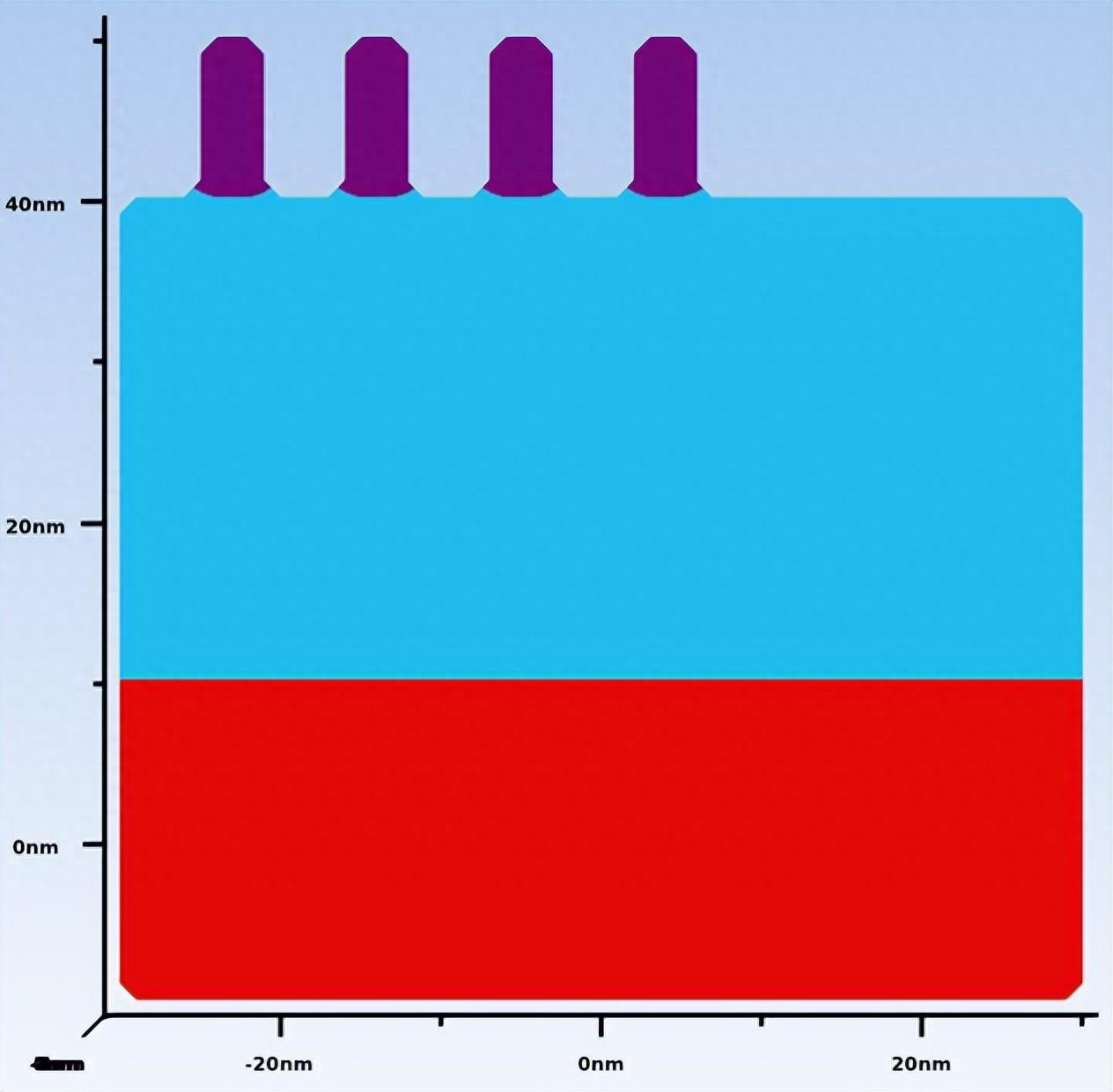

最近需要用到干法刻蝕技術(shù)去刻蝕碳化硅,采用的是ICP系列設(shè)備,刻蝕氣體使用的是SF6+O2,碳化硅上面沒有做任何掩膜,就是為了去除SiC表面損傷層達(dá)到表面改性的效果。但是實(shí)際刻蝕過程中總是會在碳化硅

2022-08-31 16:29:50

半導(dǎo)體材料是一類具有半導(dǎo)體性能(導(dǎo)電能力介于導(dǎo)體與絕緣體之間,電阻率約在1mΩ·cm~1GΩ·cm范圍內(nèi))、可用來制作半導(dǎo)體器件和集成電路的電子材料。按種類可以分為元素半導(dǎo)體和化合物半導(dǎo)體兩大類

2019-06-27 06:18:41

本文以金屬刻蝕去膠腔為背景,簡述干刻清洗工藝開發(fā)和評價(jià)過程。針對實(shí)際應(yīng)用中的問題,展開討論。通過實(shí)際案例分析,展示了干刻清洗工藝的應(yīng)用價(jià)值。關(guān)鍵字:干刻清

2009-12-14 11:06:10 16

16 半導(dǎo)體制造刻蝕設(shè)備調(diào)度算法的研究_賈小恒

2017-03-19 11:28:16 2

2 據(jù)浦東時報(bào)報(bào)道,2020年開年,中微半導(dǎo)體成功中標(biāo)長江存儲9臺刻蝕設(shè)備訂單。

2020-01-08 10:49:09 4292

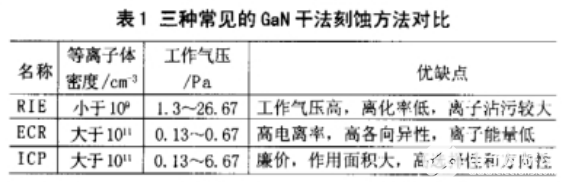

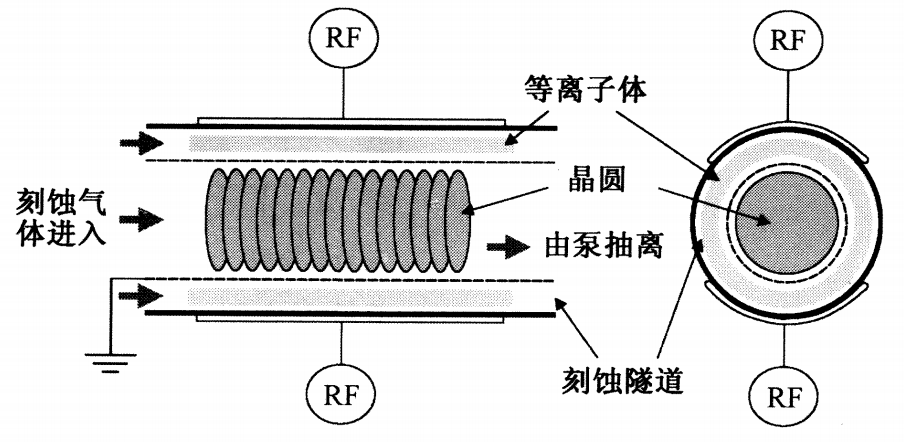

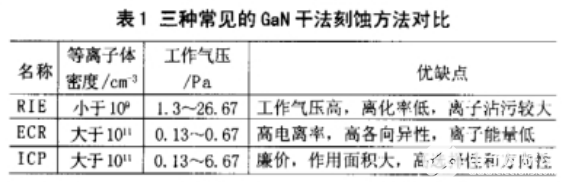

4292 摘要:對比了RIE,ECR,ICP等幾種GaN7干法刻蝕方法的特點(diǎn)。回顧了GaN1法刻蝕領(lǐng)域的研究進(jìn)展。以ICP刻蝕GaN和AIGaN材料為例,通過工藝參數(shù)的優(yōu)化,得到了高刻蝕速率和理想的選擇比及

2020-12-29 14:39:29 2909

2909

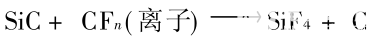

摘要:簡述了在SiC材料半導(dǎo)體器件制造工藝中,對SiC材料采用干法刻蝕工藝的必要性.總結(jié)了近年來SiC干法刻蝕技術(shù)的工藝發(fā)展?fàn)顩r. 半導(dǎo)體器件已廣泛應(yīng)用于各種場合,近年來其應(yīng)用領(lǐng)域已拓展至許多

2020-12-30 10:30:11 7638

7638

刻蝕是半導(dǎo)體制造中十分關(guān)鍵的一環(huán),刻蝕通過物理或化學(xué)方法將硅片表面不需要的材料去除,從而將掩膜圖形正確的復(fù)制到涂膠硅片上。

2021-02-23 16:41:57 3382

3382 半導(dǎo)體工藝化學(xué)原理。

2021-03-19 17:07:23 111

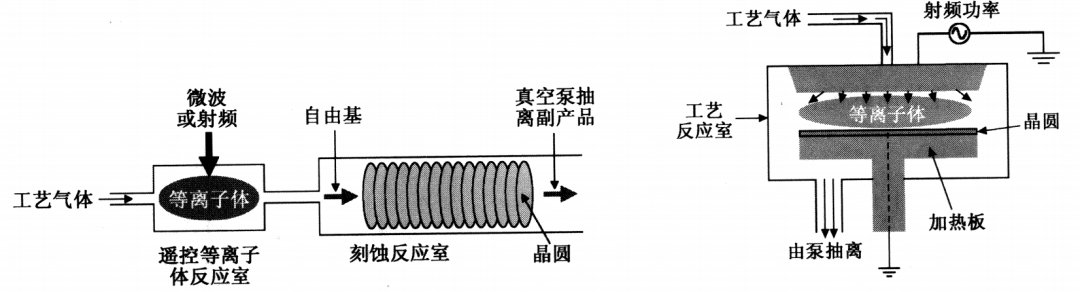

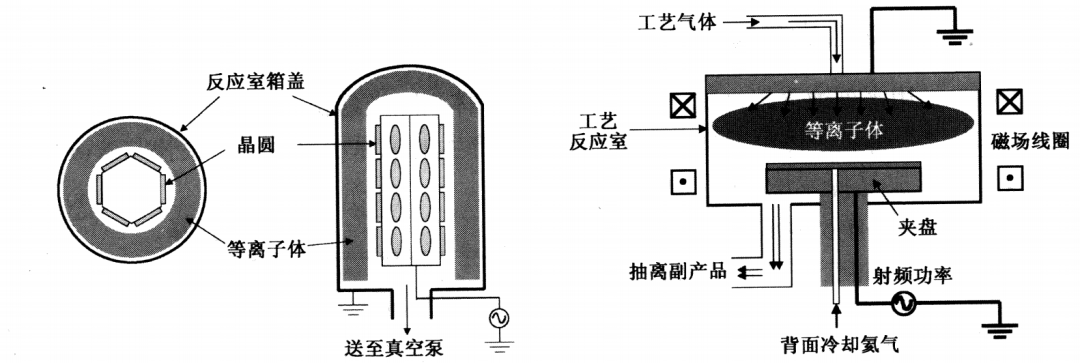

111 刻蝕室半導(dǎo)體IC制造中的至關(guān)重要的一道工藝,一般有干法刻蝕和濕法刻蝕兩種,干法刻蝕和濕法刻蝕一個顯著的區(qū)別是各向異性,更適合用于對形貌要求較高的工藝步驟。

2022-06-13 14:43:31 6

6 功率半導(dǎo)體分立器件的主要工藝流程包括:在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),進(jìn)行芯片封裝,對加工完畢的芯片進(jìn)行技術(shù)性能指標(biāo)測試,其中主要生產(chǎn)工藝有外延工藝、光刻工藝、刻蝕工藝、離子注入工藝和擴(kuò)散工藝等。

2023-02-24 15:34:13 3185

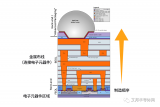

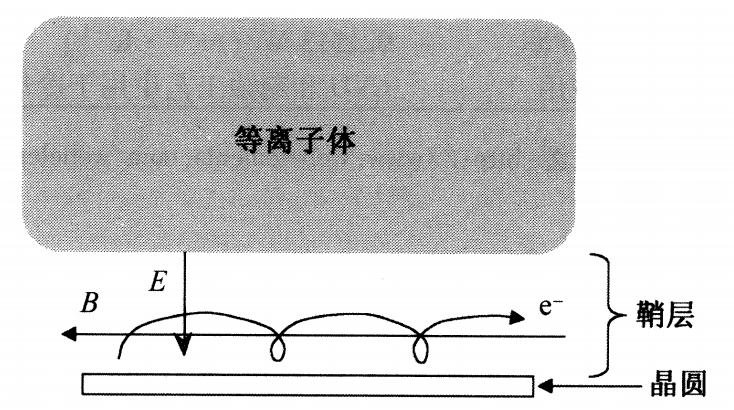

3185 嚴(yán)重的離子轟擊將產(chǎn)生大量的熱量,所以如果沒有適當(dāng)?shù)睦鋮s系統(tǒng),晶圓溫度就會提高。對于圖形化刻蝕,晶圓上涂有一層光刻膠薄膜作為圖形屏蔽層,如果晶圓溫度超過150攝氏度,屏蔽層就會被燒焦,而且化學(xué)刻蝕速率

2023-03-06 13:52:33 827

827 對于濕法刻蝕,大部分刻蝕的終點(diǎn)都取決于時間,而時間又取決于預(yù)先設(shè)定的刻蝕速率和所需的刻蝕厚度。由于缺少自動監(jiān)測終點(diǎn)的方法,所以通常由操作員目測終點(diǎn)。濕法刻蝕速率很容易受刻蝕劑溫度與濃度的影響,這種影響對不同工作站和不同批量均有差異,因此單獨(dú)用時間決定刻蝕終點(diǎn)很困難,一般釆用操作員目測的方式。

2023-03-06 13:56:03 1773

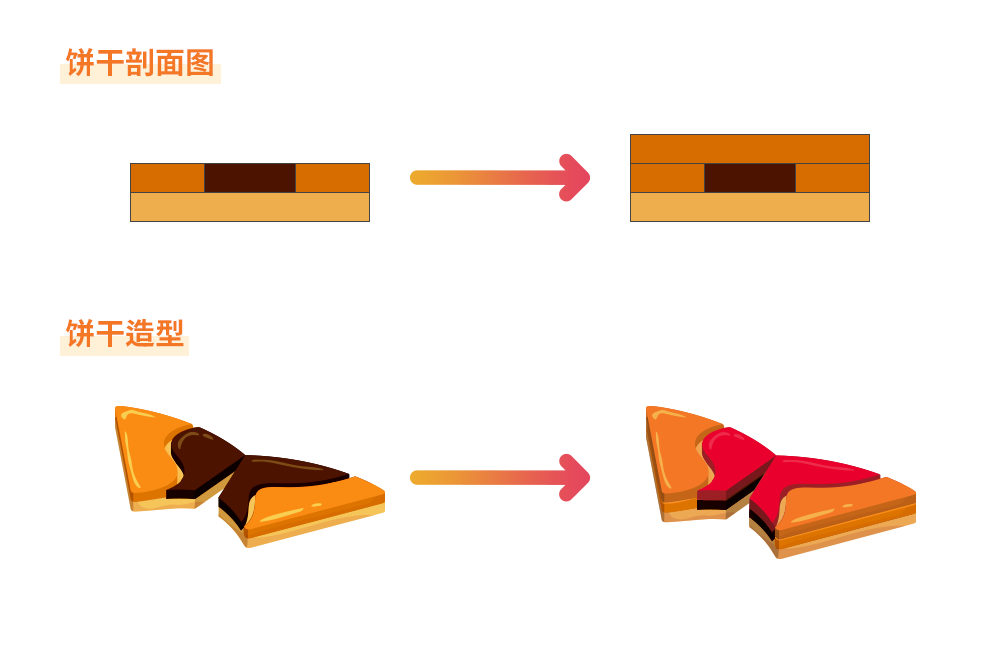

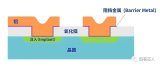

1773 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2200

2200 金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時鋁中如果 有少量銅就會引起殘余物問題,因?yàn)镃u Cl2的揮發(fā)性極低且會停留在晶圓表面。

2023-04-10 09:40:54 2330

2330 壓力主要控制刻蝕均勻性和刻蝕輪廓,同時也能影響刻蝕速率和選擇性。改變壓力會改變電子和離子的平均自由程(MFP),進(jìn)而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 1922

1922 等離子體均勻性和等離子體位置的控制在未來更加重要。對于成熟的技術(shù)節(jié)點(diǎn),高的產(chǎn)量、低的成本是與現(xiàn)有生產(chǎn)系統(tǒng)競爭的關(guān)鍵因素。如果可以制造低成本的可靠的刻蝕系統(tǒng),從長遠(yuǎn)來看,可以為客戶節(jié)省大量費(fèi)用,有可能

2023-04-21 09:20:22 1351

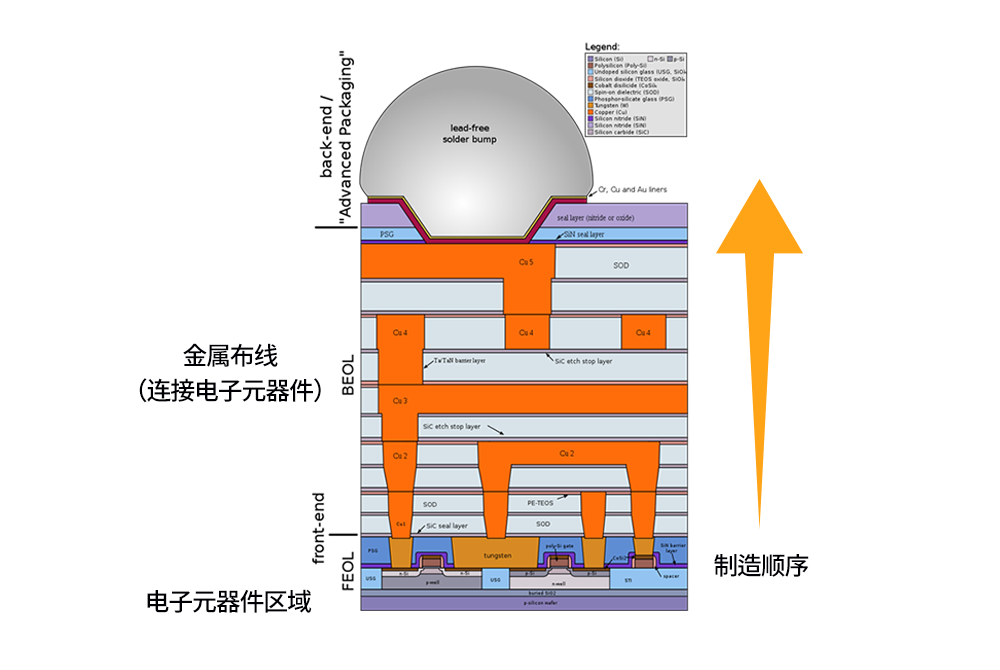

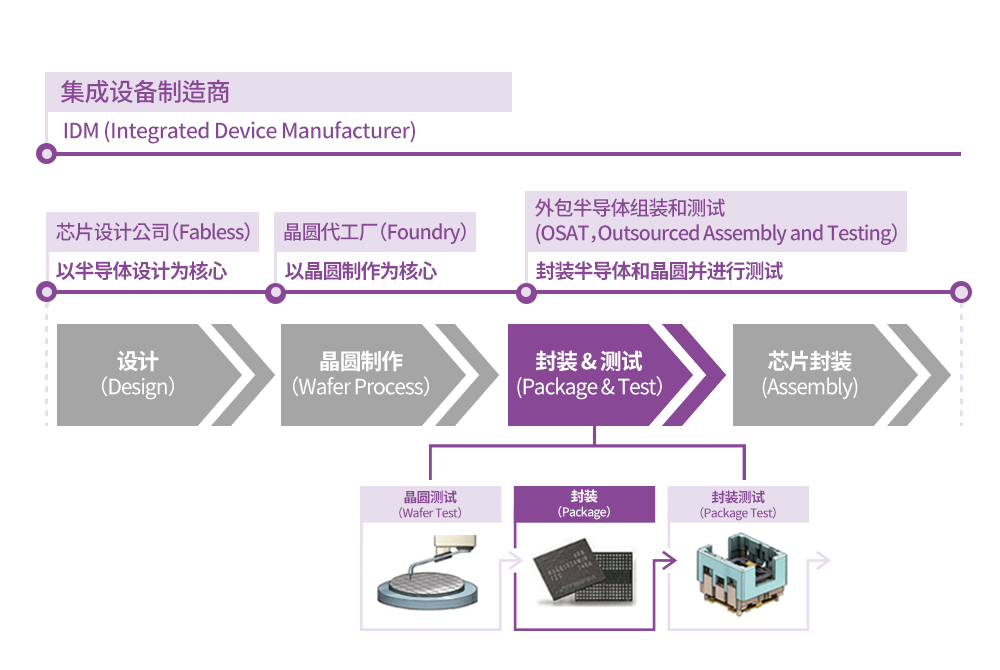

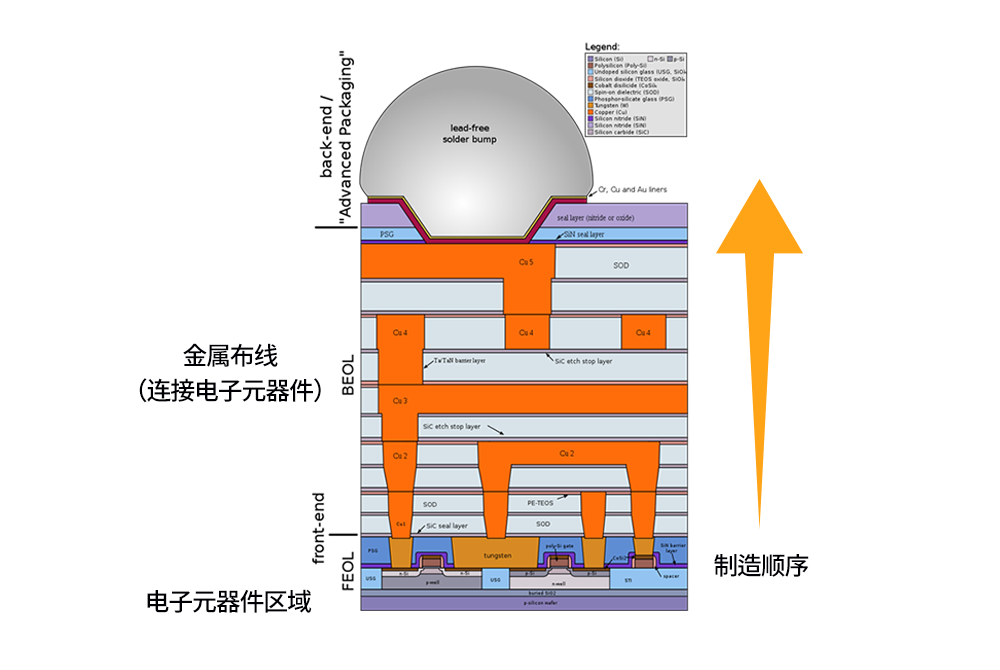

1351 本篇要講的金屬布線工藝,與前面提到的光刻、刻蝕、沉積等獨(dú)立的工藝不同。在半導(dǎo)體制程中,光刻、刻蝕等工藝,其實(shí)是為了金屬布線才進(jìn)行的。在金屬布線過程中,會采用很多與之前的電子元器件層性質(zhì)不同的配線材料(金屬)。

2023-04-25 10:38:49 986

986

經(jīng)過氧化、光刻、刻蝕、沉積等工藝,晶圓表面會形成各種半導(dǎo)體元件。半導(dǎo)體制造商會讓晶圓表面布滿晶體管和電容(Capacitor);

2023-04-28 10:04:52 532

532

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1074

1074

在半導(dǎo)體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創(chuàng)建所需的微細(xì)圖案。半導(dǎo)體“刻蝕”工藝所采用的氣體和設(shè)備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1181

1181

Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉(zhuǎn)為干法刻蝕,因此所需的設(shè)備和工藝更加復(fù)雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數(shù)出現(xiàn)波動,從而刻蝕工藝與光刻工藝成為半導(dǎo)體制造的重要工藝流程之一。

2023-06-26 09:20:10 816

816

在前幾篇文章(點(diǎn)擊查看),我們一直在借用餅干烘焙過程來形象地說明半導(dǎo)體制程 。在上一篇我們說到,為制作巧克力夾心,需通過“刻蝕工藝”挖出餅干的中間部分,然后倒入巧克力糖漿,再蓋上一層餅干層。“倒入巧克力糖漿”和“蓋上餅干層”的過程在半導(dǎo)體制程中就相當(dāng)于“沉積工藝”。

2023-06-29 16:56:17 830

830

半導(dǎo)體同時具有“導(dǎo)體”的特性,因此允許電流通過,而絕緣體則不允許電流通過。離子注入工藝將雜質(zhì)添加到純硅中,使其具有導(dǎo)電性能。我們可以根據(jù)實(shí)際需要使半導(dǎo)體導(dǎo)電或絕緣。 重復(fù)光刻、刻蝕和離子注入步驟會在

2023-07-03 10:21:57 2170

2170

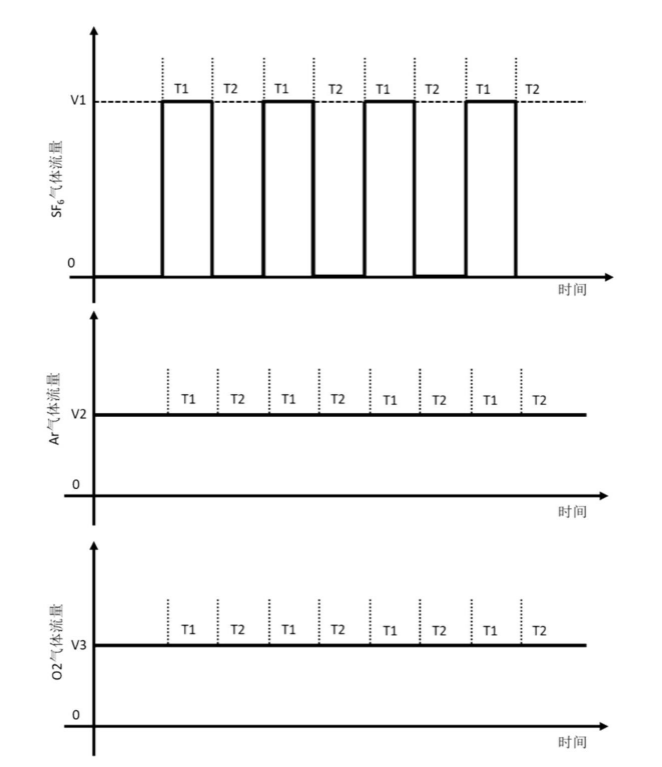

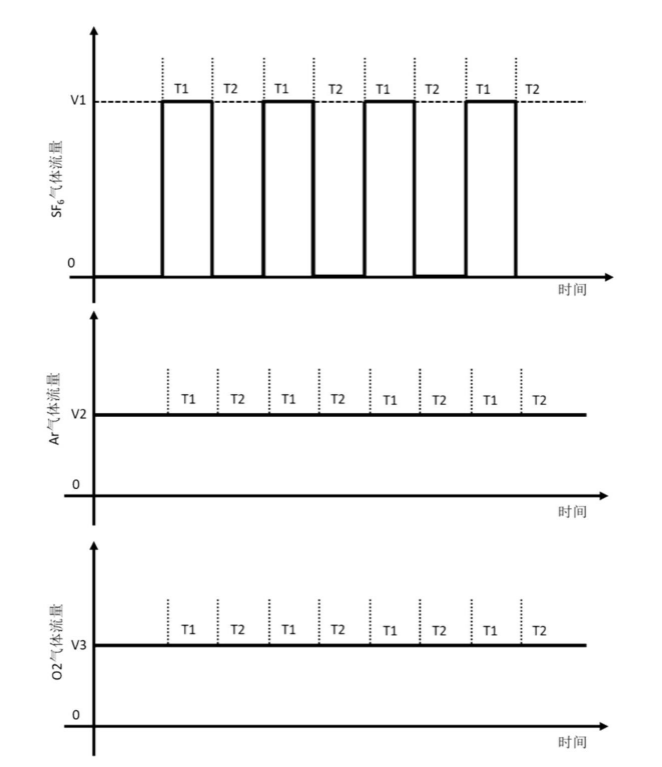

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環(huán)刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3214

3214

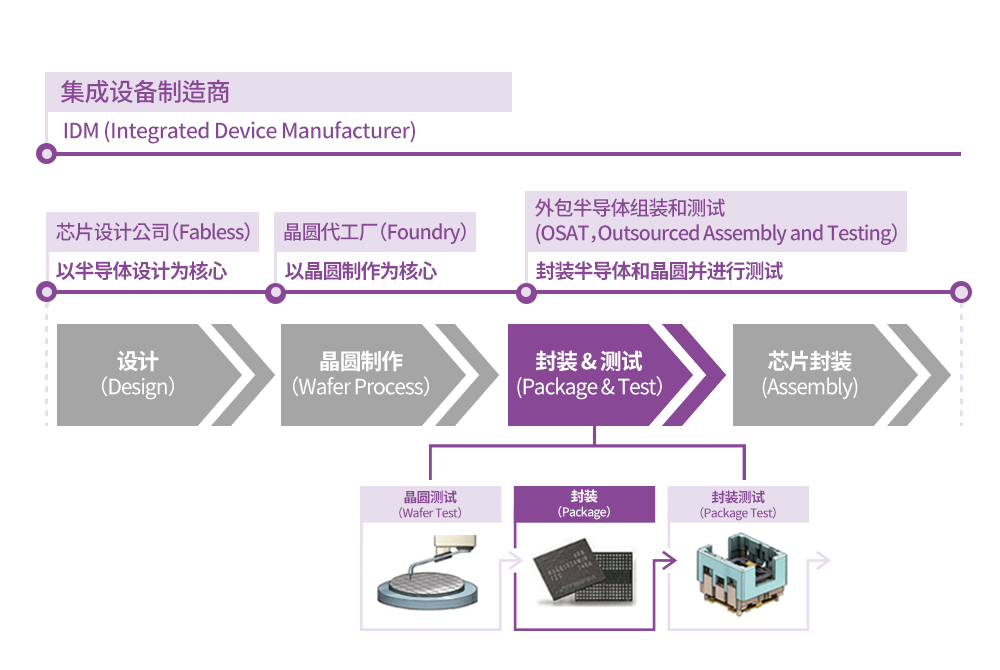

【半導(dǎo)體后端工藝:】第一篇了解半導(dǎo)體測試

2023-11-24 16:11:50 485

485

半導(dǎo)體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創(chuàng)建所需圖形

2023-11-27 16:54:26 256

256

[半導(dǎo)體前端工藝:第二篇] 半導(dǎo)體制程工藝概覽與氧化

2023-11-29 15:14:34 541

541

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負(fù)載效應(yīng),避免產(chǎn)生凹坑,并使用對TiN有高選擇比的化學(xué)氣體進(jìn)行刻蝕。

2023-12-06 09:38:53 1538

1538 該專利詳細(xì)闡述了一種針對含硅有機(jī)介電層的高效刻蝕方法及相應(yīng)的半導(dǎo)體工藝設(shè)備。它主要涉及到通過交替運(yùn)用至少兩個刻蝕步驟來刻蝕含硅有機(jī)介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

智程半導(dǎo)體自2009年起致力于半導(dǎo)體濕法工藝設(shè)備研究、生產(chǎn)與銷售事業(yè),10余載研發(fā)歷程,使得其已成為全球頂尖的半導(dǎo)體濕法設(shè)備供應(yīng)商。業(yè)務(wù)范圍包括清洗、去膠、濕法刻蝕、電鍍、涂膠顯影、金屬剝離等多種設(shè)備,廣泛應(yīng)用于各種高尖端產(chǎn)品領(lǐng)域。

2024-01-12 14:55:23 637

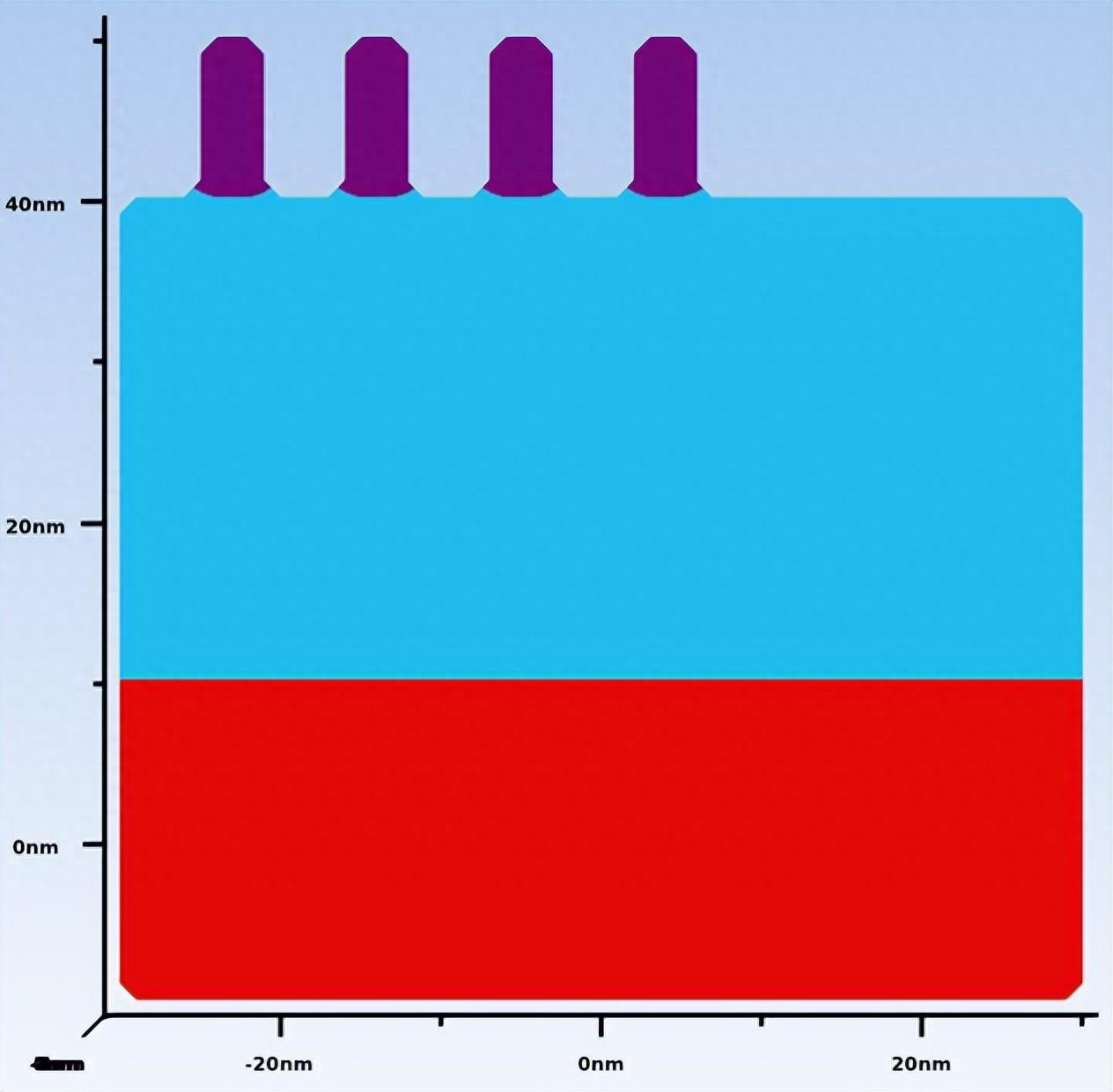

637 使用SEMulator3D?工藝步驟進(jìn)行刻蝕終點(diǎn)探測 作者:泛林集團(tuán) Semiverse Solutions 部門軟件應(yīng)用工程師 Pradeep Nanja 介紹 半導(dǎo)體行業(yè)一直專注于使用先進(jìn)的刻蝕

2024-01-19 16:02:42 130

130

電子發(fā)燒友App

電子發(fā)燒友App

評論