1. Chiplet:延續(xù)摩爾定律,規(guī)模化落地可期

1.1. Chiplet 綜合優(yōu)勢明顯,有效延續(xù)摩爾定律

摩爾定律實現(xiàn)的維度主要分為制造、設(shè)計、封裝三方面。在制造方面, 主要通過晶體管微縮工藝實現(xiàn),從 130nm 逐步向 5nm 甚至是 2nm 邁進(jìn); 在設(shè)計方面,主要通過各種架構(gòu)演進(jìn)、方案設(shè)計等方式實現(xiàn);在封裝方 面,主要通過不同模塊的異質(zhì)集成來實現(xiàn),通過 SiP、WLP 等方法不斷 提高系統(tǒng)化的集成密度。

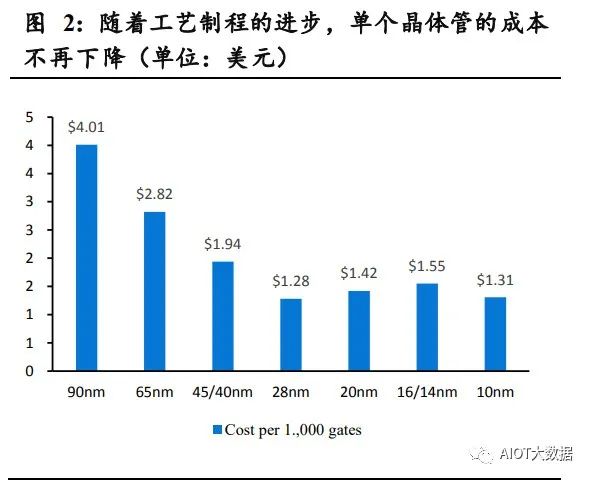

摩爾定律在制造端的提升已經(jīng)逼近極限,開始逐步將重心轉(zhuǎn)向封裝端和 設(shè)計端。隨著 AI、數(shù)字經(jīng)濟(jì)等應(yīng)用場景的爆發(fā),對算力的需求更加旺盛, 芯片的性能要求也在不斷提高,業(yè)界芯片的制造工藝從 28nm 向 7nm 以 下發(fā)展,TSMC 甚至已經(jīng)有了 2nm 芯片的風(fēng)險量產(chǎn)規(guī)劃。但隨著線寬逐 步逼近原子級別,工藝制程升級帶來的性能、功耗提升的性價比越來越 低,封裝端和設(shè)計端維度的提升開始逐步進(jìn)入視野。

Chiplet 方案正是一種通過在封裝端和設(shè)計端的提升,來進(jìn)一步提升芯 片的集成化密度,從而延續(xù)摩爾定律的新型半導(dǎo)體技術(shù)方案。其方案核 心主要包含三個概念,分別是小芯粒、異構(gòu)異質(zhì)和系統(tǒng)級集成。 1)小芯粒:原有 SoC 芯片由各種 IP 內(nèi)核設(shè)計組成,小芯粒即在設(shè)計端 將各種 IP 單個拆分,進(jìn)行芯片化。 2)異構(gòu)異質(zhì):將類似 CPU、GPU、DRAM 等不同結(jié)構(gòu)工藝材質(zhì)的芯 片合在一起,從而減少傳輸延遲、提高集成度。 3)系統(tǒng)級集成:在前兩者的基礎(chǔ)上,通過軟件設(shè)計系統(tǒng)級高密度的方 案,利用各種堆疊封裝技術(shù),將更多的異構(gòu)異質(zhì)的小芯片進(jìn)行高密度封 裝集成,從而實現(xiàn)良率、成本、性能、商業(yè)風(fēng)險等方面的綜合提升。

Chiplet 方案通過將芯片性能的提升和工藝適度解耦合,能夠利用先進(jìn) 封裝技術(shù)實現(xiàn)綜合性能的提升,其主要原因如下:

①小芯片優(yōu)化成本:將芯片分解成特定的模塊,這可以使單個芯片面積 更小并可選擇最合適的工藝,從而提高良率、降低制造成本和門檻。 在降低成本方面:當(dāng)切割芯片的面積越小,綠色芯片的數(shù) 量就越多,整體晶圓中可用的芯片面積就越大,單位面積芯片的成本就 越低。另外,硅片化 IP 的復(fù)用,也可以顯著降低成本。 在提高良率方面:晶圓中存在各種缺陷,當(dāng)芯片的面積越大,它受影響 的芯片數(shù)量比例就越大。例如,一塊晶圓中切割 3 片芯片, 有一片受到缺陷影響,良率為 2/3;當(dāng)一塊晶圓切割 25 片芯片,缺陷影 響了 3 片芯片,良率為 22/25,整體良率大于 2/3。 在降低門檻方面:小芯片化后,不同的芯片可以采用最合適的工藝和架 構(gòu)進(jìn)行設(shè)計制造。例如 I/O die 因為更加先進(jìn)的工藝對其性能的提升有限, 可以采用 12nm 工藝進(jìn)行設(shè)計制造,CPU die 因為對先進(jìn)工藝要求更高, 可以采用 7nm/5nm 工藝進(jìn)行設(shè)計制造。整體無需像 SoC 一樣,I/O 和 CPU 的 IP 都必須采用最先進(jìn)的工藝設(shè)計制造。

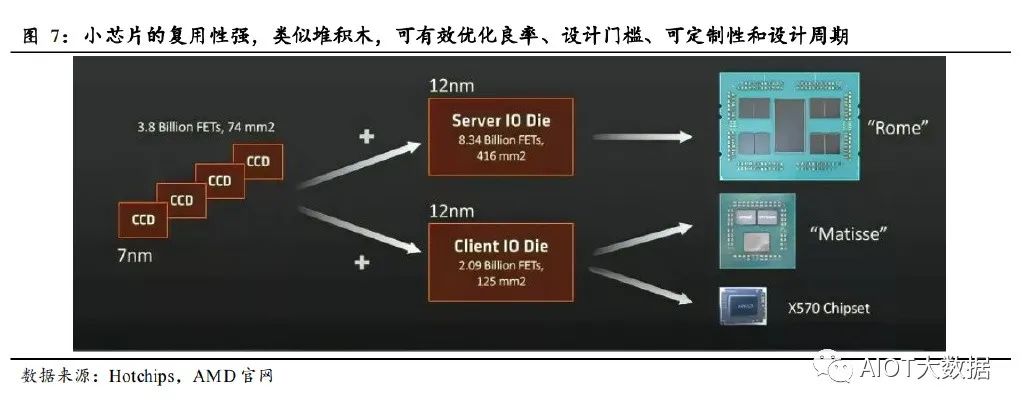

②小芯片復(fù)用性強(qiáng):小芯片可視為固定模塊,在不同的產(chǎn)品中根據(jù)需求 進(jìn)行組裝復(fù)用,類似樂高積木,具有極強(qiáng)的靈活性。通過小芯片化甚至 最理想的 IP 芯片化,不僅可以減少芯片的設(shè)計周期,加快迭代速度,還 可以提高芯片的可定制性。 以 AMD 的系列產(chǎn)品為例,將處理器芯片進(jìn)行解耦合,分成單個 CCD (Core Chiplet Die)芯片和一個 I/O die,CCD 和 I/O 核之間采用第二代 Infinity Fabric 總線連接。其中 CCD 采用 7nm 工藝,I/O 核采用 12nm 工 藝。8 個 CCD 和 1 個 Server I/O die 可組裝成 EPYC Rome(霄龍)服務(wù) 器處理器;8 個 CCD 和 1 個 Client I/O die 可組裝成 Ryzen (銳龍)3000 系列(代號 Matisse)桌面服務(wù)器;AMD 的 X570 Chipset 也可用現(xiàn)有的 小芯片進(jìn)行組裝設(shè)計。 這種固定模塊的小芯片方式,多個小芯片無需重復(fù)設(shè)計,具有復(fù)用價值, 而且芯片可采用最合適的工藝制程,可有效提高良率以及降低設(shè)計門檻。 在可定制性、設(shè)計周期方面、降低成本,進(jìn)行極大優(yōu)化。

③小芯片可高度集成化:小芯片利用芯片互連技術(shù)和高密度封裝技術(shù)可 輕易集成多核,滿足高效能運算處理器的需求。單片 SoC 的方案,在集 成多核方案時,受制于可用的光罩尺寸、良率等問題,芯片面積最多只 能達(dá)到 800mm2。Chiplet 核心計算單元可從 16 核堆積到 64 核,甚至 96 核以上。另外,對于內(nèi)存和 Cache 方面,也能實現(xiàn)高密度集成,從而實現(xiàn)更低的延遲或者更高的并行運算速度。

1.2. 整體生態(tài)處于早期,有望加速落地

Chiplet 方案主要由三大環(huán)節(jié)組成,分別是拆、合、封。 1)在“拆”的環(huán)節(jié):將原有多個 IP 組成的 SoC 大芯片進(jìn)行拆分,形成 多個不同的 CPU、I/O 等小芯片。拆解后的小芯片可以采用更加適配的 工藝節(jié)點和材質(zhì)。其中架構(gòu)設(shè)計是關(guān)鍵,需要考慮訪問頻率、緩存一致 性等各問題。 2)在“合”的環(huán)節(jié):將不同的小芯片利用內(nèi)部總線互連技術(shù)進(jìn)行電路 連接,各個電路互相組合,在功耗、通信延遲、帶寬等方面達(dá)到最優(yōu)的 效果。與 SoC 不同的是,前者是芯片間的互連,而后者是 IP 內(nèi)核間的 互連。 3)在“封”的環(huán)節(jié):將組合后的不同的芯片,利用 RDL、TSV、硅轉(zhuǎn) 接板、晶圓等高密度集成的先進(jìn)封裝技術(shù),進(jìn)行組合。

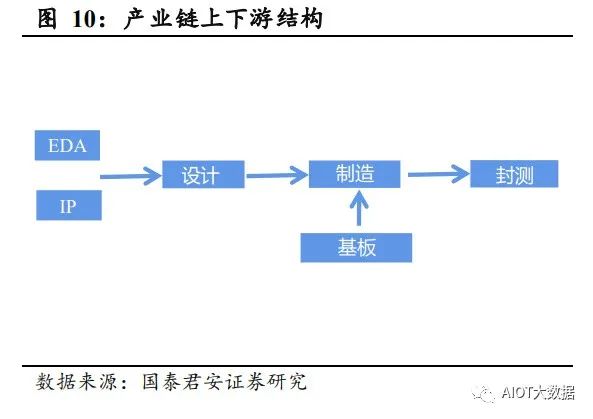

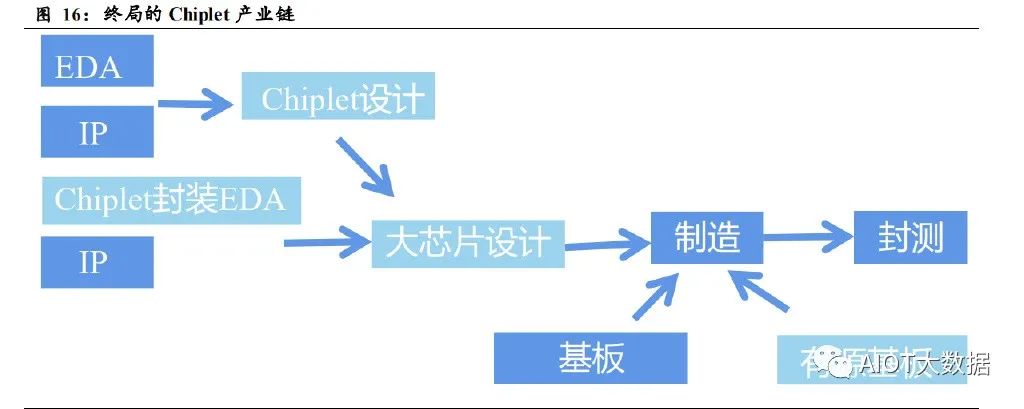

Chiplet 方案的實現(xiàn)包括 Chiplet 的設(shè)計制造和連接側(cè)的互連制造。依據(jù) 主要的產(chǎn)業(yè)鏈制造順序而言: 在設(shè)計端:利用 EDA 和 IP 核進(jìn)行分割后的 Chiplet 的設(shè)計、連接側(cè)包括 硅轉(zhuǎn)接板或者 RDL 層的互連建模,之后兩者協(xié)同仿真,得到完整的封 裝方案的模型。針對該模型依次進(jìn)行時序分析、電源網(wǎng)絡(luò)分析、可靠性 分析以及 PPA 優(yōu)化分析等,從而實現(xiàn) Chiplet 和連接側(cè)結(jié)合的系統(tǒng)性方 案。 在封裝端:利用晶圓廠制造完成的 Chiplet 與連接側(cè)方案進(jìn)行連接,以 2.5D 的硅轉(zhuǎn)接板為例,將 Chiplet 和進(jìn)行 TSV 打孔的硅轉(zhuǎn)接板相連,利 用硅轉(zhuǎn)接板內(nèi)部的 RDL 層進(jìn)行各個 Chiplet 之間的互連,最后將硅轉(zhuǎn)接 板與基板進(jìn)行連接,即完成整體 Chiplet 系統(tǒng)性方案的制造。 上述在設(shè)計端和封裝端的步驟,剛好對應(yīng)拆、合、封三大環(huán)節(jié)。

Chiplet 方案目前無法規(guī)模化落地的主要技術(shù)難點:

一、Chiplet 的統(tǒng)一接口和標(biāo)準(zhǔn)

考慮到互連是 Chiplet 的核心之一,互連接口與協(xié)議的落地和推行是實 現(xiàn)技術(shù)標(biāo)準(zhǔn)化和產(chǎn)品規(guī)模化的關(guān)鍵。2022 年 3 月,Intel、AMD、ARM、 臺積電、日月光等巨頭成立 Chiplet 標(biāo)準(zhǔn)聯(lián)盟,制定了通用 Chiplet 的高 速互聯(lián)標(biāo)準(zhǔn) UCI(e Universal Chiplet Interconnect express)。2021 年 5 月, CCITA(中國計算機(jī)互連技術(shù)聯(lián)盟)針對 Chiplet 標(biāo)準(zhǔn)《小芯片接口總線 技術(shù)要求》展開標(biāo)準(zhǔn)制定工作,集結(jié)了國內(nèi)產(chǎn)業(yè)鏈 60 多家單位共同參 與研究。 Chiplet 總線互連接口與協(xié)議可以劃分為物理層(PHY 層)、數(shù)據(jù)鏈路層、 網(wǎng)絡(luò)層以及傳輸層。數(shù)據(jù)鏈路層及以上的其他接口更多依賴沿用或擴(kuò)展 已有接口標(biāo)準(zhǔn)及協(xié)議。最重要的是物理層的接口研究,因為它與工藝、 功耗和性能等息息相關(guān)。物理層主要分為串行和并行兩種數(shù)據(jù)通信技術(shù), 串行主要分為串行器和解串器 SerDes,并行則包括低電壓封裝互連 LIPINCON 技術(shù)(TSMC 提出)、AIB 高級接口總線(Intel 提出)以及信 號引線物理互連 BoW 技術(shù)(OCP 提出)等。

互連是技術(shù)標(biāo)準(zhǔn)化的重點之一,但芯片間互連協(xié)議的標(biāo)準(zhǔn)化方面仍處于 發(fā)展演進(jìn)階段,相互競爭的標(biāo)準(zhǔn)較多。包括 CXL、CCIX、NVLink 等標(biāo) 準(zhǔn),都已經(jīng)在復(fù)雜的處理器芯片中得到應(yīng)用。其中雖然 CXL 發(fā)布較晚, 但因為 Intel 的業(yè)內(nèi)影響力和產(chǎn)品效應(yīng),大多數(shù)廠商紛紛跟隨并采納,技 術(shù)發(fā)展較快。國內(nèi)以 CCITA 為主導(dǎo)的技術(shù)聯(lián)盟正在進(jìn)行相關(guān)技術(shù)和標(biāo)準(zhǔn) 的研發(fā)中。相關(guān)國內(nèi)公司例如超摩科技也已經(jīng)宣布量產(chǎn) Chiplet 互聯(lián) IP 整體解決方案 CLCI,其協(xié)議標(biāo)準(zhǔn)主要采用自有方案,未來會考慮協(xié)議 間的兼容性。

二、EDA 工具鏈和生態(tài)系統(tǒng)的完整性、可持續(xù)性

新的 EDA 工具鏈?zhǔn)羌鼻行枰模渲饕驗椋?1) 小芯片之間更密集的互連+Chiplet 封裝 EDA 的更高要求 Chiplet 方案將芯片進(jìn)行精細(xì)化切割,并進(jìn)行更為密集的互連,例如 HBM 的芯片間的互連位寬為 1028bit,從而使其整體性能達(dá)到接近甚至超過 SoC 內(nèi)部的傳輸效率。對于 Chiplet 的封裝,也需要進(jìn)行額外的 EDA 設(shè) 計,這些都對 EDA 工具提出了更高的要求。 2) 系統(tǒng)性方案帶來的更嚴(yán)苛的可靠性挑戰(zhàn) Chiplet 方案作為一個整體的系統(tǒng)性方案,對熱效應(yīng)、電磁挑戰(zhàn)、電容耦 合、電感耦合、信號完整性等方面都提出了全新的要求,需要進(jìn)行針對 性的仿真建模,這是原有主要針對SoC芯片的EDA工具相對薄弱的點。 當(dāng)?shù)谌?Chiplet 開始被采用時,對于完整系統(tǒng)的可靠性要求將會更高。 第一種挑戰(zhàn)可能可以采用 Cadence 等工具組合設(shè)計,但針對于第二種可 靠性調(diào)整,則需要進(jìn)行針對性優(yōu)化升級。 考慮到無論是 EDA 工具鏈還是之前的協(xié)議標(biāo)準(zhǔn)抑或是制造封裝技術(shù)都 處于發(fā)展初期,為了實現(xiàn)有效的正反饋優(yōu)化,將終端的測試糾錯信息及時反饋到上游的 EDA、設(shè)計端并進(jìn)行改進(jìn),構(gòu)建一個完整的、可持續(xù) 的生態(tài)系統(tǒng)是極其重要的。

三、核心封裝技術(shù)的選擇

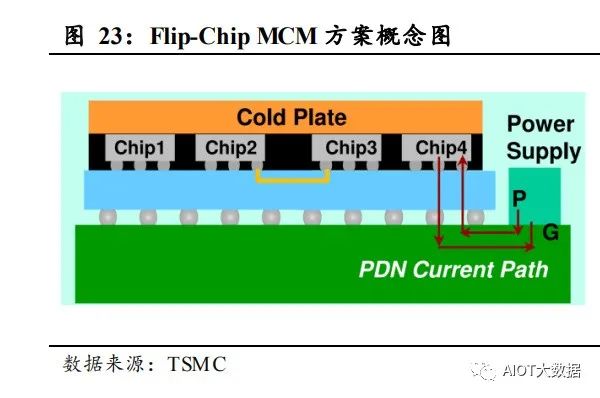

Chiplet 方案對應(yīng)的封裝技術(shù)包括 2D 的 MCM、2.1D 的 RDL 方案、2.5D 的 CoWoS 和 3D 的 HBM 等多種技術(shù),需要根據(jù)功耗、性能、成本等多 方面進(jìn)行綜合考慮。(基于 PAA的芯片評價體系+實現(xiàn)系統(tǒng)效率最大化) 1)2D 的 MCM/WLCSP 技術(shù)屬于典型的封裝技術(shù),將多個不同的芯片 在基板上進(jìn)行集成,屬于成本低復(fù)雜度低,但能有效增加管腳數(shù)量,提 高芯片集成密度的方案,在 AMD、國內(nèi)諸如超摩科技等多種產(chǎn)品中使 用,是當(dāng)前較為主流的方案。 2)InFO 技術(shù)屬于 2.1D 方案,介于 MCM 和 2.5D 的 CoWoS 之間,利用 RDL 層進(jìn)行集成,線間距接近 2 微米,引腳數(shù)量約 2500 個,多用于手 機(jī)和 IoT 中,蘋果最新的 M1 等芯片就是采用該方案。 3)2.5D 和 3D 技術(shù)可以在前兩者的基礎(chǔ)上,利用硅轉(zhuǎn)接板等就技術(shù)極強(qiáng) 地增大管腳數(shù)量和集成密度,例如 2.5D 的方案相較于 InFO 方案,線間 距減小到 0.4 微米,引腳數(shù)量增加到 4000 個,是 InFO 方案的 1.6 倍, 但由于成本過高,多用于云計算、HPC、數(shù)據(jù)中心中。

Chiplet 方案中多芯片集成的封裝方案存在散熱的功耗問題、硅轉(zhuǎn)接板 等封裝材料太貴的成本問題、復(fù)雜度過高的可靠性問題,并非適用于所 有工藝節(jié)點,也并非適用于所有下游應(yīng)用,更多時候作為先進(jìn)工藝制程 遇到門檻時的一種實現(xiàn)摩爾定律的延伸方案。關(guān)于成本最優(yōu)化的探討可 參考第二章 2.2 的探討。

四、產(chǎn)品測試的復(fù)雜性

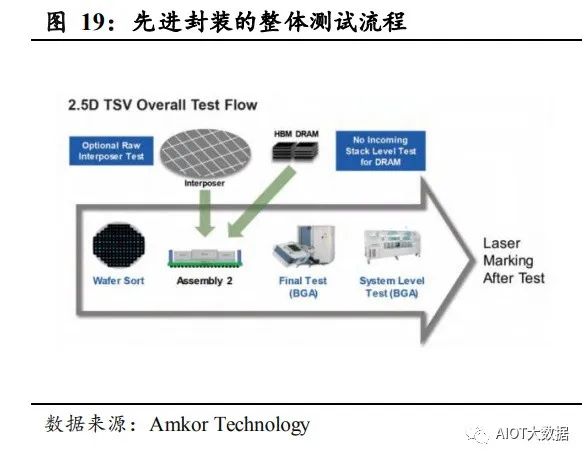

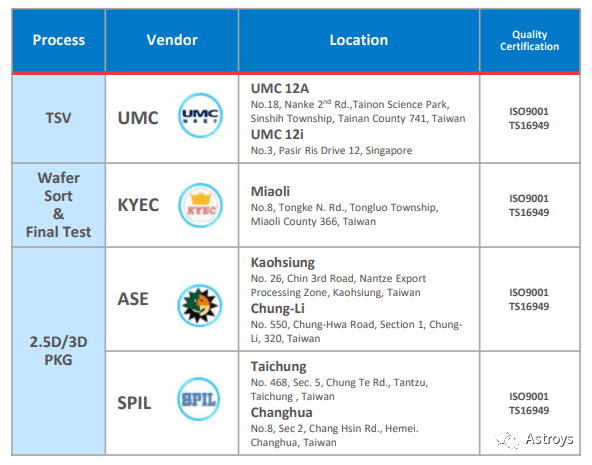

Chiplet 方案由于互連封裝方案的不同,其測試大多為定制化方案,且 包含更多的測試流程。除了常規(guī)的單片集成 SoC 芯片所需的 CP 測試(芯 片針測)、FT 測試(終測),還要包括介質(zhì)層測試、MT(中段測試)、 SLT(系統(tǒng)級測試等)。 測試流程中,KGSD(已知良好堆疊芯片)測試需要包含更多的可靠性 測試,是主要的難點之一。以 DRAM 和 HBM 為例進(jìn)行對比: 1) 在晶圓級測試環(huán)節(jié),DRAM 晶圓的測試基本相同,HBM 額外增加 針對邏輯晶圓的邏輯測試,包括測試 IP、PHY 電路中缺陷等。但是 考慮到單顆小芯片的缺陷就會導(dǎo)致堆疊的 KGSD 芯片的性能失敗, 因此對單顆小芯片的測試性能要求會更高。 2) 在 KGSD 測試環(huán)節(jié),傳統(tǒng)的 DRAM 封裝級產(chǎn)品測試設(shè)備和解決方法 將無法有效試用,其測試的挑戰(zhàn)包括動態(tài)向量老化應(yīng)力測試、大量 內(nèi)部 TSV 結(jié)構(gòu)的可靠性測試、高速性能測試、2.5D SIP 測試等。

2. Chiplet 封裝:高密度集成封裝是實現(xiàn) Chiplet 的核 心

Chipet 封裝方案可分為 2D、2.1D、2.5D 和 3D 封裝技術(shù)。2D 方案性價 比高,但無法承受大面積集成,上升空間有限;2.1D 方案集成度進(jìn)一步提高,但技術(shù)難度相對較大,應(yīng)用范圍偏小;2.5D 方案成本高,但硅轉(zhuǎn) 接板技術(shù)相對成熟,可集成密度較高,雖然價格昂貴,但在服務(wù)器等應(yīng) 用領(lǐng)域具有較大潛在價值,另外結(jié)合 3D 封裝后,整體成長空間最大, 是延續(xù)摩爾定律的潛在核心方案。

2.1. 從 2D 到 3D,封裝形式多樣

先進(jìn)封裝技術(shù)不同于傳統(tǒng)封裝技術(shù),其主要包含 RDL、Bump、Wafer 和 TSV 四個要素。傳統(tǒng)封裝主要包括 DIP、QFP 等引腳封裝和引線框架 封裝,而諸如 FC-BGA、FO WLP 和 FI WLP 等包含 RDL、Bump、Wafer 和 TSV 四個要素之一,均屬于先進(jìn)封裝。 Chiplet 封裝方案是小芯粒的異構(gòu)異質(zhì)高密度集成方案,對應(yīng)不同的封 裝類別,以先進(jìn)封裝技術(shù)為基礎(chǔ),可主要分為 2D、2.1D、2.5D 和 3D 四大類。考慮到市場上各家公司對于封裝方案的定義并不明確,本文粗 淺根據(jù)在基板基礎(chǔ)上是否有 RDL 層和硅橋、是否有無源硅轉(zhuǎn)接板、是 否有有源硅板之間的堆疊,進(jìn)行分類,依次劃分為 2D、2.1D、2.5D 和 3D 四大類,其中 2D 方案由于不使用任何額外高密度 RDL/硅等轉(zhuǎn)接板, 性價比高,在 Chiplet 的發(fā)展初期,產(chǎn)品中應(yīng)用廣泛。

一、2D 方案的客戶和產(chǎn)品應(yīng)用

2D 方案主要為簡單的 MCM 方案,無需額外的轉(zhuǎn)接板,成本低,性價 比高,應(yīng)用較為廣泛,但無法支撐多芯片大面積應(yīng)用,在性能提升上空 間有限。2D 方案整體厚度較薄,主要分為 FC-MCM 類的直接通過封裝 基板走線實現(xiàn)互連和普通 InFO 類的無需基板直接通過 RDL 層進(jìn)行互連。 FC-MCM 類受限于 ABF 基板良率低,無法支撐多芯片大面積的應(yīng)用。 普通 InFO 類由于沒有基板,僅憑 PI 材料的 RDL 層,硬度不夠,同樣 無法支撐大面積的多芯片集成。 2D 方案受益于性價比,國內(nèi)外客戶多家產(chǎn)品有量產(chǎn),在四種類別中應(yīng) 用最廣,發(fā)展最快。AMD 的最初 Zen 架構(gòu)的系列產(chǎn)品采用的就是 MCM 方案,如銳龍、霄龍等。另外,國內(nèi)包括超摩科技(高性能 CPU)、龍 芯中科等都有相關(guān)方案研究。

二、2.1D 方案的產(chǎn)品和客戶應(yīng)用

2.1D 方案介于 2D 的 MCM 和 2.5D 硅轉(zhuǎn)接板之間,成本相對適中,可 集成度較高,可適用于大規(guī)模多芯片集成。2.1D 方案主要在基板上采用 高密度的 RDL 層或者在 RDL 層/基板中內(nèi)嵌硅橋來增大集成密度。高密 度的 RDL 層方案包括特斯拉的 InFO-SoW(六層 RDL)、TSMC 的 InFO-R/InFO-oS/InFO-LSI 系列、長電的 XDFOI(五層 RDL)等。內(nèi)嵌 硅橋的方案以 Intel 的 EMIB、日月光的 FOCoS-B 為主。 2.1D 方案的主要缺點在于技術(shù)難度相對較大,目前只在少數(shù)客戶中使用。 例如高密度 RDL 層的 InFO-R 中,本身 InFO 工藝就較為復(fù)雜,還需要 在 PI 樹脂中進(jìn)行多層 RDL 高密度布線,難度更加巨大。目前主要在蘋 果的 M1 MAX 芯片中使用該方案較多。例如內(nèi)嵌硅橋的 EMIB和 FOCoS 方案中,需要額外考慮硅橋和 RDL 層/基板的兼容性,目前主要在 Intel 的產(chǎn)品中使用較多。

三、2.5D 方案的產(chǎn)品和客戶應(yīng)用

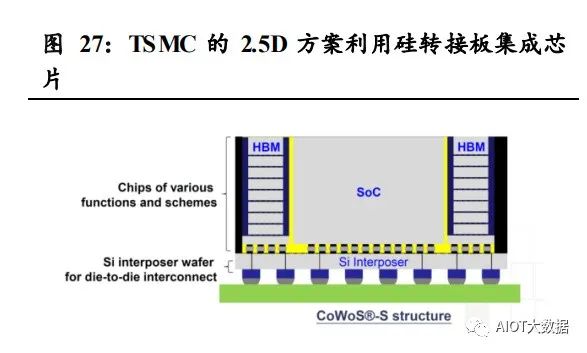

2.5D 方案利用無源硅轉(zhuǎn)接板方案,可實現(xiàn)更高密度、大面積多芯片的集 成方案,傳輸速度高,性能優(yōu)越,是潛在延續(xù)摩爾定律成長空間的主要 方案。無源硅轉(zhuǎn)接板利用內(nèi)部 RDL 和 TSV 可實現(xiàn)內(nèi)部的高密度互連, 加上硅技術(shù)較為成熟,成為替代先進(jìn)工藝延續(xù)摩爾定律的中堅力量。另 外 3D 方案的拓展也主要建立在 2.5D 方案的基礎(chǔ)上。主要方案包括臺積 電的 CoWoS 系列方案,三星的 I-Cube,通富的 VISionS 等。 2.5D 方案整體性能更為優(yōu)越,但由于增加硅轉(zhuǎn)接板,成本較高,主要用 在服務(wù)器、數(shù)據(jù)中心等高端應(yīng)用中,發(fā)展前景巨大。鯤鵬 920、AMD 的 Zen2 以上架構(gòu)產(chǎn)品諸如 Rome、Milan 等服務(wù)器芯片都應(yīng)用 CoWoS 方案。 以 AMD 的 Zen4 架構(gòu)的 EPYC 7004 服務(wù)器芯片為例,其內(nèi)部可封裝的 CCD 數(shù)量增加到 12 個,內(nèi)核增加到 96 個,可支持 12 通道的 DDR5 內(nèi) 存,提供 128 條 PCIE 5.0 通道,性能十分突出。

四、3D 方案的產(chǎn)品和客戶應(yīng)用

3D 方案主要在 2.5D 基礎(chǔ)上,利用混合鍵合等方式實現(xiàn)芯片間的垂直互 連,集成密度最大,性能提升也十分可觀,但成本非常高。3D 方案為 有源硅之間的互連,即芯片之間的互連,為滿足足夠的信息帶寬,使用 的互連線的數(shù)量和密度都遠(yuǎn)大于前三種,而且混合鍵合的難度也遠(yuǎn)大于 bump 鍵合,整體成本非常高。主要方案包括 Intel 的 Co-EMIB/Foveros、 三星的 X-Cube、TSMC 的 SoIC、HBM、3D V-Cache 等技術(shù)。 3D 方案由于成本非常高,相關(guān)應(yīng)用較少,主要在對性能要求非常苛刻 的高端應(yīng)用領(lǐng)域。相關(guān)的 HBM、3D V-Cache 等產(chǎn)品主要用在對計算要求較高的 AI 芯片中或者對延遲要求非常高的游戲 CPU 芯片中。HBM 主 要將各種 DRAM 芯片進(jìn)行堆疊,從而擴(kuò)大內(nèi)存容量,在高性能計算領(lǐng) 域需求量較大。3D V-Cache 主要將 L3 cache 堆疊在 CPU 上,以減小延 遲,這在游戲領(lǐng)域需求量較大。

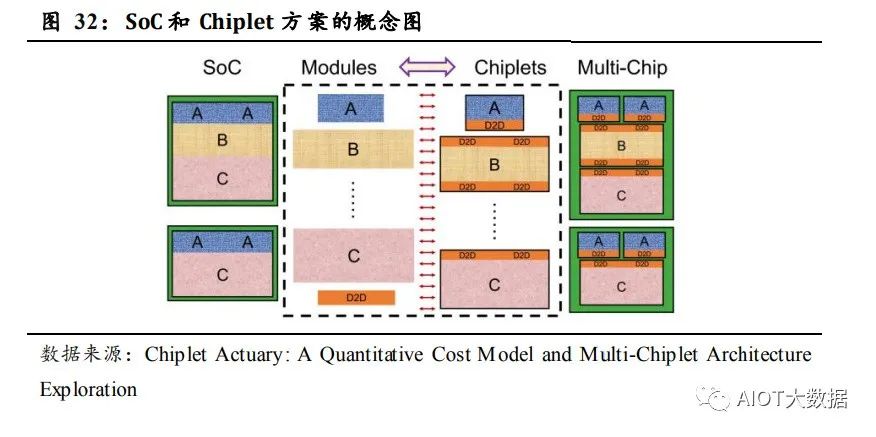

2.2. 高性能大芯片是實現(xiàn)成本性能最優(yōu)化的應(yīng)用

就成本而言,先進(jìn)封裝只對先進(jìn)工藝的大芯片即高性能大芯片存在明顯 成本效益。MCM 等最基本的 2D 封裝不僅滿足架構(gòu)需求,提高性能, 成本還低,可能會被最先大范圍使用。2.5D 等封裝方案成本高,但結(jié)合 3D 封裝后,整體可提升的成長空間最大,是潛在核心方案。 多芯片集成的 Chiplet 方案是在以先進(jìn)工藝為基礎(chǔ)的 SoC 方案遇到摩爾 定律發(fā)展的門檻時,所延伸的提升性能、減小成本、優(yōu)化性價比的方案。 SoC 方案為將 A、B、C 等各種 IP 內(nèi)核進(jìn)行組合搭配,無需 D2D(Die to Die)的 IP;而 Chiplet 方案為將 A、B、C 等各種內(nèi)核分別與 D2D IP 進(jìn) 行組合,依次封裝,并在基板或者硅轉(zhuǎn)接板上進(jìn)行互連組合,并利用高 密度集成封裝方案進(jìn)行封裝。 Chiplet 方案的成本隨著集成密度的提高而不斷提高,需要和小芯片的 成本進(jìn)行綜合考量,實現(xiàn)最優(yōu)綜合性能。例如 2D 方案的 MCM 封裝集 成密度最低,bump 密度為 90 微米,成本也最低。而 RDL Interposer 和Si Interposer 的集成密度逐步提高,bump 密度分別達(dá)到 45/30 微米,成 本也相對提升,其中硅轉(zhuǎn)接板的成本最高。3D 封裝的 bump 密度達(dá)到 9 微米,成本是所有集成封裝方案中最高的。

就成本角度進(jìn)行考量,一塊單片 SoC 芯片或者 Chiplet 芯片,主要成本 可粗略劃分為 RE(recurring engineering)成本和 NRE(non-recurring engineering)成本。NRE 成本為電路設(shè)計中的一次性成本,包括軟件、 IP 授權(quán)、模塊/芯片/封裝設(shè)計、驗證、掩模版等費用,針對于單顆芯片 是攤銷后的成本。RE 成本為大規(guī)模量產(chǎn)中的制造成本,包括晶圓、封 裝、測試等。 根據(jù)《Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration》中的成本模型和驗證數(shù)據(jù):

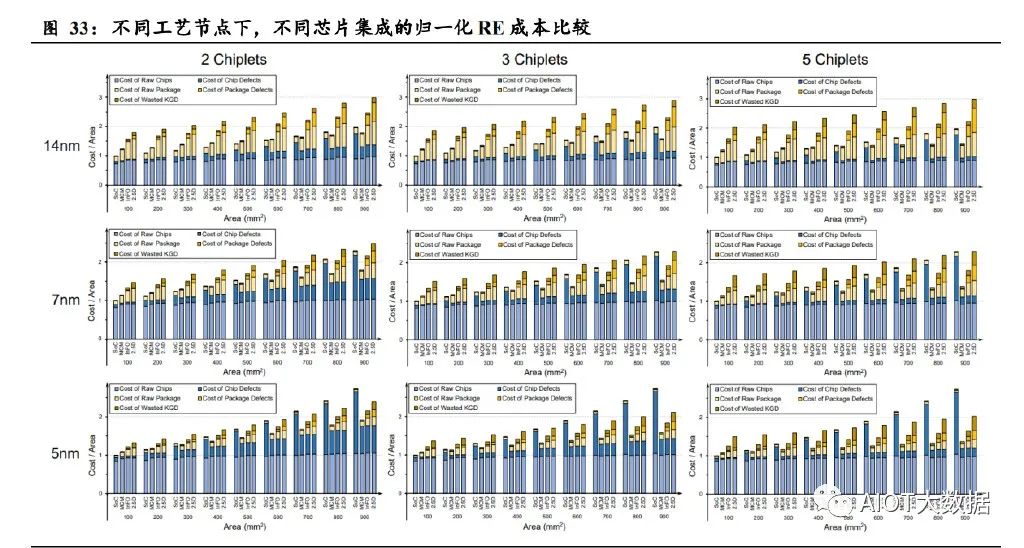

一、在 RE 成本方面,主要包含五部分:1)原芯片成本;2)芯片缺陷 成本;3)原封裝成本;4)封裝缺陷成本;5)因為封裝缺陷導(dǎo)致的 KGDs 被浪費的成本。對于芯片間 D2D 帶來的成本,等同于一塊特定的 IP 核。 對于不同的工藝和架構(gòu),它在芯片面積中占一定比例。其他諸如 bumping、 wafer sort、測試等成本由于重要性較低,包含如前述五項中,不進(jìn)行額 外考慮。 就不同的集成的小芯片的數(shù)量、不同的芯片面積和不同的工藝節(jié)點,針 對不同的封裝形式進(jìn)行考量,得出結(jié)論:

① 工藝節(jié)點越小,芯片面積越大,多芯片集成的 Chiplet 方案帶來的 好處越大。SoC 主要的成本增加來源于面積增大后導(dǎo)致的芯片缺陷成本。 以 800mm2 的 5nm 工藝 SoC 芯片為例,其芯片缺陷成本占總成本超過 50%,而 100mm2 的芯片中的芯片缺陷成本占比不足 10%。當(dāng)對此芯片 進(jìn)行芯粒化+高密度封裝,芯片缺陷成本減小一半,哪怕疊加 2.5D 封裝 帶來的封裝成本,其總成本仍小于 SoC 方案。 就 2 Chiplets 組成的 14nm 芯片而言,只有當(dāng)面積大于 700mm2,SoC 的 成本才勉強(qiáng)大于 MCM。而對于 InFO 和 2.5D,哪怕面積大于 900mm2, SoC 方案始終占有成本優(yōu)勢。 就 2 Chiplets 組成的 7nm 芯片而言,當(dāng)面積大于 500 mm2,SoC 的成本 大于 MCM;當(dāng)面積大于 800 mm2,SoC 的成本才大于 InFO; 就 2 Chiplets 組成的 5nm 芯片而言,當(dāng)面積大于 300 mm2,SoC 的成本 大于 MCM;當(dāng)面積大于 500 mm2,SoC 的成本大于 InFO;當(dāng)面積大于 700 mm2,SoC 的成本才大于 2.5D 方案;總之,對于任何工藝節(jié)點,芯片面積提升帶來的好處,先進(jìn)工藝節(jié)點會 早于成熟工藝。成熟工藝節(jié)點不適合高密度 Chiplet 的原因在于 14nm 工藝較為成熟,良率較高,面積增大帶來的芯片缺陷成本的增加小于 D2D以及更高級封裝帶來的成本增加。小面積芯片不適合高密度 Chiplet 的原因在于芯片缺陷成本太小,封裝類的成本占據(jù)主要。 ② 小芯粒數(shù)量的提升,對成本的優(yōu)化具有一定效果。就 5nm,800 mm2 的 MCM 芯片而言,從 3 個小芯粒增加到 5 個小芯粒,芯片的缺陷成本 的減小約為 10%。

二、在 NRE 成本方面,

多芯片 Chiplet 方案會造成非常高的額外 NRE 成本,只有當(dāng)量產(chǎn)數(shù)量足 夠高,才有足夠性價比。以 14nm 的 800mm2 的芯片為例,500k 的銷量, 對于成本最高的 2.5D 封裝,D2D 的互連和封裝的成本占比分別小于 2% 和 9%,而 Chiplet 1/2 模塊和芯片的成本在 MCM 中占 36%,在 2.5D 中 占 31%,占比非常高,不如采用單集成 SoC 方案。而當(dāng)銷量從 500k 增 加到 10M 時,Chiplet 方案的成本將大幅縮減。

除了面積、工藝、小芯片的數(shù)量以外,Chiplet 在多芯片架構(gòu)復(fù)用和異 構(gòu)方面存也在著巨大的成本優(yōu)勢。多芯片復(fù)用架構(gòu)主要分為三類:① SCMS(單芯片多系統(tǒng));②OCME(一中心多拓展);③FSMC(固定插 座多組合)。 ① SCMS:芯片的復(fù)用,使 Chiplet 相較于 SoC 而言節(jié)省一次性投入成 本。該種方案只需要一個芯片即可,適用于同一產(chǎn)品線不同等級的 產(chǎn)品。AMD 和國內(nèi)最初的產(chǎn)品架構(gòu)就是采用該方案。 ② OCME:實現(xiàn)了異構(gòu)工藝,將不同的成熟工藝產(chǎn)品和先進(jìn)工藝產(chǎn)品 進(jìn)行拼接。諸如 AMD 的 ZEN3 架構(gòu)采用的就是該方案。 ③ FSMC:將復(fù)用的可能性最大化,即將可復(fù)用的芯片最小化,這樣一 次性投入成本攤銷的收益就越大。多芯片集成的 Chiplet 方案的成本 優(yōu)勢將會最大化。

3. Chiplet 空間:高算力需求打開成長空間,封測端 是主要受益點

3.1. AI+數(shù)字經(jīng)濟(jì)催生高算力需求,Chiplet 深度受益

ChatGPT作為生成式 AI 的現(xiàn)象級產(chǎn)品,將催生龐大的產(chǎn)業(yè)鏈算力需求。 ChatGPT 是 OpenAI 開發(fā)的聊天機(jī)器人,在 2022 年 11 月推出,一經(jīng)推 出,就成為迄今為止用戶量增長最快的消費應(yīng)用程序,僅用 2 月就積累 1 億用戶數(shù)量,即使是海外現(xiàn)象級應(yīng)用 TikTok 也用了 9 個月的時間。未 來國內(nèi)外諸如百度等大模型公司、科大訊飛等應(yīng)用端公司都在積極參與, 帶來龐大的算力需求。

數(shù)字經(jīng)濟(jì)推動數(shù)據(jù)中心建設(shè)快速發(fā)展,帶動計算需求增長。受益于 5G、 人工智能、大數(shù)據(jù)、云計算等新興產(chǎn)業(yè)發(fā)展,對海量數(shù)據(jù)處理的需求不 斷提升,數(shù)據(jù)中心成為數(shù)字化發(fā)展的重要基礎(chǔ)設(shè)施。截止 2021 年底, 我國在用數(shù)據(jù)中心機(jī)架規(guī)模達(dá)到 520 萬架,近五年 CAGR 超過 30%,其 中大型以上機(jī)架規(guī)模達(dá) 420 萬架,占比達(dá) 80%。進(jìn)入數(shù)字經(jīng)濟(jì)時代,數(shù) 據(jù)量呈指數(shù)級增長,對算力提出了巨大需求。據(jù) Cisco 預(yù)計,2021 年計 算能力更強(qiáng)的超級數(shù)據(jù)中心將達(dá)到 628 座,占數(shù)據(jù)中心總量的 53%。

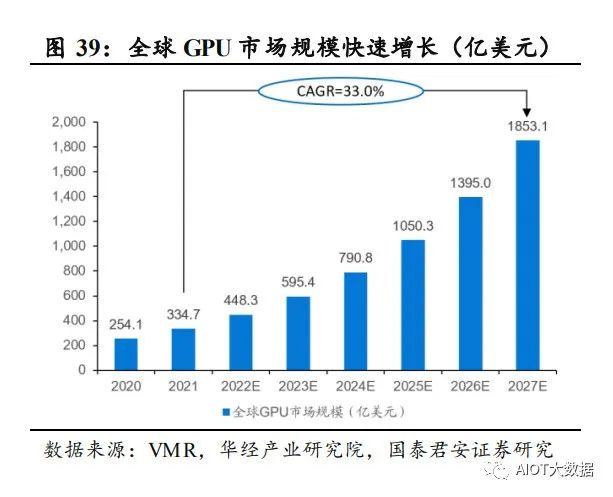

受益于 AI 和數(shù)字經(jīng)濟(jì)的需求,全球 GPU、MPU、AI 芯片等大算力芯 片需求大幅提升。2027 年全球 GPU 市場規(guī)模預(yù)計達(dá)到 1853.1 億美元, 21-27 年 CAGR 為 33%。2022 年 MPU 的全球市場規(guī)模也已經(jīng)突破 1000 億美元。2024 年 AI 的中國市場規(guī)模也預(yù)計突破 785 億元,21-24 年 CAGR 為 46%。

3.2. 產(chǎn)業(yè)生態(tài)發(fā)展早期,封測端是主要受益點

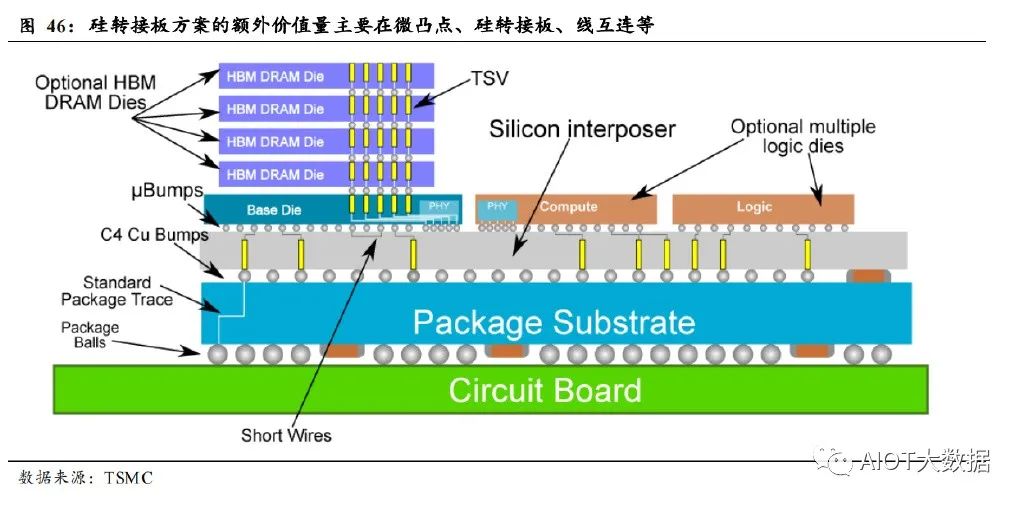

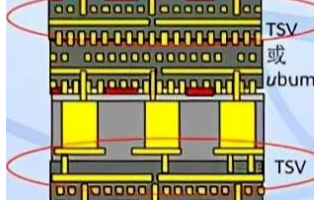

Chiplet 生態(tài)仍處于發(fā)展早期,就產(chǎn)業(yè)鏈而言,價值量的增長點主要集 中在封測端和材料端。目前產(chǎn)業(yè)仍處于 Chiplet 生態(tài)成長期,設(shè)計廠商 主要采用已有的 EDA 和 IP 針對 Chiplets 進(jìn)行自重用和自迭代,工藝和 互連標(biāo)準(zhǔn)尚未統(tǒng)一。產(chǎn)業(yè)鏈中最大的價值量增長源于新的高密度集成的 封裝方案帶來的封測端和材料端的應(yīng)用,未來隨著生態(tài)和技術(shù)的成熟, EDA 等更上游的價值量也會逐步增加。 Chiplet 業(yè)務(wù)鏈中,晶圓廠和封測廠都逐步向產(chǎn)業(yè)鏈下游垂直整合,以 擴(kuò)大自身的業(yè)務(wù)空間和利潤增長點。晶圓廠圍繞硅互連技術(shù)進(jìn)行發(fā)展, 從帶 TSV 的轉(zhuǎn)接板向 RDL 層、微凸點等領(lǐng)域拓展,自上而下,拓展價 值空間。封測廠在爭取從原有的基板、C4 凸點向上游 Chiplet 業(yè)務(wù)鏈中 的 RDL 層、TSV 轉(zhuǎn)接板、微凸點等方向發(fā)展,因為該塊業(yè)務(wù)精細(xì)度不 高但有較大業(yè)務(wù)量。不過,封測廠話語權(quán)不如晶圓廠,大多封測廠更多 向下游拓展,將更多的元器件、射頻器件、PMIC 等集成到基板中,以 期獲得更大的價值量增長。

在封裝端,對于封裝廠而言,價值量額外增長主要集中在微凸點、轉(zhuǎn)接 板、線互連等領(lǐng)域。 ① 在MCM的2D領(lǐng)域,只增加了額外的基板內(nèi)互連,價值量增長最低。 ② 在 RDL 轉(zhuǎn)接板的 2.1D 領(lǐng)域(RDL 整體較薄,介于 2.5D 和 2D 之間, 又可稱為 2.1D),主要為臺積電的 InFO 和長電的 XDFOI 等方案。 InFO 方案是 Chipfirst 技術(shù),沒有微凸點,由于該類方案主要由 TSMC 主導(dǎo),下游封測廠話語權(quán)較小,價值量仍主要局限于原有封測領(lǐng)域, 如 C4 bump 和基板等。XDFOI 方案是 chiplast 方案,存在微凸點, 該類方案包含多層 RDL 層、微凸點、互連線等,封測廠可做價值量 更大。 ③ 在硅轉(zhuǎn)接板的 2.5D 領(lǐng)域,主要為臺積電的 CoWoS 等方案,該方案 價值量較多,包括微凸點、RDL、硅轉(zhuǎn)接板、TSV 等,但同樣受限 于 TSMC 等晶圓廠較為強(qiáng)勢的話語權(quán),大多硅轉(zhuǎn)接板等價值量都被 晶圓廠拿走。但是臺積電等晶圓廠開價過高,終端廠等正嘗試分散 供應(yīng)鏈,各環(huán)節(jié)找不同的廠商,以實現(xiàn)利益最大化。 ④ 在 3D 領(lǐng)域,如 HBM 方案,由于精細(xì)要求較高,這部分基本全部依 賴晶圓廠,在晶圓制造領(lǐng)域直接堆疊完成。

在測試端,受益于小芯粒帶來更多的測試需求以及 KGSD 帶來更復(fù)雜的 測試要求,相關(guān)測試公司和測試設(shè)備公司將深度受益。例如偉測科技、 長川科技、和林微納等都將較為受益。 在材料端,受益于 Chiplet 的突破和高算力的需求,ABF 膜的需求在不 斷增長,相關(guān)基板產(chǎn)業(yè)鏈公司將深度受益。例如生益科技、深南電路等 都將較為受益。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論