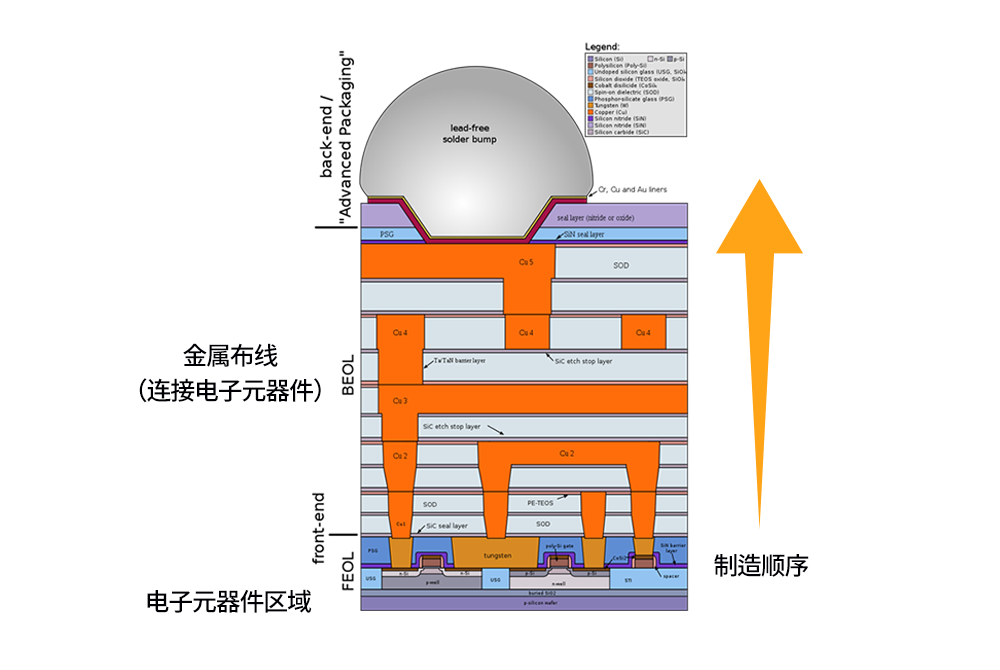

半導體制作工藝可分為前端和后端:前端主要是晶圓制作和光刻(在晶圓上繪制電路);后端主要是芯片的封裝。隨著前端工藝微細化技術逐漸達到極限,后端工藝的重要性愈發突顯。作為可以創造新附加價值的核心突破點,其技術正備受矚目。

此系列文章將以《提高半導體附加價值的封裝與測試》一書內容為基礎,詳細講解后端工藝。

#1 半導體后端工藝

制作半導體產品的第一步,就是根據所需功能設計芯片(Chip)。然后,再將芯片制作成晶圓(Wafer)。由于晶圓由芯片反復排列而成,當我們細看已完成的晶圓時,可以看到上面有很多小格子狀的結構,其中一個小格子就相當于一個芯片。芯片體積越大,每個晶圓可產出的芯片數量就越少,反之亦然。

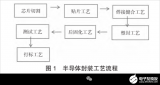

半導體設計不屬于制程工序,半導體產品的制程工序大體可分為晶圓制作、封裝和測試。其中,晶圓制作屬于前端(Front End)工藝;封裝和測試屬于后端(Back End)工藝。晶圓的制作工藝中也會細分前端和后端,通常是CMOS制程工序屬于前端,而其后的金屬布線工序屬于后端。

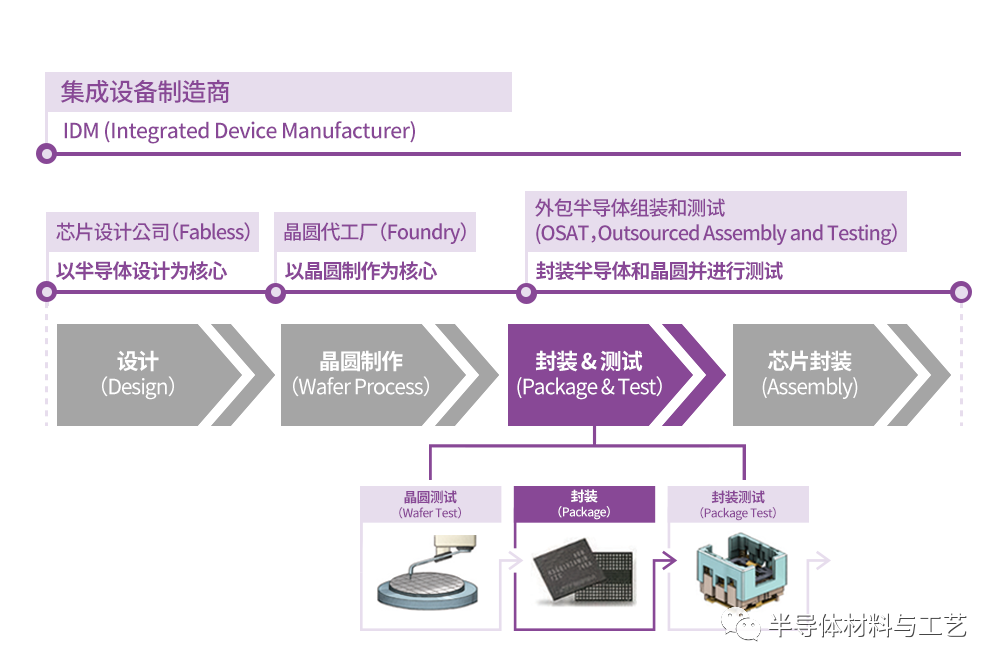

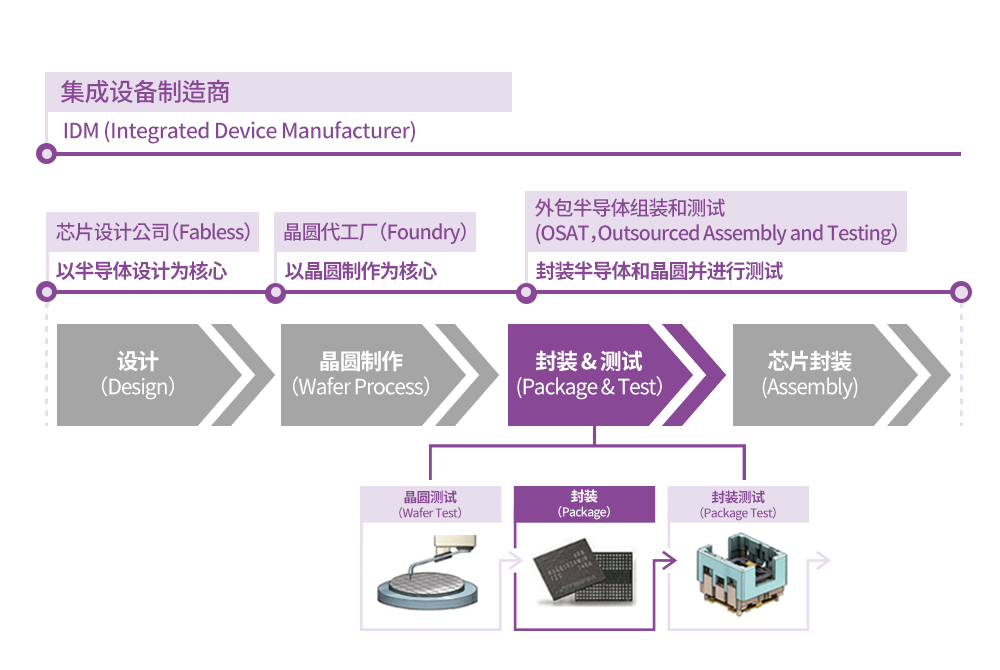

▲ 圖1:半導體制作流程與半導體行業劃分(?HANOL出版社/photograph.SENSATA)

圖1展示了半導體制程工藝及其行業的劃分。只從事半導體設計的產業運作模式被稱作芯片設計公司(Fabless),該模式的典型代表有高通(Qualcomm)、蘋果(Apple)等。負責晶圓制作的制造商被稱為晶圓代工廠(Foundry),他們根據Fabless公司的設計制作晶圓,其中最典型的代表要臺積電(TSMC)了,DB HiTek、Magnachip等韓企也采用這一模式。經Fabless設計和Foundry制造的晶圓還需經過封裝和測試,專門負責這兩道工藝的企業就是外包半導體組裝和測試(OSAT,Outsourced?Assembly?and?Testing),其典型代表有ASE、JCET、星科金朋(Stats Chippac)、安靠(Amkor)等。此外,還有像SK海力士這樣集半導體設計、晶圓制造、封裝和測試等多個產業鏈環節于一身的集成設備制造商(IDM,Integrated Device Manufacturer)。

如圖1所示,封裝和測試工藝的第一步就是晶圓測試。封裝后,再對封裝進行測試。

半導體測試的主要目的之一就是防止不良產品出廠。一旦向客戶提供不良產品,客戶對我們的信任就會大打折扣,進而導致公司銷售業績的下降,還會引發賠償等資金上的損失。因此,我們必須在產品出廠前對其進行細致的全面檢測。半導體測試須根據產品的各種特性,對其各參數進行測試,以確保產品的品質和可靠度。當然,這需要時間、設備和勞動力上的投入,產品的制造成本也會隨之增加。因此,眾多測試工程師正致力于減少測試時間和測試參數。

#2 測試的種類

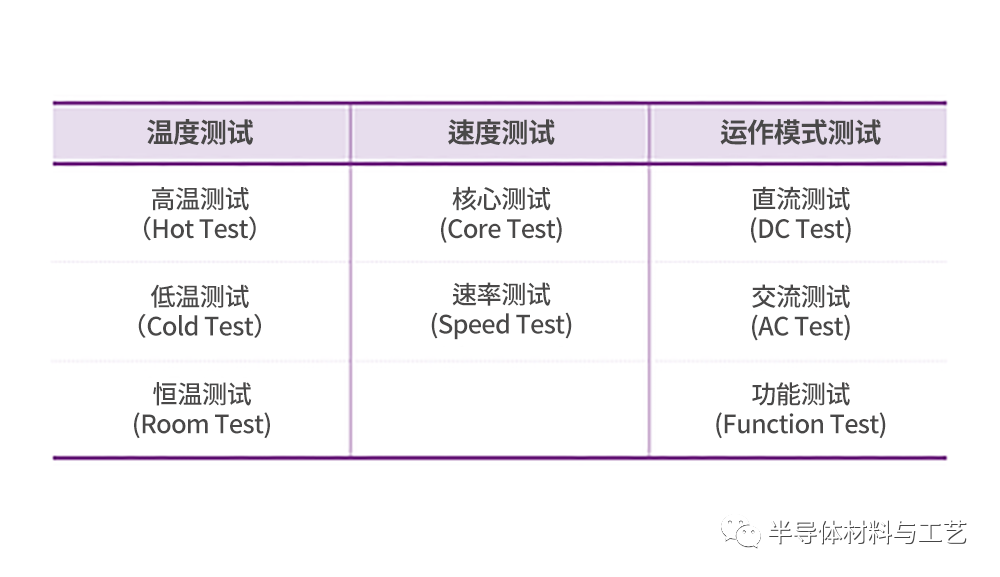

▲ 表1: 測試分類(? HANOL出版社)

測試工藝可依據不同的測試對象,分為晶圓測試和封裝測試;也可根據不同的測試參數,分為溫度、速度和運作模式測試等三種類型(見表1)。

溫度測試以施加在試驗樣品上的溫度為標準:在高溫測試中,對產品施加的溫度比產品規格1?所示溫度范圍的上限高出10%;在低溫測試中,施加溫度比規格下限低10%;而恒溫測試的施加溫度一般為25℃。在實際使用中,半導體產品要在各種不同的環境中運作,因此必須測試產品在不同溫度下的運作情況以及其溫度裕度(Temperature Margin)。以半導體存儲器為例,高溫測試范圍通常為85~90℃,低溫測試范圍為-5~-40℃。

1?規格(Spec): specification的縮寫,指產品配置,即制造產品時在設計、制作方法上或對所需特性的各種規定。

速度測試又分為核心(Core)測試和速率測試。核心測試主要測試試驗樣品的核心運作,即是否能順利實現原計劃的目標功能。以半導體存儲器為例,由于其主要功能是信息的存儲,測試的重點便是有關信息存儲單元的各項參數。速率測試則是測量樣品的運作速率,驗證產品是否能按照目標速度運作。隨著對高速運轉半導體產品需求的增加,速率測試目前正變得越來越重要。

運作模式測試細分為直流測試(DC Test)、交流測試(AC?Test)和功能測試(Function?Test):直流測試驗證直流電流和電壓參數;交流測試(AC Test)驗證交流電流的規格,包括產品的輸入和輸出轉換時間等運作特性;功能測試則驗證其邏輯功能是否正確運作。以半導體存儲器為例,功能測試就是指測試存儲單元(Memory cell)與存儲器周圍電路邏輯功能是否能正常運作。

#3 晶圓測試

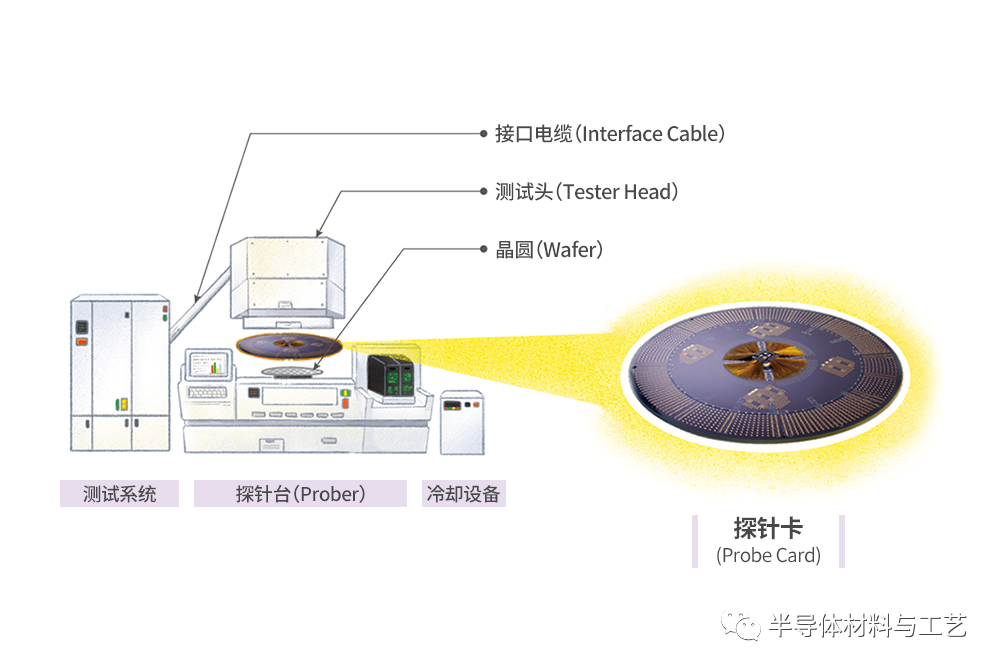

晶圓測試的對象是晶圓,而晶圓由許多芯片組成,測試的目的便是檢驗這些芯片的特性和品質。為此,晶圓測試需要連接測試機和芯片,并向芯片施加電流和信號。

完成封裝的產品會形成像錫球(Solder?Ball)一樣的引腳(Pin),利用這些引腳可以輕而易舉完成與測試機的電氣連接。但在晶圓狀態下,連接兩者就需要采取一些特殊的方法,比如探針卡(Probe?Card)。

如圖2所示,探針卡是被測晶圓和測試機的接口,卡上有很多探針2可以將測試機通訊接口和晶圓的焊盤直接連接起來,卡內還布置了很多連接探針與測試機的連接線材。探針卡固定在測試頭上,晶圓探針臺通過使探針卡與晶圓焊盤點精準接觸,完成測試。

2?探針: 與晶圓焊盤進行電氣連接和直接接觸的針狀物。

▲ 圖2 : 晶圓測試系統模式圖(? HANOL出版社/photograph.Formfactor)

將晶圓正面朝上裝載后,再把圖2右側的探針卡反過來使針尖朝下,實現與晶圓焊盤的準確對位。這時,溫度調節設備根據測試所需溫度條件,施加相應溫度。測試系統通過探針卡傳送電流和信號,并導出芯片訊號,從而讀取測試結果。

探針卡要根據被測芯片的焊盤布局和晶圓芯片排布制作,即探針與被測晶圓焊盤布局要一致。而且,要按照芯片排列,反復排布探針。其實,在實際操作中,僅憑一次接觸是無法測試晶圓的所有芯片的。因此,在實際量產過程中要反復接觸2~3次。

一般來講,晶圓測試依次按照“電氣參數監控(EPM) → 晶圓老化(Wafer Burn in) → 測試 → 維修(Repair) → 測試”順序進行。下面,我們來詳細講解一下晶圓測試的具體工序。

◎ 電氣參數監控(EPM,Electrical Parameter Monitoring)

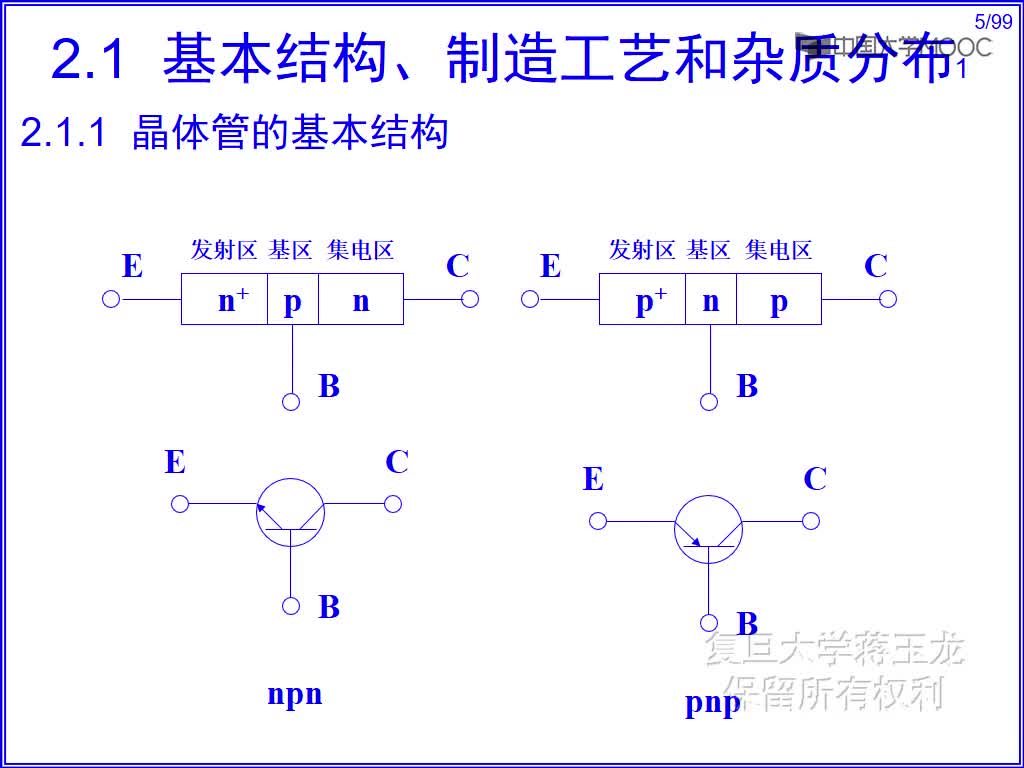

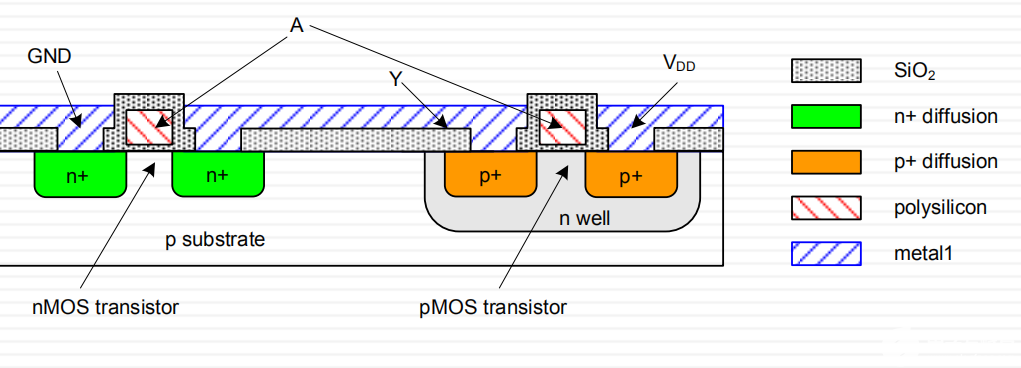

測試可以篩選出不良產品,又可以反饋正在研發或量產中的產品缺陷,從而進行改善。相比而言,電氣參數監控的主要目的是后者,即通過評價分析產品單位元件的電氣特性,對晶圓的制作工序提供反饋。具體來說,就是在進入正式晶圓測試前,采用電學方法測量晶體管的特性和接觸電阻,驗證被測產品是否滿足設計和元件部門提出的基本特性。從測試的角度來看,就是利用元件的電學性能提取直流參數(Parameter),并監控各單位元件的特性。

◎ 晶圓老化(Wafer Burn in)

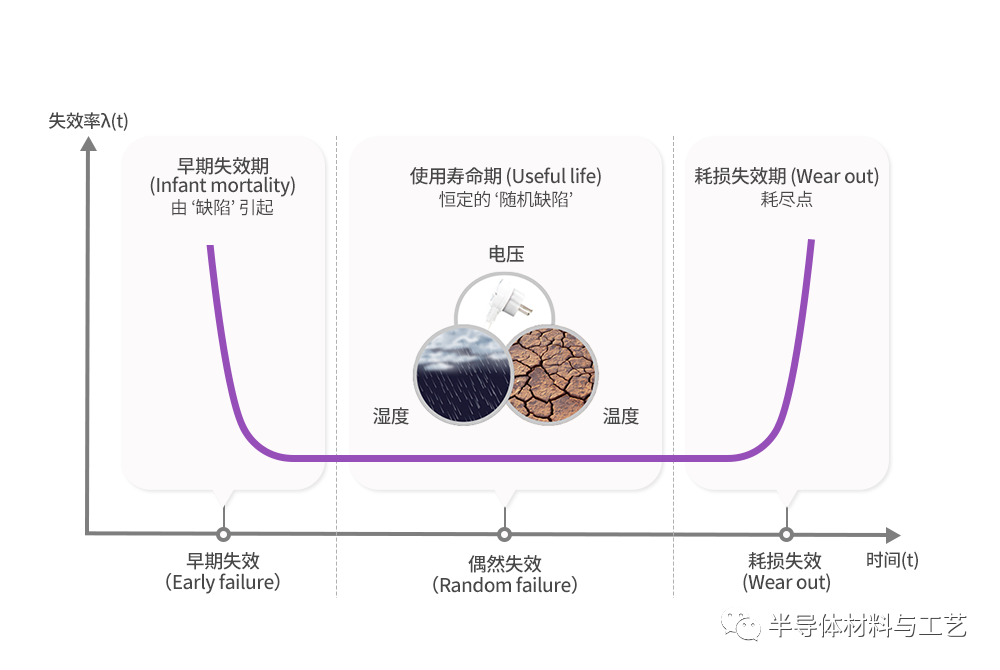

▲ 圖3:產品使用時間與不良率(? HANOL出版社)

圖3以時間函數揭示了產品生命周期中的不良率 [曲線呈現出如同浴缸的形狀,故被稱作浴盆曲線(Bath-Tub Curve)] :早期失效(Early failure)期,產品因制作過程中的缺陷所導致的失效率較高;制造上的缺陷消失后,產品進入偶然失效(Random failure)期,在此期間,產品的失效率降低;產品老化磨損后進入耗損(Wear out)失效期,失效率明顯再次上升。可見,如果完成產品后立即提供給客戶,早期失效會增加客戶的不滿,造成退貨等產品問題的可能性也很大。

“老化(Burn in)”的目的就是為識別產品的潛在缺陷,提前發現產品的早期失效狀況。晶圓老化是在晶圓產品上施加溫度、電壓等外界刺激,剔除可能發生早期失效的產品的過程。

◎ 晶圓測試

在晶圓老化(Wafer Burn in)測試剔除早期失效產品后使用探針卡進行晶圓測試。晶圓測試是在晶圓上測試芯片電學性能的工序。其主要目的包括:提前篩選出不良芯片、事先剔除封裝/組裝3過程中可能產生的不良產品并分析其原因、提供工序反饋信息,以及通過晶圓級驗證(Wafer Level Verification)提供元件與設計上的反饋等。

在晶圓測試中篩選出的部分不良單元4,將會在我們下面要講到的維修(Repair)過程中被備用單元(Redundancy cell)替換。為測試這些備用單元是否能正常工作,以及芯片能否成為符合規格的良品,在維修工序后,必須重新進行一次晶圓測試。

3?組裝?: 與基板或系統實現電氣或直接連接、組裝的工序;

4單元(Cell): 為在記憶元件存儲信息(Data)所需的最小單位的單元數組;DRAM存儲單元(Cell)由一個晶體管(Transistor)和一個電容器(Capacitor)組成;

◎ 維修(Repair)

維修作為內存半導體測試中的一道工序,是通過維修算法(Repair Algorithm),以備用單元取代不良單元的過程。假設在晶圓測試中發現DRAM 256bit內存的其中1bit為不良,該產品就成了255bit的內存。但如果經維修工序,用備用單元替換不良單元,255bit的內存就又重新成了256bit的內存,可以向消費者正常銷售。可見,維修工序可以提高產品的良率,因此,在設計半導體存儲器時,會考慮備用單元的制作,并根據測試結果以備用單元取代不良單元。當然,制作備用單元就意味著要消耗更多的空間,這就需要加大芯片的面積。因此,我們不可能制作可以取代所有不良內存的充足的備用單元(比如可以取代所有256bit的備用256bit等)。要綜合考慮工藝能力,選擇可以最大程度地提升良率的數量。如果工藝能力強,不良率少,便可以少做備用單元,反之則需要多做。

維修可分為列(Column)單位和行(Row)單位:備用列取代不良單元所在的列;備用行取代不良單元所在的行。

DRAM的維修要先切斷不良單元的列或行,再連接備用列或行。維修可分為激光維修和電子保險絲(e-Fuse)維修。激光維修,顧名思義,就是用激光燒斷與不良單元的連接。這要求先脫去晶圓焊盤周圍連線的保護層(Passivation layer),使連接線裸露出來。由于完成封裝后的芯片表面會被各種封裝材料所包裹,激光維修方法只能用于晶圓測試。電子保險絲維修則采用在連接線施加高電壓或電流的方式斷開不良單元。這種方法與激光維修不同,它通過內部電路來完成維修,不需要脫去芯片的保護膜。因此,除晶圓測試外,該方法在封裝測試中也可使用。

#4 封裝測試

在晶圓測試中被判定為良品的芯片,經封裝工序后需要再進行封裝測試,因為這些芯片在封裝工序中有可能發生問題。而且,晶圓測試同時測試多個芯片,測試設備性能上的限制可能導致其無法充分測試目標參數。與此相反,封裝測試以封裝為單位進行測試,對測試設備的負荷相對較小,可以充分測試目標參數,從而選出符合規格的良品。

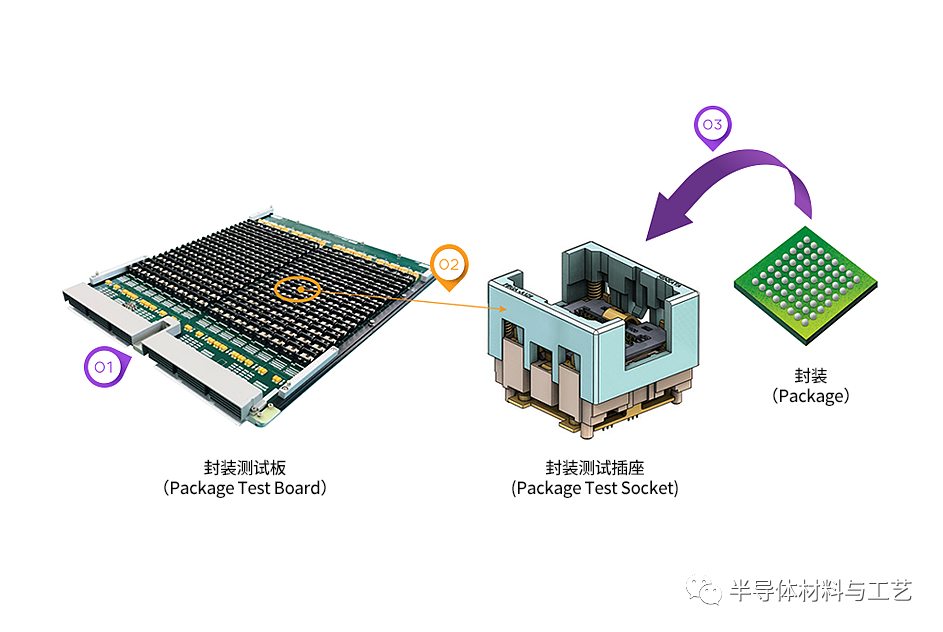

封裝測試方法如圖4所示:先把“03”的封裝引腳(Pin,圖中為錫球)朝下裝入封裝測試插座內,使引腳與插座內的引腳對齊,然后再將封裝測試插座固定到封裝測試板(Package Test Board)上進行測試。

▲ 圖4:封裝測試系統(?HANOL出版社/ photograph.NST, SENSATA)

◎ 老化測試(Test During Burn In,TDBI)

前邊也提到過,“老化(Burn in)”是為了提前發現產品的早期失效,向晶圓產品施加溫度、電壓等外界刺激的工序。這一工序既可在晶圓測試中進行,也可在封裝測試階段進行。封裝后實施的“老化”被稱為老化測試(TDBI)。大部分半導體產品在晶圓和封裝測試均進行老化測試,以便更加全面地把握產品的特性,尋找縮減老化時間和工序數量的條件。可見,老化對于量產來說是一道最有效的工序。

◎ 測試

這是驗證數據手冊5中定義的運作模式在用戶環境中能否正常工作的流程。通過溫度測試,檢驗產品交流/直流參數的缺陷,以及單元&外圍電路(Cell & Peri)區域的運作是否滿足客戶要求的規格。此時,需要在比數據手冊中規定的條件更為惡劣的條件下,甚至是最糟糕的條件下進行測試。

5?數據手冊(Data Sheet):定義半導體產品基本配置與特性等具體信息的文件。

◎ 外觀(Visual)檢測

完成所有測試后,需通過激光打標(Laser?Marking)把測試結果和速率特性(尤其是需要區分速率時)記錄在產品封裝的表面。經封裝測試和激光打標后,將良品裝入封裝托盤(Tray),產品即可出廠了。當然,在出廠前,還要進行最后一道測試——外觀測試,以剔除外觀上的缺陷。外觀檢測主要查看是否有龜裂、打標錯誤、裝入錯誤的托盤等問題;錫球方面主要檢查球是否被壓扁,或球是否脫落等問題。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論