高性能計算、人工智能等應用推動芯片的技術節點不斷向前邁進,導致設計、制造的難度 和成本問題凸顯,針對這一問題,Chiplet?技術應運而生。Chiplet?技術是將復雜的系統級芯片按?IP?功 能切分成能夠復用的“小芯片?(芯粒)”,然后將執行存儲和處理等功能的小芯片以超高密度扇出型封 裝、2.5D?和?3D?高端性能封裝進行重新組裝,以實現高性能計算對高帶寬、高性能的要求。介紹了上 述封裝的多樣化形式和通信協議,分析其重要的電連接結構與工藝難點,及其在可靠性方面的一些問題。

引言 ? ?

高性能計算、人工智能、5G?通信、數據中心和云計 算的快速發展使芯片的技術節點不斷向前推進,單顆 芯片上集成的晶體管數目已超過百億級。與此同時, 將更多功能集成在單顆芯片的難度不斷增大,設計與 制造的成本不斷上升。與?90 nm?技術節點相比,3 nm技術節點的投資成本增加了?35~40?倍,僅英特爾 (Intel)、臺積電(TSMC)和三星(Samsung)3?家頭部企 業參與其中。5 nm?技術節點的設計成本超過?5?億美 金,約是?28 nm?的?10?倍。為解決上述問題,出現了?Chiplet?概念。

Chiplet?作為一種設計概念,指將單顆集成復雜功 能的片上系統級芯片(SoC)離散成多顆特定功能的小 芯片(Chiplet,又稱“芯粒”),再采用封裝技術將其整合 在一起,構成多功能的異構系統級封裝(SiP),以持續 提高器件算力,縮短產品開發周期,提升產品良率,降 低整體成本。近年來,受限于高端設備和材料的能力 等,以?Chiplet?方式將處理芯片與存儲芯片封裝集成的 技術越來越重要。目前,TSMC、Intel、Samsung?等均已 發布相關產品,通過高密度(≥16 /mm2)和窄節距(≤?130?μm)的輸入?/?輸出接口(I/O)為處理芯片與存儲芯 片提供定制化的封裝,以應對高性能計算、人工智能、 數據處理等前沿行業的要求。市場研究公司?Yole?根 據產品的終端應用特點,將為追求最優計算性能而采 用的先進封裝平臺技術歸類為高端性能封裝,高端性 能封裝主要包括超高密度扇出型封裝(UHD FO)、嵌 入硅橋技術、2.5D?硅轉接板技術、3D?存儲堆疊和混合 鍵合技術。加入封測行業交流群,加VX:tuoke08。2021—2026?年,全球封裝市場總額預計將 達到?960?億美元,復合年增長率保持在?3.8%。同時, 先進封裝的營收將超過傳統封裝。而以?FO、2.5D?和?3D?封裝為代表的高端性能封裝,在人工智能、5G?通信 和高性能計算等產業的推動下,其復合年增長率將超 過?10%,呈現高速增長的態勢。?

本文介紹了高端性能封裝的主要技術形式,剖析 了其結構的特點,分析了其在設計、工藝和可靠性測 試方面所面臨的挑戰。?

2?高端性能封裝的結構 ? ?

高端性能封裝主要以追求最優化計算性能為目的,其結構主要以?UHD FO、2.5D?和?3D?先進封裝為 主。在上述封裝結構中,決定封裝形式的主要因素為 價格、封裝密度和性能等。?

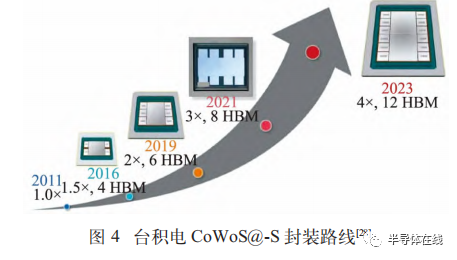

由?TSMC?在先進封裝上的主要業務可知,推動高 端性能封裝的主要項目為高性能計算與高帶寬存儲, 其代表結構為基于硅轉接板的芯片在晶圓基板上的 封裝(CoWoS@-S),是一種典型的?2.5D?封裝結構。該 結構將處理芯片和存儲芯片平鋪在硅轉接板上,采用 線寬?/?線間距為?0.4?μm /0.4?μm?的金屬布線將其互 連。TSMC?突破光罩對硅轉接板面積的限制,結合集成 芯片的數量,制定了其在?2.5D?封裝上的發展路線。?Intel?和?Samsung?在?2.5D?封裝上,也具有類似的封裝結構。對于?2.5D?封裝而言,硅轉接板可提供亞微米 級高密度布線,能夠顯著提升多芯片的組裝密度。隨 著高帶寬存儲芯片的數據傳輸效率逐步提升,采用?2.5D?封裝連接存儲芯片和處理器芯片將成為主流的 選擇。然而,硅轉接板采用前道晶圓制造的設備和工 藝,制作成本相對昂貴。為此,一些企業在?FO?封裝的 基礎上進一步深耕,開發出多樣化的結構,以滿足一 些稍低端產品的需求。

FO?通過晶圓重構技術,將多顆相同或不同的芯 片靈活組合起來,以實現多芯片集成的目的。在此基 礎上,FO?采用高密度布線有機層、硅橋和高速基板等 來提升器件的性能,衍生出了?2D、2.1D、2.2D?和?2.3D?封裝結構,以實現超高密度?I/O?的連接。由于?FO?主要采用高分子材料來制造芯片間的微米級布線,其 自身的線寬?/?間距的尺寸極限也相對明顯。為進一步 縮小?FO?封裝的布線尺寸,新的設備與材料有待開發, 同時,封裝成本也將大大提高。因此,FO?封裝主要應 用在性能相對較低的存儲器與處理器芯片上。?

在高端性能封裝中,處理芯片和存儲芯片對高帶 寬、低延遲有嚴格的要求,3D?封裝是最理想的方案。目 前,常見的?3D?封裝結構為存儲芯片間垂直互連以及 存儲芯片與邏輯芯片間的連接。在上述結構中,除采 用微凸點的芯片堆疊(C2C)和晶圓上芯片(C2W)工藝 外,基于硅通孔和混合鍵合(HB)的無凸點工藝實現了 異構異質芯片間的最短距離互連,將器件性能提至最 優,其投資成本也最高。預計在?2023?年,TSMC?采 用?HB?的集成芯片系統封裝(SoIC)將率先實現量產。?

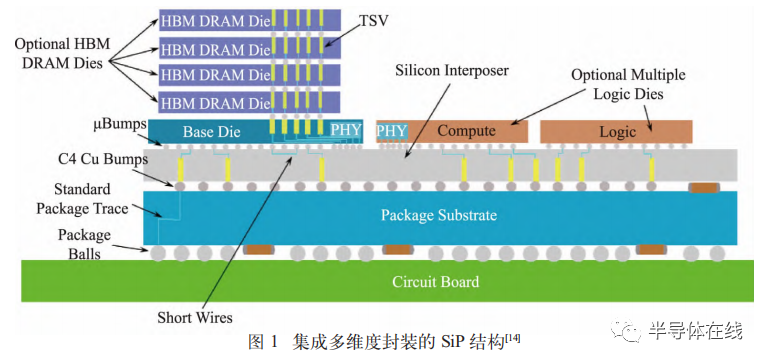

隨著高端性能封裝技術的發展,不同維度封裝結 構間的界限將變得模糊,將其集合成一個系統的?SiP?會變得普遍,圖?1?為集成多維度封裝的?SiP?結構示意 圖。例如?Intel?的最新產品?Ponte Vecchio?集成了嵌入 式多芯片互連橋接技術(EMIB)和邏輯晶圓?3D?堆疊 技術(Foveros);TSMC?的?SoIC?也可與?CoWoS?和集成 扇出型疊層封裝(InFO-PoP)相結合并共同使用。上述 結構可以實現器件對性能的極致追求,同時,多顆處 理芯片的集成也為器件的熱耗散帶來巨大挑戰。?

3?高端性能封裝的通信協議與設計? ? ?

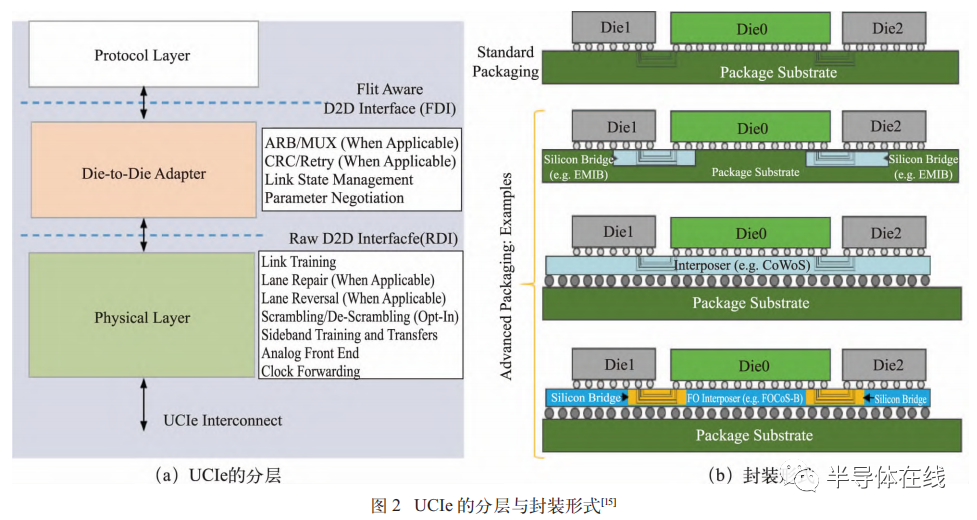

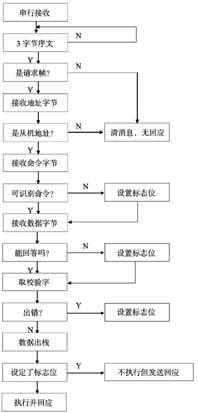

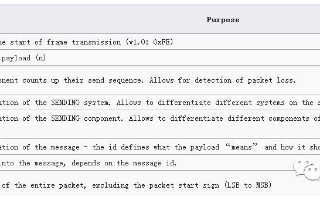

在高端性能封裝結構中,多顆特定功能的芯片(Die)被集成在單個系統之中,上述芯片的連接已成為 迫切需要解決的問題。Intel?公司開發了一種開放性的 通用小芯片互連技術(UCIe),為異構的小芯片間提供 了高帶寬、低延遲、高電源效率和高性價比的封裝連接。該標準結合外圍元器件互連總線標準(PCIe)、計 算鏈接協議(CXL)和軟件基礎設施來確保互操作性, 使得設計者能夠對不同來源的芯片進行封裝,UCIe?的 分層與封裝形式如圖?2?所示。

UCIe?技術標準提供了協議層、適配器和物理層。芯片與芯片間的適配器為?Chiplet?提供鏈路狀態管理 和參數協商。物理層提供電信號、時鐘、鏈路訓練、邊 帶、電路架構和封裝互連通道等。上述技術適用于標 準的?2D?封裝和先進的?2.5D?封裝。在先進的高端性能 封裝中,處理芯片對信道寬度最為敏感,其與存儲芯 片的數據發射與接收端沿芯片的邊緣放置,雙向的導 線長度也保持一致,這樣不僅簡化了電路設計,還大 大降低了信道帶寬的損耗。隨著處理芯片對帶寬要求 的進一步提升,存儲芯片的?3D?封裝得到發展,與之相 應的?UCIe?標準還需不斷升級,擴展到?3D?封裝互連。?

在國內,中國計算機互連技術聯盟聯合數+家企 業和科研院所制定了應用計算機系統芯片內、芯片 間、系統間互連技術的協議規范和標準,即《小芯片接 口總線技術要求》。該標準描述了處理芯片、人工智 能芯片、網絡處理器和網絡交換芯片等應用場景的小 芯片接口總線技術要求,通過對鏈路層、適配層、物理 層進行詳細定義,實現小芯片之間的互連互通。上述 標準于?2022?年?12?月發布,為?Chiplet?的芯片設計和封 裝打下了基礎,其在高端性能封裝中的應用尚未有報道。

4?高端性能封裝的電連接結構與工藝? ? ?

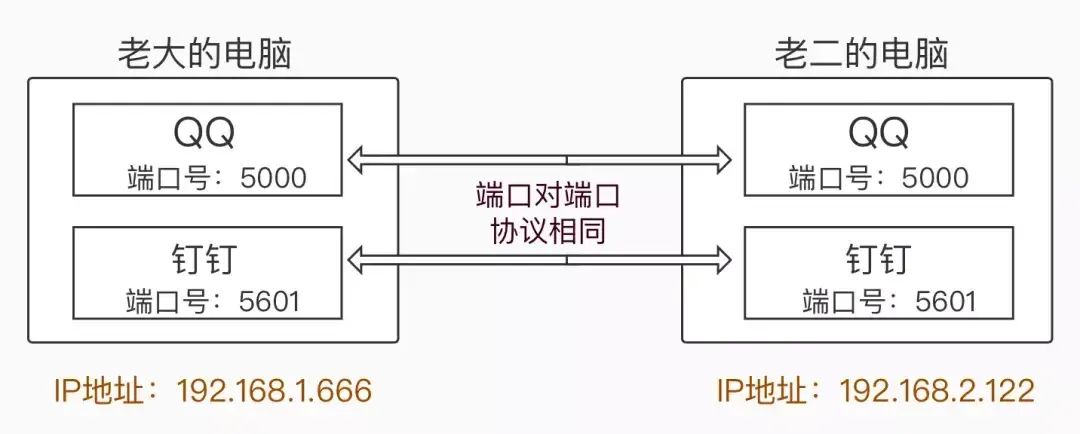

傳統的通信協議可用于規定芯片封裝的?I/O?設 置,其中,最常用的是?PCIe。芯片間的帶寬速率每?4?年 增加?1?倍,迫使芯片需要更多的?I/O,與之相應的封裝 互連結構需要逐年縮小。在高端性能封裝中,芯片的?I/O?數目隨著芯片技術節點的推進不斷增多,與之相 應的連接結構主要為凸點、高密度布線和中介層。

4.1?高端性能封裝的凸點結構

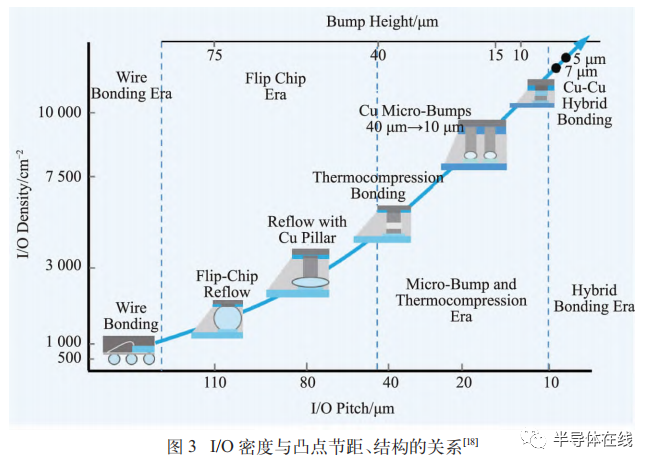

I/O?密度與凸點節距、結構的關系如圖?3?所示,傳 統的可控塌陷芯片連接焊球已無法滿足高端性能封 裝對高密度?I/O?的要求,取而代之的是節距小于?100μm?的微凸點。目前,常用的微凸點連接結構有銅-錫-銅、 鎳-錫-鎳、銅-錫-鎳、銅-鎳-錫-鎳-銅和銅-銅。在 熱壓鍵合工藝中,微凸點的最小節距甚至可以縮小至?10?μm,混合鍵合工藝又使凸點節距小于?10?μm。除 晶圓間的混合鍵合外,C2C?和?C2W?混合鍵合技術在 近年來受到青睞。除可獲得最優的電性能外,該技術 可選擇已知合格芯片進行貼片,以提升整體良率,降 低制造成本。由于?C2C?和?C2W?混合技術涉及晶圓切 割,如何保護化學機械拋光后的芯片表面免受污染、 同時提升鍵合界面的強度問題仍需解決。已有的報道 在切割過程中采用光刻膠遮住芯片表面,再采用等離 子體進行后處理,產品的封裝良率尚無法滿足工業批 量生產的要求,上述問題有待更多的研究。

4.2?高端性能封裝的高密度布線?

在高密度布線方面,2.5D?與?3D?封裝可以與前道 晶圓制造共用已成熟的制程,其線寬?/?間距在微米級 以下,達到最高的布線密度。以?FO?為基礎的?2D、?2.1D、2.2D?和?2.3D?封裝更接近封測企業的制程。FO?將芯片埋入模塑料中以重構晶圓,大量的模塑料不僅 不利于器件的散熱,還與芯片間存在熱失配的問題, 導致晶圓發生嚴重的翹曲,同時,包裹金屬布線的高 分子介電層又加劇了上述現象,給工藝帶來了較大挑戰。除晶圓翹曲外,模塑料在成形過程中收縮,帶動 芯片偏離設定位置,造成曝光偏移,不利于高密度布 線的制作,需要新的設備投入。作為?FO?封裝的重要 連接結構,高密度布線在工藝上亦存在較高難度。特 別在多層布線的制作過程中,底層布線的拱起妨礙上 層光刻膠的曝光和刻蝕,造成布線缺陷。金屬布線在 電鍍后的種子層過刻蝕亦會造成其與介電層的剝離。目前,在?FO?封裝結構中,4?層布線寬度?/?間距為?5?μm / 5?μm?的產品已進入量產階段,同時,布線寬度?/?間距 的尺寸極限為?1?μm /1?μm,層數最多為?6?層,難以滿 足更高?I/O?密度的芯片間連接。據報道,有學者采用 聚酰亞胺的大馬士革工藝來制作亞微米布線,提升介 電層層數,上述研究尚未在量產中廣泛應用。?

4.3?高端性能封裝的中介層?

在高端性能封裝中,中介層作為重要的連接結 構,可大幅提高芯片的集成度。目前,中介層按材料成 分分為有機中介層與無機中介層。其中,有機中介層 主要采用高分子材料制作高密度布線,將其置于芯片 與基板之間,作為?2.5D?硅轉接板的一種廉價的替代方 案,同時降低了在基板上制造細線寬?/?窄間距布線的 難度,如?Samsung?開發出的制板級封裝轉接板和TSMC?基于?FO?的集成基板。

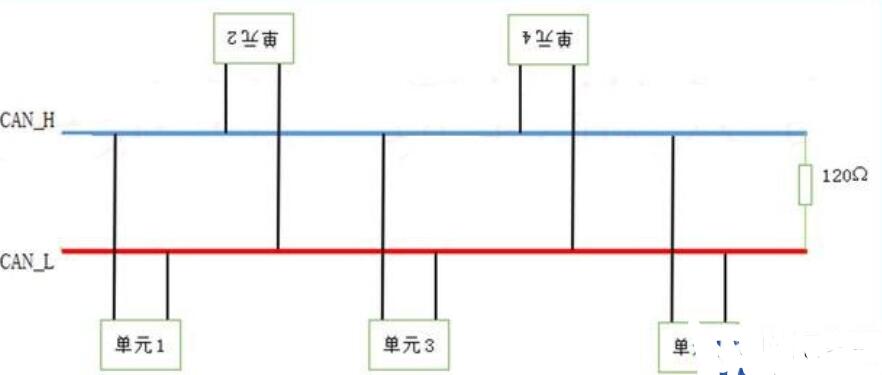

無機中介層包括硅橋、硅轉接板和玻璃轉接板。在高帶寬存儲芯片和處理芯片間,存在局部的高密度 連接。Intel?根據上述結構特點,開發出硅橋結構,將其 埋入基板,僅連接高密度?I/O?部分,其余的布線連接由基板完成。部分企業則將硅橋與?FO?封裝相結合,開 發出新的封裝結構。據日月光的報道,與布線寬度?/?間 距為?0.8?μm /0.8?μm?的?2.5D?封裝相比,采用布線線寬/?間距為?2?μm /2?μm?的嵌入硅橋的扇出型基板上芯片 封裝(FOCoS-B)表現出更優的電性能。在?2.5D?封裝 中,硅轉接板為芯片平面互連提供了媒介。臺積電?CoWoS@-S?封裝路線如圖?4?所示,按照?TSMC?推出的 存儲芯片與邏輯芯片的組合方式,2023?年硅轉接板的 平面面積將達到?2011?年轉接板面積的?4?倍,如何將大 尺寸的轉接板貼在基板之上而無貼片偏移和虛焊等 問題尚待解決。另外,硅作為一種半導體材料,不利 于信號的傳輸與完整性保持。TSMC?通過在硅轉接板 上制作電容以彌補上述不足,但金屬布線形成的電容 容量有限,無法滿足廣泛的應用需求。近年來,有學 者提出采用絕緣材料如玻璃替換硅,而在玻璃轉接板 上制作多層亞微米級布線并提高集成度仍需要進一步探索。

5?高端性能封裝的可靠性?? ? ?

在高端性能封裝中,產品常常采用疊層結構,且 存在大量用于信號連接的微結構,這使得封裝體具有 多材料、多界面和尺寸跨度大等特點,其在熱、力和電 學方面均存在較大的挑戰。?

5.1?高端性能封裝中的熱失配問題?

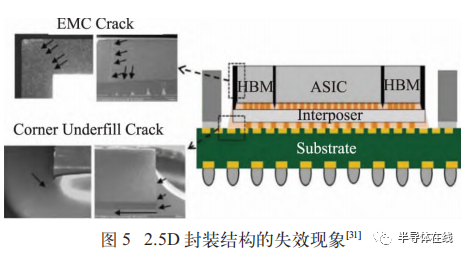

在高端性能封裝中,芯片主材硅、金屬和高分子 材料間的熱失配問題普遍存在,由此導致封裝結構在 邊角處出現焊球疲勞、模塑料開裂和底填料界面分層 等現象,2.5D?封裝結構的失效現象如圖?5?所示。在 上述問題中,FO?封裝在降低焊球熱疲勞方面具有優勢,大量的模塑料使得結構的熱膨脹系數增大至接近 基板的水平,兩者在熱脹冷縮過程中保持協調變形, 焊球的應力降低,使得結構在可靠性測試時表現良好。同時,模塑料的比重小,降低了焊球在振動與跌 落過程中的慣性,有助于封裝結構在上述測試時保持 完整。相比于?FO?封裝,2.5D?和?3D?封裝的疊層結構自 身比重大,不僅不利于散熱,而且其與基板間協調變 形的難度增加了,不斷增大的?2.5D?硅轉接板尺寸加劇 了該現象。此外,采用模塑料對?FO、2.5D?和?3D?封裝產 品進行外保護,硅芯片與模塑料間會由于熱失配導致 模塑料開裂,事先使用有限元工具對模塑料的材料進 行選擇是一種合適的解決方案。

5.2?微結構的熱電遷移?

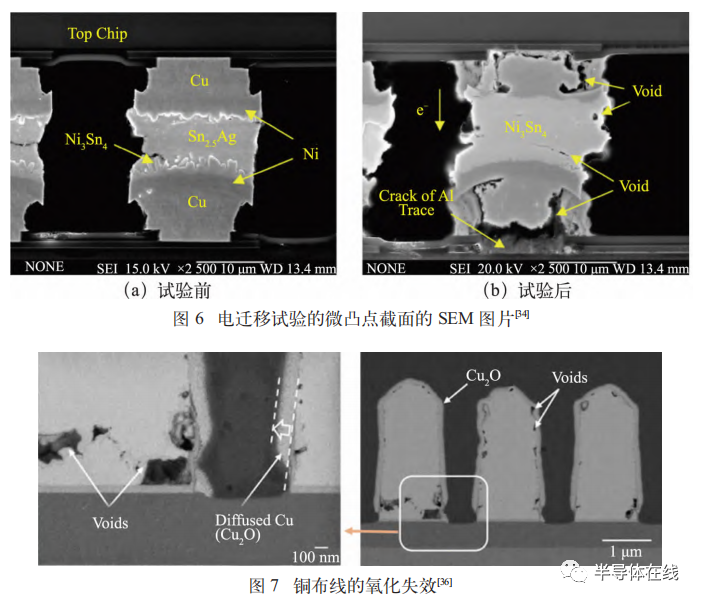

隨著封裝尺寸的不斷縮小,微凸點和高密度布線 作為高端性能封裝的重要電連接結構,其熱電遷移問 題日益突出。在高性能產品的?2.5D?和?3D?封裝中,微 凸點的直徑(10~20?μm)比傳統的焊球縮小一個數量 級。在?0.05 A?的小電流條件下,通過結構橫截面的電 流密度約為?104A/cm2,接近錫層電遷移發生的閾值。此外,在產品服役過程中,結構中的錫、銀將完全轉化 為金屬間化合物,造成體積收縮和柯肯達爾孔洞,加 速結構的失效,電遷移試驗的微凸點截面的?SEM?圖 片如圖6?所示。?

與微凸點的熱電遷移相似,處理芯片與高帶寬存 儲芯片間的高密度布線亦存在上述問題,且處理芯片 工作時溫度高達?100?℃,其與存儲芯片間的溫度梯度 加速了上述現象的發生。在?FO?封裝中,金屬銅布線被 包裹在高分子鈍化層中,使得其表面發生氧化、生成 氧化銅,銅布線的氧化失效如圖?7?所示。在銅氧化的 過程中,銅不斷向表面遷移,使得銅與氧化銅界面處 存在大量孔洞。在高溫和大電流的作用下,上述氧化 現象更加明顯,形成的大量孔洞嚴重影響布線強度與信號傳輸。一些研究采用非有機材料在銅表面形成保護層,將銅與高分子材料隔離,防止其氧化,由此導致 的新工藝增加了額外的制造成本。

5.3?封裝體的散熱問題?

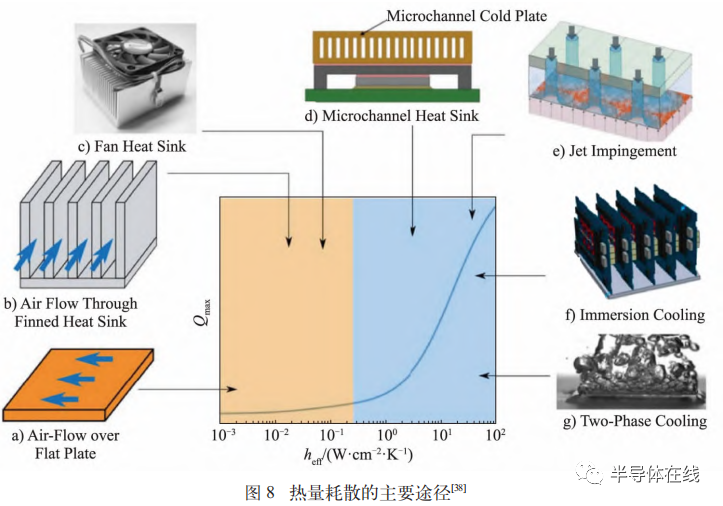

為追求最優的計算性能,處理芯片的技術節點不 斷向前推進,集成的晶體管數量激增,與此同時,封裝 的集成度進一步提高,要求封裝體能夠為處理芯片提 供熱流密度高達?1 000 W/cm2的熱量耗散能力。在高 端性能封裝中,UHD FO、2.5D?和?3D?封裝最終與基板貼合 , 一 般的組裝 方 式 為 倒 裝 芯 片 球 柵 陣 列 (FCBGA)。該封裝的主要散熱途徑為背部熱沉,一些 學者通過優化其設計,采用水冷、氣液?2?相、風冷等方 式進行散熱,優化結構的最大熱耗散功率(Qmax)與有 效傳熱系數(heff)間的關系,以滿足不同產品的應用需 求,熱量耗散的主要途徑如圖?8?所示。

在?FCBGA?結構中,影響散熱的另一重要因素為 熱界面材料的選擇。相比于傳統的硅質材料,低熔點的金屬材料更受到青睞,如銦、銦-銀、錫和液態金屬, 上述材料具有較大的導熱系數,能夠及時傳遞處理芯片工作時的熱量。然而,基板焊球的回流焊會使這 些低熔點的材料再熔化,由此導致的孔洞與外溢問題 尚待有效解決。為進一步滿足散熱的需求,更加優質 的熱界面材料有待開發,如石墨。除上述熱沉和熱界 面材料的選擇外,有研究者也通過優化邏輯芯片與存 儲芯片的疊層方式、FCBGA?的空腔大小等方式獲得部分熱性能的改進。?

6 結束語 ? ?

高性能計算、人工智能、云計算、數據中心和?5G?通信等領域的快速發展推動芯片技術向高性能、高帶 寬的方向發展,由此導致單顆?SoC?的技術節點不斷向 前推進,集成功能愈發復雜,制造成本不斷攀升。一些 廠商將?SoC?的存儲單元與處理單元分離出來,再經由?UHD FO、2.5D?和?3D?封裝方式進行重新組合,以實現最優的計算性能。高端性能封裝能夠較好地滿足處理 芯片日益增長的?I/O?密度、散熱能力等的要求,有望得 到更多的關注和研究。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論