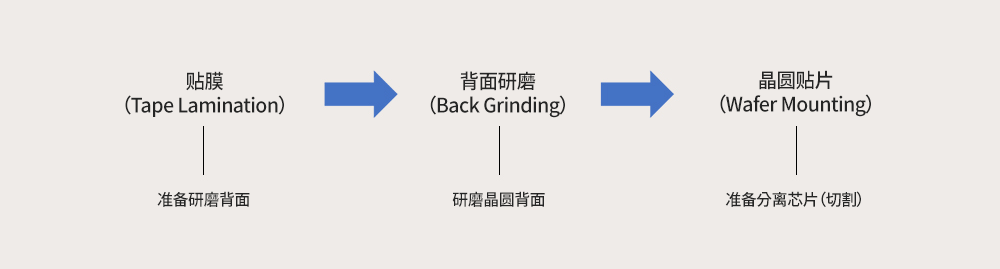

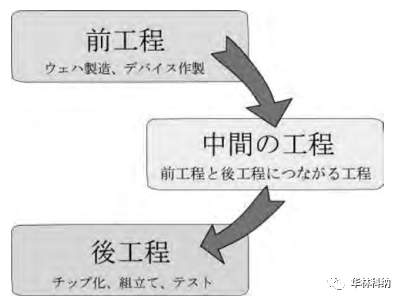

作為半導(dǎo)體制造的后工序,封裝工藝包含背面研磨(Back Grinding)、劃片(Dicing)、芯片鍵合(Die Bonding)、引線鍵合(Wire Bonding)及成型(Molding)等步驟。

2023-03-27 09:33:37 7225

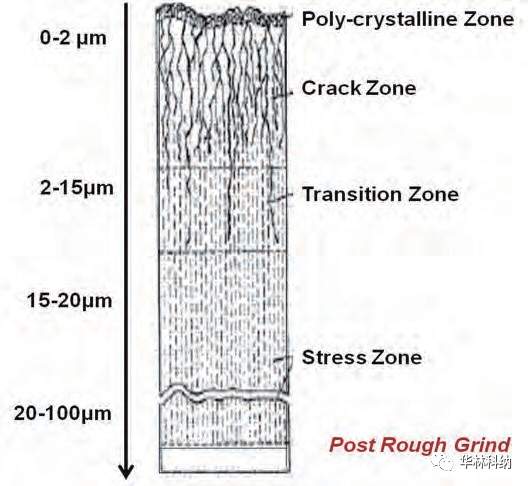

7225 經(jīng)過前端工藝處理并通過晶圓測試的晶圓將從背面研磨(Back Grinding)開始后端處理。背面研磨是將晶圓背面磨薄的工序,其目的不僅是為了減少晶圓厚度,還在于聯(lián)結(jié)前端和后端工藝以解決前后兩個工藝

2023-05-12 12:39:18 764

764

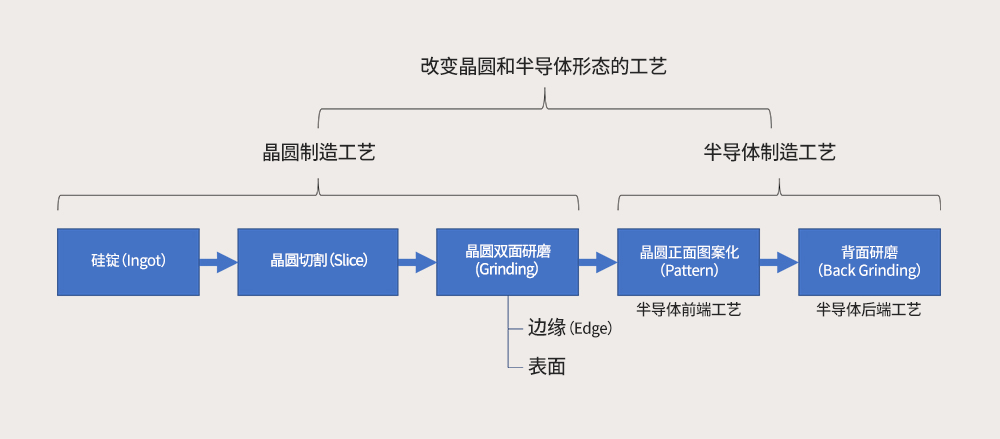

一些后處理步驟,例如研磨、化學(xué)機械研磨(CMP)、SiC外延、注入、檢測、化學(xué)氣相沉積(CVD)和物理氣相沉積(PVD)。SiC晶圓因其半透明性質(zhì)和材料硬度而面臨許多挑戰(zhàn),這需要對關(guān)鍵工藝步驟設(shè)備進行

2019-05-12 23:04:07

小弟想知道8寸晶圓盒的制造工藝和檢驗規(guī)范,還有不知道在大陸有誰在生產(chǎn)?

2010-08-04 14:02:12

在庫存回補需求帶動下,包括環(huán)球晶、臺勝科、合晶、嘉晶等硅晶圓廠第二季下旬出貨續(xù)旺,現(xiàn)貨價出現(xiàn)明顯上漲力道,合約價亦確認(rèn)止跌回升。 新冠肺炎疫情對半導(dǎo)體材料的全球物流體系造成延遲影響,包括晶圓

2020-06-30 09:56:29

晶圓凸點模板技術(shù)和應(yīng)用效果評價詳細(xì)介紹了晶圓凸點目前的技術(shù)現(xiàn)狀,應(yīng)用效果,通過這篇文章可以快速全面了解晶圓凸點模板技術(shù)晶圓凸點模板技術(shù)和應(yīng)用效果評價[hide][/hide]

2011-12-02 12:44:29

` 晶圓級封裝是一項公認(rèn)成熟的工藝,元器件供應(yīng)商正尋求在更多應(yīng)用中使用WLP,而支持WLP的技術(shù)也正快速走向成熟。隨著元件供應(yīng)商正積極轉(zhuǎn)向WLP應(yīng)用,其使用范圍也在不斷擴大。 目前有5種成熟

2011-12-01 14:33:02

有沒有能否切割晶圓/硅材質(zhì)濾光片的代工廠介紹下呀

2022-09-09 15:56:04

`晶圓切割目的是什么?晶圓切割機原理是什么?一.晶圓切割目的晶圓切割的目的,主要是要將晶圓上的每一顆晶粒(Die)加以切割分離。首先要將晶圓(Wafer)的背面貼上一層膠帶(Wafer Mount

2011-12-02 14:23:11

`晶圓制造總的工藝流程芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構(gòu)裝工序(Packaging)、測試工序(Initial

2011-12-01 15:43:10

+ 4HNO3 + 6 HF? 3H2SiF6 +4 NO + 8H2O 拋光:機械研磨、化學(xué)作用使表面平坦,移除晶圓表面的缺陷八、晶圓測試主要分三類:功能測試、性能測試、抗老化測試。具體有如:接觸測試

2019-09-17 09:05:06

`微晶片制造的四大基本階段:晶圓制造(材料準(zhǔn)備、長晶與制備晶圓)、積體電路制作,以及封裝。晶圓制造過程簡要分析[hide][/hide]`

2011-12-01 13:40:36

晶圓制造的基礎(chǔ)知識,適合入門。

2014-06-11 19:26:35

`一、摩爾定律與硅芯片的經(jīng)濟生產(chǎn)規(guī)模 大多數(shù)讀者都已經(jīng)知道每個芯片都是從硅晶圓中切割得來,因此將從芯片的生產(chǎn)過程開始討論。下面,是一幅集成芯片的硅晶圓圖像。(右邊的硅晶圓是采用0.13微米制程P4

2011-12-01 16:16:40

晶圓是指硅半導(dǎo)體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結(jié)構(gòu),而成為有特定電性功能之IC產(chǎn)品。晶圓的原始材料是硅,而地殼表面有用之不竭的二氧化硅

2011-12-01 14:53:05

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合,即是通過化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達(dá)到密封效果。如下

2021-02-23 16:35:18

` 誰來闡述一下晶圓有什么用?`

2020-04-10 16:49:13

本人想了解下晶圓制造會用到哪些生產(chǎn)輔材或生產(chǎn)耗材

2017-08-24 20:40:10

晶圓的制造過程是怎樣的?

2021-06-18 07:55:24

` 硅是由石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造積體電路的石英半導(dǎo)體的材料,經(jīng)過照相制版,研磨,拋光,切片等程序,將多晶硅融解拉出單晶硅晶棒

2011-09-07 10:42:07

`晶圓的結(jié)構(gòu)是什么樣的?1 晶格:晶圓制程結(jié)束后,晶圓的表面會形成許多格狀物,成為晶格。經(jīng)過切割器切割后成所謂的晶片 2 分割線:晶圓表面的晶格與晶格之間預(yù)留給切割器所需的空白部分即為分割線 3

2011-12-01 15:30:07

晶圓級CSP的返修工藝包括哪幾個步驟?晶圓級CSP對返修設(shè)備的要求是什么?

2021-04-25 08:33:16

細(xì)間距的晶圓級CSP時,將其當(dāng)做倒裝晶片并采用助焊劑浸蘸的方法進行組裝,以取代傳統(tǒng)的焊膏印刷組裝,如圖2所示,首先將晶圓級CSP浸蘸在設(shè)定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關(guān)于錫膏裝配和助焊劑裝配的優(yōu)缺點。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

; ·尺寸和位置精度受阻焊膜窗口的影響,不適合密間距元件的裝配。 NSMD焊盤的尺寸和位置不受阻焊膜窗口的影響,在焊盤和阻焊膜之間有一定空隙,如圖2和圖3所示。對于 密間距晶圓級CSP,印刷電路板上的焊盤

2018-09-06 16:32:27

晶圓級CSP裝配回流焊接工藝控制,看完你就懂了

2021-04-25 06:28:40

晶圓級CSP的裝配對貼裝壓力控制、貼裝精度及穩(wěn)定性、照相機和影像處理技術(shù)、吸嘴的選擇、助焊劑應(yīng) 用單元和供料器,以及板支撐及定位系統(tǒng)的要求類似倒裝晶片對設(shè)備的要求。WLCSP貼裝工藝的控制可以參

2018-09-06 16:32:18

晶圓級封裝技術(shù)源自于倒裝芯片。晶圓級封裝的開發(fā)主要是由集成器件制造廠家(IBM)率先啟動。1964年,美國IBM公司在其M360計算器中最先采用了FCOB焊料凸點倒裝芯片器件。

2020-03-06 09:02:23

晶圓級封裝類型及涉及的產(chǎn)品

2015-07-11 18:21:31

晶圓級芯片封裝技術(shù)是對整片晶圓進行封裝測試后再切割得到單個成品芯片的技術(shù),封裝后的芯片尺寸與裸片一致。

2019-09-18 09:02:14

(Engineering die,test die):這些芯片與正式器件(或稱電路芯片)不同。它包括特殊的器件和電路模塊用于對晶圓生產(chǎn)工藝的電性測試。(4)邊緣芯片(Edge die):在晶圓的邊緣上的一些掩膜殘缺不全

2020-02-18 13:21:38

晶圓針測制程介紹 晶圓針測(Chip Probing;CP)之目的在于針對芯片作電性功能上的 測試(Test),使 IC 在進入構(gòu)裝前先行過濾出電性功能不良的芯片,以避免對不良品增加制造成

2020-05-11 14:35:33

`159-5090-3918回收6寸晶圓,8寸晶圓,12寸晶圓,回收6寸晶圓,8寸晶圓,12寸晶圓,花籃,Film Fram Cassette,晶元載具Wafer shipper,二手晶元盒

2020-07-10 19:52:04

請問有人用過Jova Solutions的ISL-4800圖像測試儀嗎,還有它可否作為CIS晶圓測試的tester,謝謝!

2015-03-29 15:49:20

晶圓級芯片級封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

工藝,制造出各種性能優(yōu)異、價格低廉、微型化的傳感器、執(zhí)行器、驅(qū)動器和微系統(tǒng)。SITIME MEMS電子發(fā)燒友振是由MEMS電子發(fā)燒友圓與CMOS晶圓上下疊加而成,而CMOS晶圓則包括了NON

2017-04-06 14:22:11

SiC SBD 晶圓級測試 求助:需要測試的參數(shù)和測試方法謝謝

2020-08-24 13:03:34

新加坡知名半導(dǎo)體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設(shè)備主管!此職位為內(nèi)部推薦,深刻蝕工藝工程師需要有LAM 8寸機臺poly刻蝕經(jīng)驗。刻蝕設(shè)備主管需要熟悉LAM8寸機臺。待遇優(yōu)厚。有興趣的朋友可以將簡歷發(fā)到我的郵箱sternice81@gmail.com,我會轉(zhuǎn)發(fā)給HR。

2017-04-29 14:23:25

【六寸晶圓金屬化工藝主管】崗位職責(zé):1、負(fù)責(zé)減少背金、鍍膜工序的工藝缺陷,改進工藝條件,維護工藝的穩(wěn)定性,提高成品率;2、提出并實現(xiàn)優(yōu)化工藝條件等方法,提高生產(chǎn)效率,保證產(chǎn)能需求;3、協(xié)助設(shè)備工程師

2016-10-08 09:55:38

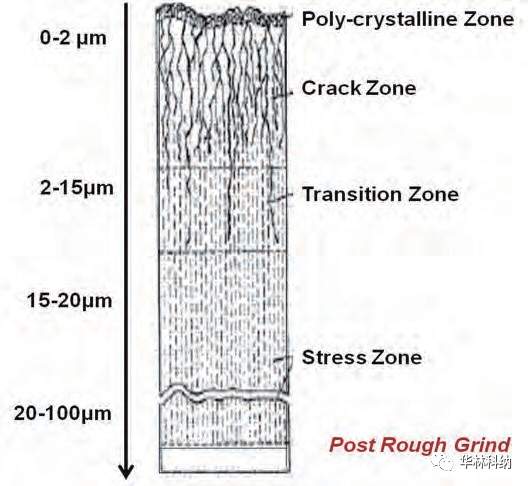

無法聚焦一樣。平整和拋光的工藝分兩步:磨片和化學(xué)機械拋光。磨片是一個傳統(tǒng)的磨料研磨工藝,精調(diào)到半導(dǎo)體使用的要求。磨片的主要目的是去除切片工藝殘留的表面損傷。至此,就生產(chǎn)出了表面平整的晶圓。`

2018-07-04 16:46:41

納米到底有多細(xì)微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

` 晶圓是指硅半導(dǎo)體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結(jié)構(gòu),而成為有特定電性功能之IC產(chǎn)品。晶圓的原始材料是硅,而地殼表面有用之不竭的二氧化硅

2011-12-01 11:40:04

的輔助。 測試是為了以下三個目標(biāo)。第一,在晶圓送到封裝工廠之前,鑒別出合格的芯片。第二,器件/電路的電性參數(shù)進行特性評估。工程師們需要監(jiān)測參數(shù)的分布狀態(tài)來保持工藝的質(zhì)量水平。第三,芯片的合格品與不良品

2011-12-01 13:54:00

` 晶圓電阻又稱圓柱型精密電阻、無感晶圓電阻、貼片金屬膜精密電阻、高精密無感電阻、圓柱型電阻、無引線金屬膜電阻等叫法;英文名稱是:Metal Film Precision Resistor-CSR

2011-12-02 14:57:57

`晶圓級封裝(WLP)就是在其上已經(jīng)有某些電路微結(jié)構(gòu)(好比古董)的晶片(好比座墊)與另一塊經(jīng)腐蝕帶有空腔的晶片(好比玻璃罩)用化學(xué)鍵結(jié)合在一起。在這些電路微結(jié)構(gòu)體的上面就形成了一個帶有密閉空腔的保護

2011-12-01 13:58:36

半導(dǎo)體晶圓(晶片)的直徑為4到10英寸(10.16到25.4厘米)的圓盤,在制造過程中可承載非本征半導(dǎo)體。它們是正(P)型半導(dǎo)體或負(fù)(N)型半導(dǎo)體的臨時形式。硅晶片是非常常見的半導(dǎo)體晶片,因為硅

2021-07-23 08:11:27

制作,而且廠家生產(chǎn)晶振的原材料還用好的國外進口。 2、晶片制成流程規(guī)范;X光機角-粘板-多刀切割-改圓-研磨-粘坨-磨外形-圓邊-頻率分選-清洗腐蝕-分選 3、嚴(yán)格把控石英晶體成品制成流程;清洗

2021-03-15 13:53:46

1、為什么晶圓要做成圓的?如果做成矩形,不是更加不易產(chǎn)生浪費原料?2、為什么晶圓要多出一道研磨的工藝?為什么不能直接做成需求的厚度?

2014-01-20 15:58:42

宜特檢測不僅可以提供一般剖面研磨(Cross-section),也提供樣品從背面進行研磨(晶背研磨,Backside Polishing),將基材磨至特定的厚度后再進行拋光。剖面、斷面研磨與晶背研磨

2018-09-11 10:24:52

單晶的晶圓制造步驟是什么?

2021-06-08 06:58:26

的有氧化爐、沉積設(shè)備、光刻機、刻蝕設(shè)備、離子注入機、清洗機、化學(xué)研磨設(shè)備等。以上是今日Enroo關(guān)于晶圓制造工藝及半導(dǎo)體設(shè)備的相關(guān)分享。

2018-10-15 15:11:22

is not preferred; instead, use ‘back surface’.)背面 - 晶圓片的底部表面。(注:不推薦該術(shù)語,建議使用“背部表面”)Base Silicon Layer

2011-12-01 14:20:47

找了一圈,發(fā)現(xiàn)做線鍵合機的比較多,想知道做晶圓鍵合wafer bonding的中國廠家。

2021-04-28 14:34:57

`所謂多項目晶圓(簡稱MPW),就是將多種具有相同工藝的集成電路設(shè)計放在同一個硅圓片上、在同一生產(chǎn)線上生產(chǎn),生產(chǎn)出來后,每個設(shè)計項目可以得到數(shù)十片芯片樣品,這一數(shù)量足夠用于設(shè)計開發(fā)階段的實驗、測試

2011-12-01 14:01:36

服務(wù)。其雙軸劃片功能可同時兼顧正背面劃片質(zhì)量,加裝二流體清洗功能可對CMOS Sensor等潔凈度要求較高組件,提供高質(zhì)量劃片服務(wù)。晶圓劃片機為廠內(nèi)自有,可支持至12吋晶圓。同時,iST宜特檢測可提供您

2018-08-31 14:16:45

是什么推動著高精度模擬芯片設(shè)計?如何利用專用晶圓加工工藝實現(xiàn)高性能模擬IC?

2021-04-07 06:38:35

`各位大大:手頭上有顆晶圓的log如下:能判斷它的出處嗎?非常感謝!!`

2013-08-26 13:43:15

怎么選擇晶圓級CSP裝配工藝的錫膏?

2021-04-25 08:48:29

``揭秘切割晶圓過程——晶圓就是這樣切割而成芯片就是由這些晶圓切割而成。但是究竟“晶圓”長什么樣子,切割晶圓又是怎么一回事,切割之后的芯片有哪些具體應(yīng)用,這些可能對于大多數(shù)非專業(yè)人士來說并不是十分

2011-12-01 15:02:42

招聘6/8吋晶圓測試工藝工程師/主管1名工作地點:無錫工資:面議要求:1. 工藝工程師:晶圓測試經(jīng)驗3年以上,工藝主管:晶圓測試經(jīng)驗5年以上;2. 精通分立器件類產(chǎn)品晶圓測試,熟悉IC晶圓測試尤佳

2017-04-26 15:07:57

`各位大大:手頭上有顆晶圓的log如下:能判斷它的出處嗎?非常感謝!!`

2013-08-26 13:45:30

求晶圓劃片或晶圓分撿裝盒合作加工廠聯(lián)系方式:QQ:2691003439

2019-03-13 22:23:17

芯片封裝測試是對芯片的失效和可靠性進行測試嗎?網(wǎng)上有個這樣的流程:封裝測試廠從來料(晶圓)開始,經(jīng)過前道的晶圓表面貼膜(WTP)→晶圓背面研磨(GRD)→晶圓背面拋光(polish)→晶圓背面

2013-12-09 21:48:32

激光用于晶圓劃片的技術(shù)與工藝 激光加工為無接觸加工,激光能量通過聚焦后獲得高能量密度,直接將硅片

2010-01-13 17:01:57

的解決方案 泛林集團通過其獨有的Durendal?工藝解決這一問題。該工藝可以產(chǎn)出優(yōu)質(zhì)、光滑的大型銅柱頂部表面,整個晶圓上的大型銅柱高度也非常均勻。整套Durendal?工藝可以在SABRE? 3D設(shè)備上

2020-07-07 11:04:42

看到了晶圓切割的一個流程,但是用什么工具切割晶圓?求大蝦指教啊 ?

2011-12-01 15:47:14

%),接著是將這些純硅制成長硅晶棒,成為制造積體電路的石英半導(dǎo)體的材料,經(jīng)過照相制版,研磨,拋光,切片等程序,將多晶硅融解拉出單晶硅晶棒,然后切割成一片一片薄薄的晶圓。我們會聽到幾寸的晶圓廠,如果硅晶圓的直徑

2011-12-02 14:30:44

`背金工藝之前 ,背面如何處理? 最近做片時出現(xiàn)異常,如下圖中間靠下為異常區(qū)域,合金沒合好,請問如何避免,謝謝!!`

2011-01-07 11:10:24

的替代工藝。激光能對所有第III-V主族材料包括第IV主族材料如硅(Si)和鍺(Ge)的晶圓進行快速劃片。硅晶圓片,切口寬度均小于30微米,切口邊緣平直、精準(zhǔn)、光滑,沒有崩裂,尤其硅晶圓更是如此。電力

2010-01-13 17:18:57

刻劃LED刻劃線條較傳統(tǒng)的機械刻劃窄得多,所以使得材料利用率顯著提高,因此提高產(chǎn)出效率。另外激光加工是非接觸式工藝,刻劃帶來晶圓微裂紋以及其他損傷更小,這就使得晶圓顆粒之間更緊密,產(chǎn)出效率高、產(chǎn)能高

2011-12-01 11:48:46

` 集成電路按生產(chǎn)過程分類可歸納為前道測試和后到測試;集成電路測試技術(shù)員必須了解并熟悉測試對象—硅晶圓。測試技術(shù)員應(yīng)該了解硅片的幾何尺寸形狀、加工工藝流程、主要質(zhì)量指標(biāo)和基本檢測方法;集成電路晶圓測試基礎(chǔ)教程ppt[hide][/hide]`

2011-12-02 10:20:54

芯片背面研磨,上海IC研磨,IC集成電路研磨公司,宜特檢測集成電路背面研磨(Backside Polishing)工作原理:透過自動研磨機,從芯片背面進行研磨將Si基材磨薄至特定厚度后再進行拋光

2018-10-24 10:57:21

氧化鋯基氧化鋁 - 半導(dǎo)體晶圓研磨粉 (AZ) 系列半導(dǎo)體晶圓研磨粉是一種細(xì)粉磨料,是作為需要高精度的包裹材料而開發(fā)的。原材料粒度分布尖銳,粒度穩(wěn)定,形狀呈塊狀。再以熔融氧化鋁為原料,鋯英

2022-05-31 14:21:38

晶圓測溫系統(tǒng),晶圓測溫?zé)犭娕迹?b class="flag-6" style="color: red">晶圓測溫裝置一、引言隨著半導(dǎo)體技術(shù)的不斷發(fā)展,晶圓制造工藝對溫度控制的要求越來越高。熱電偶作為一種常用的溫度測量設(shè)備,在晶圓制造中具有重要的應(yīng)用價值。本文

2023-06-30 14:57:40

晶圓測溫系統(tǒng)tc wafer晶圓表面溫度均勻性測溫晶圓表面溫度均勻性測試的重要性及方法 在半導(dǎo)體制造過程中,晶圓的表面溫度均勻性是一個重要的參數(shù)

2023-12-04 11:36:42

裸光纖研磨鍍膜 裸光纖研磨鍍膜 250um光纖研磨

為了配光纖端面鍍膜工藝,獨立開發(fā)的一套裸光纖端面研磨拋光工藝,基于這個工藝可以獲得超高質(zhì)量的拋光端面,Zygo 干涉儀測量的結(jié)果表明

2021-10-22 09:22:11 706

706 在許多 IC 工藝輔助配件進行蝴蝶研磨(背面研磨、研磨),使裝片薄形化,例如:用巧克力蛋糕及智能封裝等。到200~40μm。在珍珠打磨之后,有許多產(chǎn)品需要進行工藝,包括:離子布植(離子實現(xiàn))、熱處理

2022-03-23 14:15:31 1096

1096

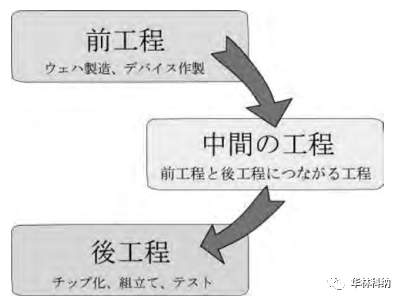

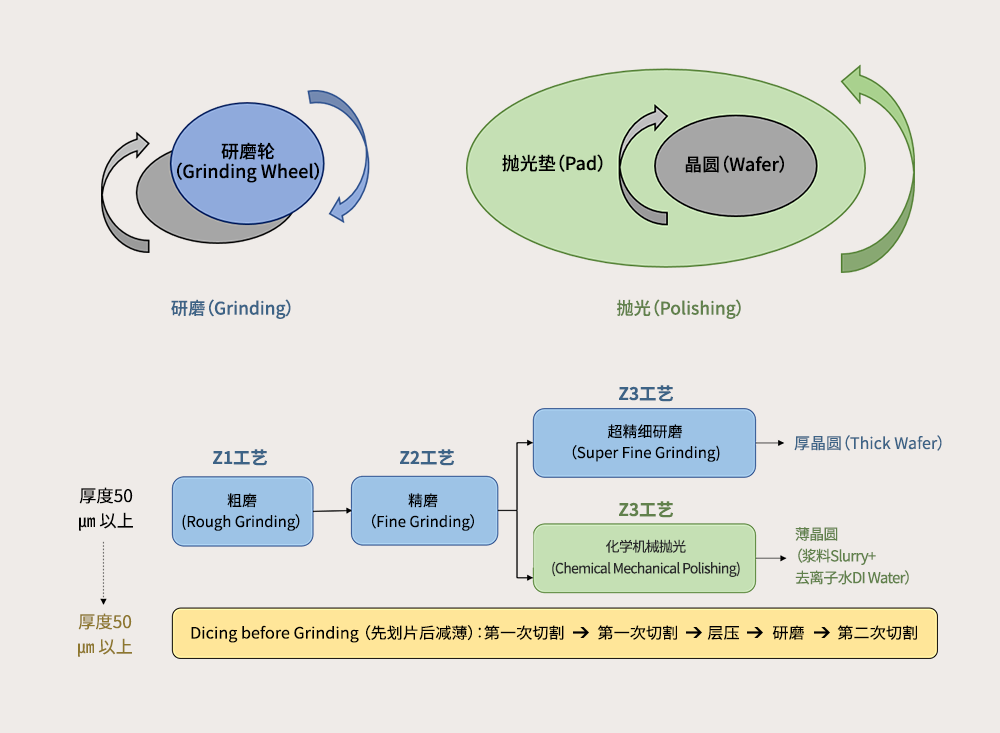

的變形,然后將晶片加工成鏡面。此外,存在用于使在前一工藝中制造的具有圖案的晶片的厚度均勻且薄的后研磨工藝。在背面研磨之后,在切割過程中進行芯片化,并且在后處理中進行安裝。研磨工藝和切割工藝是前一工藝和后一工藝之間的中間工藝,是提高附加值的中間工藝,如晶片減薄,應(yīng)力消除,以MEMS(微機電系統(tǒng)

2022-04-20 16:09:48 10872

10872

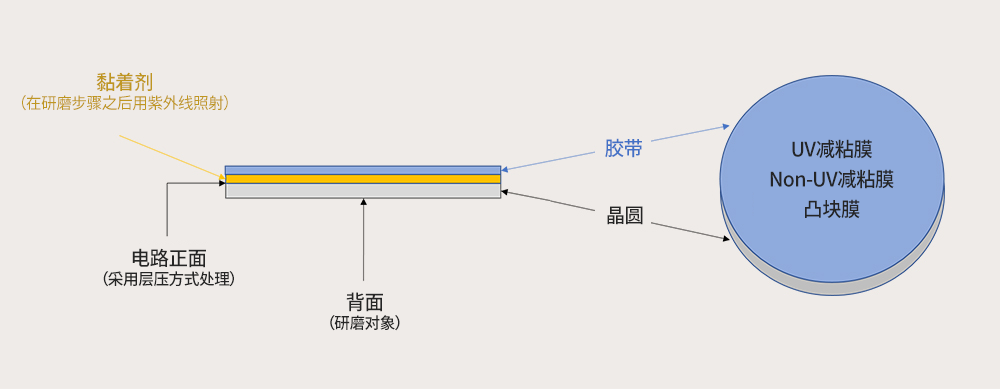

】晶圓 FOL– Back Grinding背面減薄 將從晶圓廠出來的Wafer進行背面研磨,來減薄晶圓達(dá)到 ? ?封裝需要的厚度(5mils~10mils); 磨片時,需要在正面(Active

2023-05-23 09:56:41 2144

2144

化學(xué)機械研磨工藝操作的基本介紹以及其比單純物理研磨的優(yōu)勢介紹。

2023-11-29 10:05:09 349

349

電子發(fā)燒友App

電子發(fā)燒友App

評論