CEA -Leti和英特爾今天宣布了一項聯合研究項目,旨在開發 300 毫米晶圓上二維過渡金屬二硫化物 (2D TMD) 的層轉移技術,目標是將摩爾定律擴展到 2030 年以后。

二維層狀半導體,例如基于鉬和鎢的 TMD,有望擴展摩爾定律并確保 MOSFET 晶體管的最終縮放,因為 2D-FET 提供了固有的亞 1nm 晶體管溝道厚度。由于其良好的載流子傳輸和移動性,即使對于原子級薄層,它們也適用于高性能和低功耗平臺。此外,它們的器件主體厚度和適度的能帶隙導致增強的靜電控制,從而導致低斷態電流。

這些特性將 2D-FET 堆疊納米片器件定位為 2030 年后晶體管縮放的有前途的解決方案,這將需要高質量的 2D 通道生長、適應性轉移和穩健的工藝模塊。為此,這個多年期項目將開發一種可行的層轉移技術,將高質量二維材料(生長在 300 毫米首選基板上)轉移到另一個用于晶體管工藝集成的器件基板。英特爾為該項目帶來了數十年的研發和制造專業知識,CEA-Leti 還提供了鍵合和傳輸層專業知識以及大規模表征。

英特爾技術開發高級研究員兼英特爾歐洲研究總監 Robert Chau 表示:“隨著我們不懈地推動摩爾定律,2D TMD 材料是一種很有前途的選擇,可以在未來擴展晶體管的縮放極限。” “該研究計劃的重點是開發一種可行的基于 2D TMD 的 300mm 技術,用于未來的摩爾定律晶體管縮放。”

英特爾將其在半導體和封裝研究與技術方面的實力和專業知識與歐洲合作伙伴合作,以開發摩爾定律創新并推動歐洲的微電子技術發展。2022 年,Chau 從美國調往歐洲,領導英特爾歐洲研究院,并與歐洲大陸的合作伙伴一起推動英特爾的研發。英特爾和 CEA-Leti 在半導體設計、工藝和封裝技術方面有著長期的密切合作。

最近,他們宣布在 2022 年 6 月使用自組裝工藝實現未來芯片集成的新型芯片到晶圓鍵合技術的研究取得突破。Chau 于 6 月 16 日訪問了 CEA-Leti 的格勒諾布爾總部,以強調其重要性他們的合作和項目的啟動,一直是兩個實體之間多年研究合作的有力支持者。

CEA-Leti 首席執行官 Sebastien Dauvé 表示,行業路線圖表明,二維材料將集成到未來的微電子設備中,而 300 毫米晶圓的轉移能力將是這種集成的關鍵。

“由于其超過 700°C 的高生長溫度和在首選基板上的高質量生長,很難堆疊 2D 材料,很難像通常的薄層一樣沉積在堆疊上。因此,轉移最有希望將它們集成到未來的設備中,而 CEA-Leti 在這方面的優勢在于其在轉移開發和表征方面的專業知識和技術訣竅,”Dauvé 說。

除了二維晶體管外,CFET 晶體管也是大家關注的一個方向,imec也在其上取得了新進展。

邁向單片 CFET 晶體管

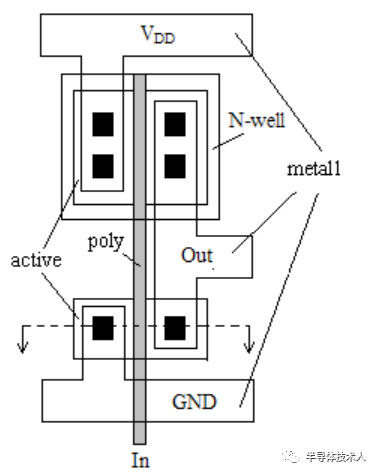

imec 主要技術成員 Hans Mertens表示:“今天,半導體行業正處于從 FinFET 到 Nanosheet 的過渡期,Nanosheet 是一種器件架構,將通過多代邏輯技術擴展路線圖。在此過程中,我們可能會介紹 Forksheet,這是imec幾年前提出的一種先進的納米片架構,它減少了相鄰器件之間的間隔,與傳統的納米片相比,提供了縮放和性能優勢。到本世紀末,imec預計 complementary FET (CFET) 將進入路線圖。在該器件架構中,n- 和 pMOS 器件相互堆疊,首次從標準單元高度考慮中消除了 np 分離。當輔以先進的技術來接觸晶體管時,CFET允許逐漸推動track高度從5T走向4T,有效地大幅縮小標準單元尺寸。

從工藝的角度來看,由于 nMOS-pMOS 垂直堆疊結構,CFET 制造具有挑戰性,我們正處于尋路的早期階段。已經提出了幾種 CFET,包括單片(monolithic )和順序(sequential )工藝流程。在順序工藝流程中,頂層器件在底層器件頂部通過晶圓鍵合轉移覆蓋半導體層后按順序進行處理。相反,單片集成涉及在單個基板上構建垂直設備架構。”

單片 CFET:引入 CFET 的最快途徑

imec 技術人員主要成員 Anne Vandooren 表示:“在我們的邏輯計劃中,imec 及其合作伙伴專注于單片 CFET 集成,因為與現有的納米片型工藝流程相比,這種集成方案的破壞性最小。因此,它被認為是在行業相關維度上引入 CFET 的最快途徑。盡管如此,制造這兩種器件的層的垂直堆疊推動了對高縱橫比圖案化、材料的選擇性沉積和去除以及高質量(epi-)膜沉積的需求。此外,還需要引入一些 CFET 專用工藝模塊,以實現橫截面的柵極和接觸部分的垂直隔離。

我們通過將單片 CFET 集成挑戰劃分為不同的子項目來應對這些挑戰,并逐漸增加集成復雜性。每個子項目都建立在不同的測試工具上。我們首先關注單極單片 CFET,n 和 p 頂部和底部器件在不同晶圓上加工。其他測試車輛將在同一晶圓上加工單片 CMOS CFET 器件。它們的主要區別在于 CFET 器件的接觸方式,最終致力于實現先進的中線 (MOL) 和背面連接選項。對于每個test vehicles,我們探索了各種工藝和集成選項,權衡功率性能區域收益與復雜性。在每輛車上獲得的知識將轉移到下一輛車上。”

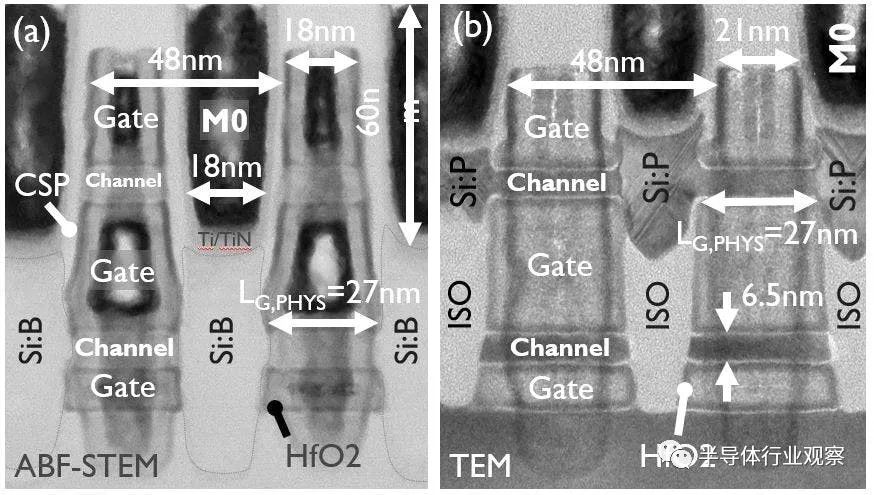

48nm 柵極間距的單極單片 CFET 演示

Hans Mertens:“在 VLSI 2020 上,imec 率先在 300mm 晶圓上展示了單片 CFET 器件,盡管采用的是 90nm 的‘relaxed’柵極間距(即接觸多晶硅間距 (CPP))。在 VLSI 2023 上,imec 展示了通過單片集成以行業相關的 48nm 柵極間距構建的單極 CFET 器件。該作品入選 2023 VLSI 技術研討會亮點環節。我們的功能器件分別為 n- 和 pMOS 的底部和頂部器件顯示出出色的開關特性。我們目前正在探索以更小的柵極間距進行單極單片 CFET 集成。

(a)底部 pFET 和 (b) 頂部 nFET (LG,PHYS=27nm)(在 VLSI 2023 上展示)的工藝結束橫截面圖像。

在此演示中,評估了底部或頂部器件的源極-漏極外延結構(源極-漏極外延)和源極-漏極接觸。此外,為了限制縱橫比并加快開發速度,結構的活性部分僅限于底部的一個納米片和頂部器件的一個。然而,這項工作的意義在于表明,在頂層和底層之間的垂直間距僅為 30 納米的情況下,我們找到了一種獨立接觸頂層和底層設備的方法。它是在縮放維度上進行高級 CFET 集成的墊腳石。”

單片 CMOS CFET:具有挑戰性的工藝步驟和模塊

imec 科學總監 Steven Demuynck:“此外,我們繼續努力實現單片 CMOS CFET 器件演示,這是 imec 的一個戰略項目,通過與我們的合作伙伴的密切合作實現。與單極 CFET 器件不同,堆疊式 p 底部和 n 頂部器件現在將在同一晶圓上實現并獨立接觸。此外,集成流程應允許區分共享公共柵極的兩個器件上的閾值電壓 (Vt) 設置——所有器件均采用行業相關的 50nm 柵極間距。這種垂直架構具有重大意義。它不僅需要開發三個新的、特定于 CFET 的工藝模塊,還需要調整工藝流程中的其他模塊以適應這些特定于 CFET 的模塊的存在。

第一個特定于 CFET 的工藝模塊,我們稱為中間電介質隔離 (MDI:middle dielectric isolation),源于在頂部和底部柵極之間創建垂直電介質隔離以區分頂部和底部器件之間的 Vt 設置的需要。為實現這一點,我們的團隊提出了一個從一開始就影響工藝流程的獨特解決方案:為創建 CFET 的有源部分而形成的 Si/SiGe 疊層轉變為更高的 Si/SiGe1/SiGe2 多層疊層,具有更高的SiGe2 的 Ge% 高于 SiGe1。當犧牲 SiGe1 層被設置 Vt 的功函數金屬取代時,富含 Ge 的犧牲層被轉化為 MDI 電介質,在柵極內形成 np WF 金屬分離。該堆棧允許在堆棧中的 Ge 缺陷層上形成內部間隔物——這是一個關鍵的納米片特定特征,可將柵極與源極-漏極隔離。尋找最有效的方法來共同集成底部源漏、新的 MDI 模塊和內部墊片,在這種緊密間距和高縱橫比幾何形狀下,是我們目前研發工作的重點。

頂部和底部器件的源極-漏極接觸金屬之間需要第二個垂直隔離。探索了各種選項來構建和隔離底部和頂部觸點——在兩個高柵極之間的深處——并隨后路由底部和頂部晶體管。在 VLSI 2023 上共享了一個形態學概念驗證流程,展示了制造堆疊式 MOL 的能力。

最后,在底部器件上生長源漏外延時,我們需要封裝頂部通道。這將有效地在底部和頂部器件上實現不同摻雜的外延生長。”

從背面連接 CFET 器件

Anne Vandooren:“從長遠來看,我們正在探索先進的集成選項,以從背面連接有源設備。這些發展是由進一步降低標準單元高度和避免晶圓正面后端生產線中的布線擁塞的需求推動的。

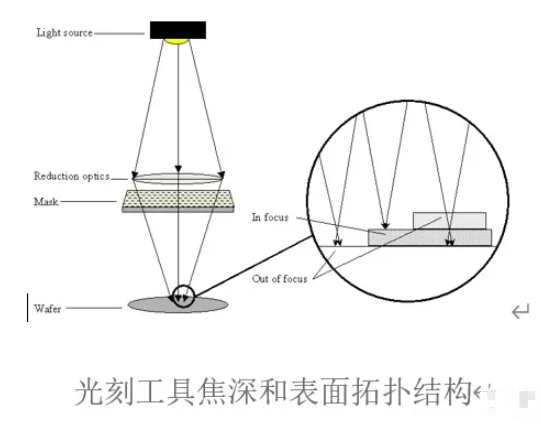

背面接觸引入了額外的工藝步驟,包括晶圓鍵合和從背面減薄基板。這些步驟挑戰了非常緊密的覆蓋層,以將背面層與正面已經存在的小特征對齊。這更具挑戰性,因為在鍵合過程中會發生晶圓變形,需要使用特定的光刻覆蓋校正方法。此外,還需要一個額外的工藝模塊來在背面金屬 1 和 CFET 器件的活性納米片部分之間提供適當的隔離。”

CFET 支持:行業協作努力

Steven Demuynck:“自從我們開始 CFET 開發以來,我們發現與設備供應商的合作強度有所增加。一方面,這些供應商希望參與到開發的早期階段,以便能夠確定他們的工具、流程和材料在該路線圖中的位置。他們還想了解這些需要運行的環境,以了解流程中上游和下游的交互。Imec 在為這些公司提供具有 CFET 相關拓撲和幾何形狀的晶圓方面發揮著關鍵作用。在 IDM 開始開發之前,他們通常不容易獲得此類材料。另一方面,這些合作也為 imec 帶來了好處。與我們的工具供應商的合作有助于我們利用合作伙伴的最先進功能。

與此同時,我們的邏輯核心合作伙伴有興趣通過評估各種流程風格來確定我們遇到的關鍵挑戰和潛在障礙。在早期階段了解硬件和流程支持什么,可以讓他們在開始自己的研發工作時搶先一步。”

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論