?

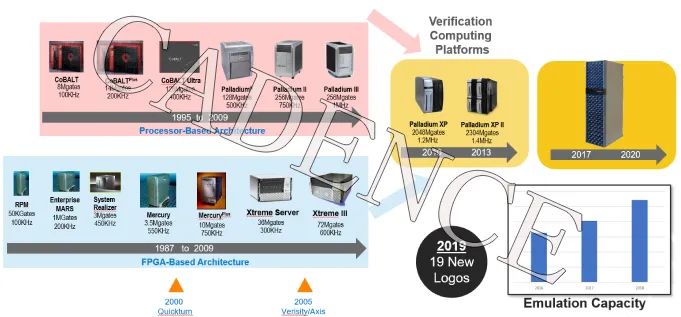

硬件仿真器(Emulator)從誕生至今,已經(jīng)有接近40年的歷史,經(jīng)歷了一個(gè)不斷成熟的過程,它隨著集成電路產(chǎn)業(yè)的發(fā)展仍在不斷演進(jìn)。

想了解Emulation的發(fā)展和技術(shù)演進(jìn)的,可以觀看Dr. T.C. Lin作為硬件仿真器發(fā)展的親歷者的精彩分享。

Emulation: From History to Technology Evolution

20世紀(jì)80年代后期,FPGA芯片剛剛誕生,立刻被用于電路邏輯的仿真。因?yàn)?strong>FPGA本質(zhì)就是使用可編程的通用電路單元去仿真各種電路,非常適合電路邏輯的仿真驗(yàn)證。

那之后,用多顆FPGA芯片構(gòu)建專用的硬件仿真器產(chǎn)品逐漸掀起熱潮,這需要解決一系列的問題:大規(guī)模FPGA陣列的硬件設(shè)計(jì)、目標(biāo)電路邏輯的分割、多FPGA之間的數(shù)據(jù)交換、如何實(shí)現(xiàn)分割之后的統(tǒng)一調(diào)試等等。

硬件仿真器以其容量、性能、可調(diào)試性方面的獨(dú)特優(yōu)勢(shì),從誕生以來不斷發(fā)展,已經(jīng)是仿真驗(yàn)證中的基礎(chǔ)性EDA工具,也引領(lǐng)著芯片驗(yàn)證技術(shù)的不斷革新。

本文將從發(fā)展的眼光來探討“當(dāng)代Emulator”應(yīng)該滿足哪些條件。

Emulator v.s. Prototyping

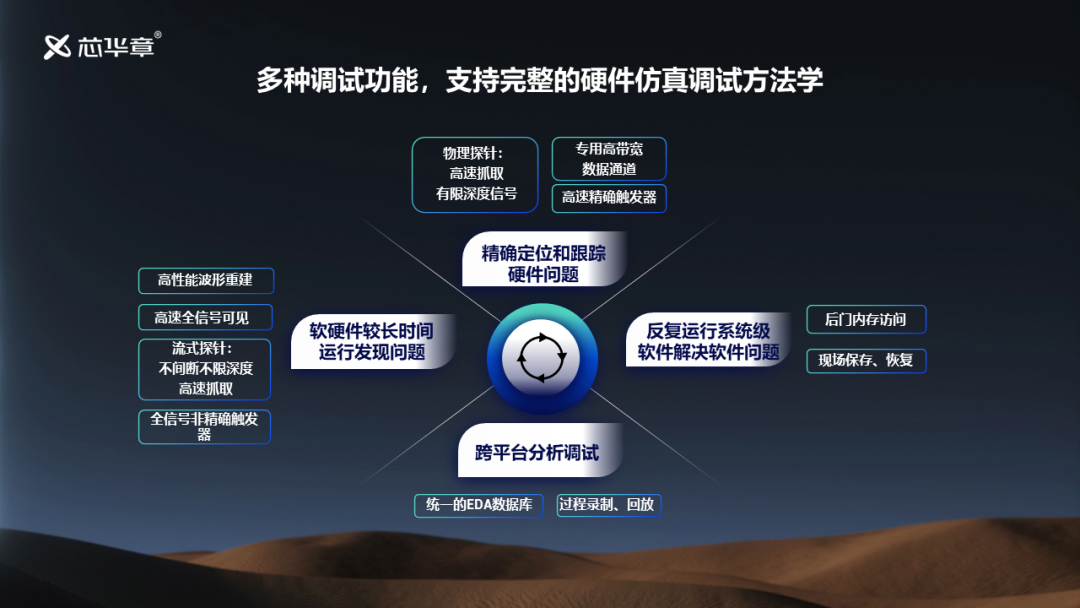

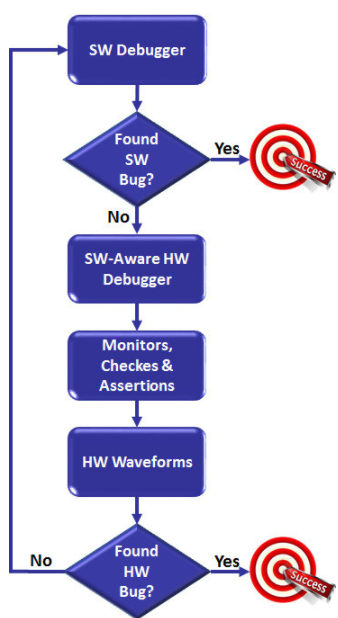

Emulator具備更深度和靈活的調(diào)試能力

總體上看,硬件仿真器能夠支持超大規(guī)模(百億門級(jí))的設(shè)計(jì)容量,全自動(dòng)化的軟件設(shè)置實(shí)現(xiàn)流程,基本無需修改硬件連接配置,以及靈活多樣的全系統(tǒng)仿真調(diào)試能力,Emulator的優(yōu)勢(shì)包括:

依托自研綜合工具的信號(hào)綜合后全保留,以及完整、長時(shí)間的信號(hào)追蹤(達(dá)數(shù)百億周期)

信號(hào)的高級(jí)觸發(fā)模式態(tài)探針插入/離線虛擬調(diào)試

擁有不限量的時(shí)鐘域,它們可以從核心時(shí)鐘資源中無限衍生

全系統(tǒng)范圍可見的Debug調(diào)試追蹤

System Verilog/UVM Simulation/C++/Python等測(cè)試加速支持

軟硬件的協(xié)同驗(yàn)證、測(cè)試接口的虛擬化支持

系統(tǒng)功耗預(yù)估/分析等

現(xiàn)代硬件仿真系統(tǒng)容量

進(jìn)入 “百億門規(guī)模”的級(jí)別

考慮到硬件仿真自身會(huì)占用大量的Debug(調(diào)試) 邏輯,這里的“大容量”,是指產(chǎn)品扣除了上述的調(diào)試邏輯后,能夠供用戶實(shí)際使用的最大設(shè)計(jì)容量。那么,這個(gè)指標(biāo)必須匹配當(dāng)前主流SoC和多片封裝的Chiplet芯片設(shè)計(jì)規(guī)模。什么是主流芯片規(guī)模? ?

蘋果M1Pro處理器的規(guī)模約100億門

按一般的4晶體管等效門來大致計(jì)算,GPU巨頭英偉達(dá)公司目前主流GPU芯片規(guī)模為100多億門(420億晶體管),蘋果M1 Pro處理器的規(guī)模約100億門(400億左右晶體管,單封裝),國內(nèi)某廠商的AI芯片是超過90億門(370億晶體管),即使是比較小的某廠商交換芯片,也接近50億門規(guī)模(近200億晶體管),而其它的大型CPU、GPU、DPU等主流系統(tǒng)級(jí)芯片也都在百億門左右甚至更高的規(guī)模。 ?

從這些數(shù)據(jù)來定義Emulator,我們可以提出一個(gè)很具體的百億門容量指標(biāo)。 ? 不

能通過全自動(dòng)設(shè)計(jì)工具支持百億門以上設(shè)計(jì)實(shí)現(xiàn)仿真的產(chǎn)品,只能說有一定的硬件仿真(Emulation)特性,但由于其無法容納并驗(yàn)證一個(gè)全芯片規(guī)模的邏輯功能,所以很難被認(rèn)定為完整的Emulator,即硬件仿真器產(chǎn)品。 ? 從國外EDA公司的主流產(chǎn)品來看,目前也都達(dá)到了百億門到三百億門級(jí)別的容量指標(biāo),同時(shí)對(duì)大容量設(shè)計(jì)依然保持?jǐn)?shù)百KHz以上甚至上MHz的性能。 ?

硬件仿真器豐富的使用模式

ICE模式

ICE模式的吸引力在于能將現(xiàn)實(shí)測(cè)試中的激勵(lì),以可綜合的方式注入到硬件中高速運(yùn)行的DUT(待測(cè)設(shè)備)中,以此驗(yàn)證設(shè)計(jì)在硬件中的真實(shí)功能和性能

在Emulator初生的年代,ICE模式是最主要的使用模式,一直到今天也是主流使用場(chǎng)景之一

此外,典型的測(cè)試?yán)邮切枰谕獠肯到y(tǒng)和硬件仿真器之間插入速度適配器(Speed Adapter),這樣做是為了適應(yīng)前者的快速時(shí)鐘速率

TBA加速仿真模式

軟件的功能也大大加強(qiáng)。除了傳統(tǒng)的ICE模式外,基于Transaction(事務(wù)級(jí))、以收發(fā)包為傳輸單位的TBA加速仿真模式及Hybrid Mode的仿真模式(即在Server主機(jī)當(dāng)中安裝各類虛擬OS,DUT運(yùn)行在Emulator中,兩者通過特定的協(xié)議聯(lián)通)

雖然說這兩者的運(yùn)行速度不及ICE模式高,但由于其無需復(fù)雜連線,與傳統(tǒng)軟件仿真兼容的方案,以及十分豐富的調(diào)試手段,受到了驗(yàn)證工程師的廣泛歡迎

Hybrid混合仿真模式

隨著Emulator要仿真的系統(tǒng)越來越復(fù)雜,將軟件模型與Emulator中的DUT邏輯混合使用,去仿真更大的系統(tǒng)也成為了一個(gè)常用應(yīng)用場(chǎng)景

在主機(jī)上運(yùn)行虛擬CPU模型,或者是虛擬化的完整x86主機(jī),而把外設(shè)芯片電路放在Emulator中仿真,兩者之間通過Transactor協(xié)議模型互聯(lián),就是一種典型的混合仿真

相反,把CPU模型運(yùn)行在Emulator中,而用軟件去仿真豐富多樣的存儲(chǔ)或外設(shè)接口模型(HBM,DDR5/4,LPDDR/PCIe/MIPI PHY等),也大大增強(qiáng)了工程師的系統(tǒng)級(jí)驗(yàn)證手段

此外,對(duì)斷言(Assertion)和覆蓋率(Coverage)的支持、基于DPI-C的TLM擴(kuò)展接口及對(duì)運(yùn)行現(xiàn)場(chǎng)保存和恢復(fù)的支持等,這些高級(jí)功能的加入也給高速仿真驗(yàn)證工作提供了完整的解決方案。

不斷發(fā)展的硬件仿真器

硬件仿真器是一個(gè)軟件工具鏈和硬件平臺(tái)互相配合、設(shè)計(jì)難度極高的復(fù)雜系統(tǒng)。因此,目前市場(chǎng)上能夠提供真正意義上硬件仿真器及完整配套方案的公司也是鳳毛麟角,過去主要是來自美國的EDA三大巨頭:

Cadence的Palladium系列,以特制ASIC 處理器組成龐大系統(tǒng)

Synopsys基于商業(yè)FPGA的ZeBU產(chǎn)品線

西門子EDA(原Mentor)基于自研FPGA芯片的硬件仿真器Veloce

而國產(chǎn)EDA廠商也在追趕、創(chuàng)新、超越,比如芯華章最新發(fā)布的國內(nèi)首套百億級(jí)HuaEmuE1硬件仿真器,不僅僅實(shí)現(xiàn)了傳統(tǒng)仿真器在容量、調(diào)試、性能方面的各項(xiàng)能力,還創(chuàng)新發(fā)展了多項(xiàng)特色功能:

E1為了解決多級(jí)FPGA傳輸數(shù)據(jù)引起的延遲過大問題,采用了自研格式的高速光交換協(xié)議,和傳統(tǒng)通用的Aurora協(xié)議相比,延遲降低50%;同時(shí)在物理的部署上采用全光纜互聯(lián),更輕便靈活;較銅制線纜的應(yīng)力影響更小

系統(tǒng)最高支持128個(gè)用戶同時(shí)使用,并采用了“隔離通道”的技術(shù),來保證多用戶情況下數(shù)據(jù)的獨(dú)立性,防止互相干擾;并且支持基于云的使用模式

E1支持豐富的驗(yàn)證場(chǎng)景,如虛擬主機(jī)混仿、虛擬設(shè)備混仿、ICE在線仿真、系統(tǒng)性能分析、軟仿測(cè)試加速、系統(tǒng)級(jí)調(diào)試等

E1還支持非常豐富的解決方案:從協(xié)議上,涵蓋AXI/PCIe/MIPI/DDR5/DDR4/HBM2E Transactor等各種類型的應(yīng)用

以下我們結(jié)合具體的應(yīng)用場(chǎng)景,來簡單說明芯華章硬件仿真系統(tǒng)為用戶提供的豐富解決方案。

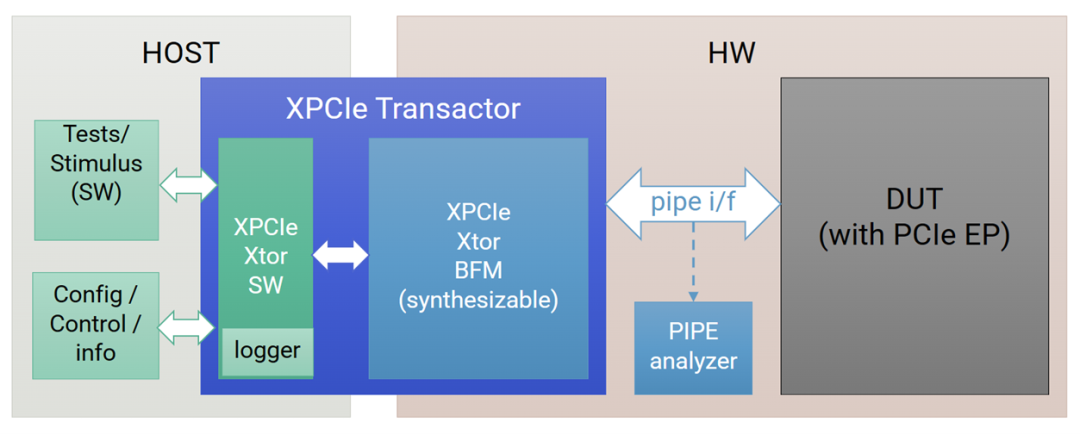

芯華章科技PCIe方案

?? 在Host主機(jī)側(cè)進(jìn)行配置和控制的動(dòng)作,運(yùn)行一個(gè)包含PCIe協(xié)議相關(guān)測(cè)試用例的軟件仿真器(Simulator),那么再在E1硬件上運(yùn)行一個(gè)模擬PCIe Root Complex的可綜合模型(內(nèi)部包含了PCIe RC的IP);

?? 通過PIPE接口連接到用戶設(shè)計(jì)的待驗(yàn)證功能模塊。這樣的好處是避免了繁瑣的硬件線路連接,從而使得驗(yàn)證過程更穩(wěn)定可靠。

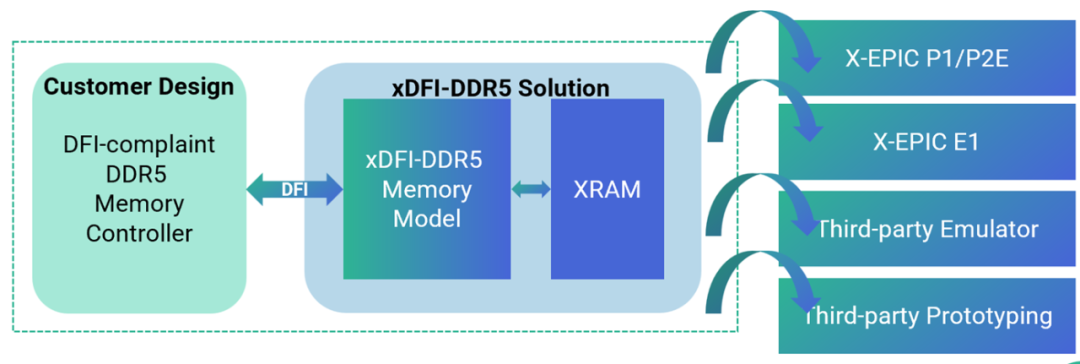

芯華章科技DDR5模型

?? 芯華章自研的XRAM模塊提供前后門讀寫等工作模式,可以方便用戶的調(diào)試,通過連接DDR5的內(nèi)存模型并提供到接口給用戶,然后用戶只需方便地把自己的設(shè)計(jì)接到內(nèi)存接口上就可以實(shí)現(xiàn)模塊的調(diào)用實(shí)現(xiàn)。

由此看來:在這些創(chuàng)新技術(shù)的驅(qū)動(dòng)下,硬件仿真系統(tǒng),特別是國產(chǎn)EDA廠商的百億門級(jí)以上的硬件仿真產(chǎn)品,在實(shí)現(xiàn)智能設(shè)計(jì)流程、減少用戶人工投入、縮短芯片驗(yàn)證周期方面,起到了極大的作用,一定會(huì)繼續(xù)作為關(guān)鍵性EDA工具推動(dòng)芯片設(shè)計(jì)驗(yàn)證方法的發(fā)展。

?

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論