華金證券,孫遠峰、王海維、王臣復

先進封裝:打破IC發(fā)展限制,向高密度封裝時代邁進

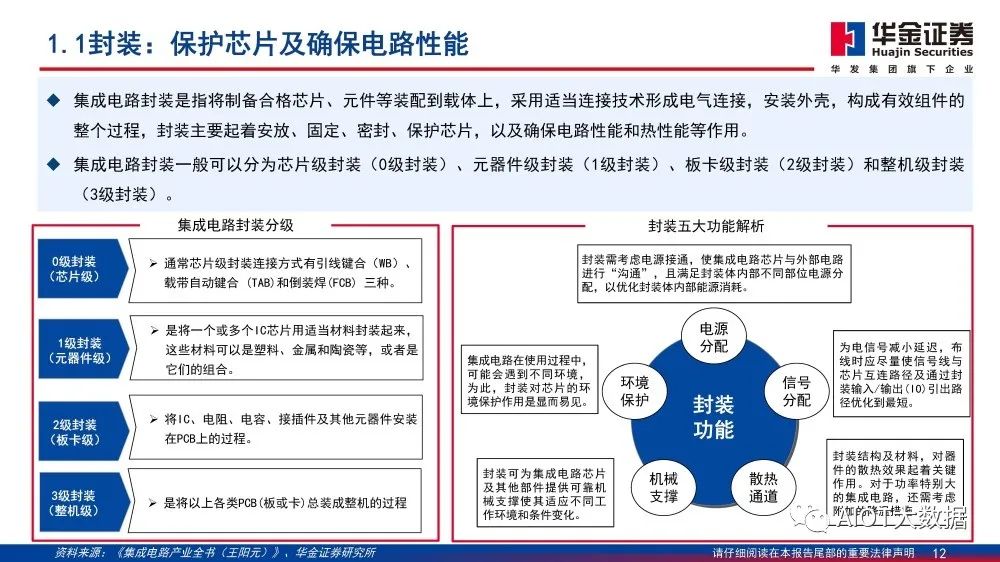

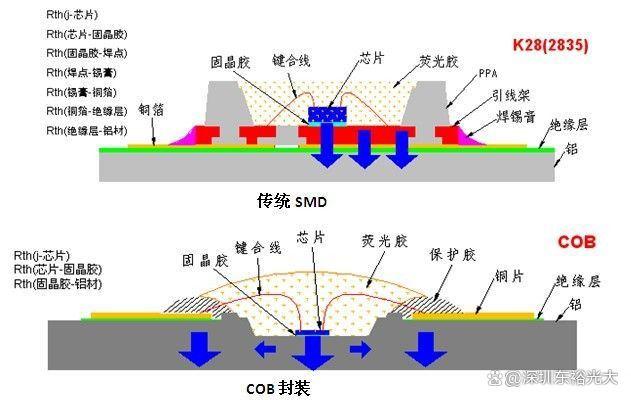

封裝:保護芯片及確保電路性能

集成電路封裝是指將制備合格芯片、元件等裝配到載體上,采用適當連接技術形成電氣連接,安裝外殼,構成有效組件的整個過程,封裝主要起著安放、固定、密封、保護芯片,以及確保電路性能和熱性能等作用。 集成電路封裝一般可以分為芯片級封裝(0級封裝)、元器件級封裝(1級封裝)、板卡級封裝(2級封裝)和整機級封裝(3級封裝)。

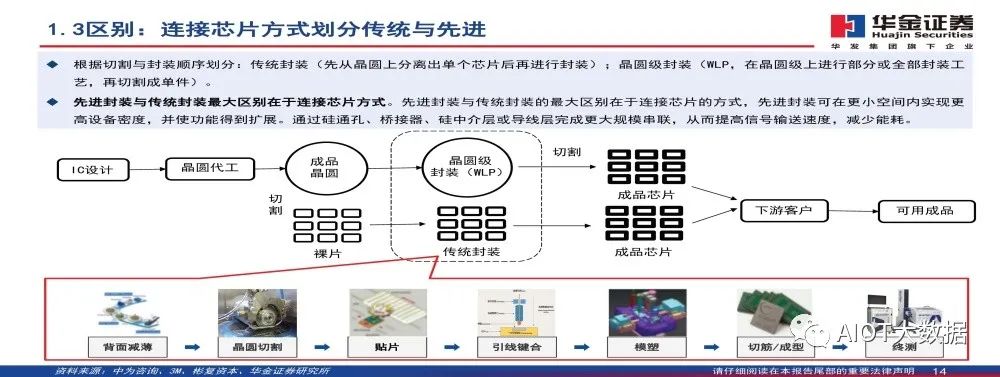

區(qū)別:連接芯片方式劃分傳統(tǒng)與先進

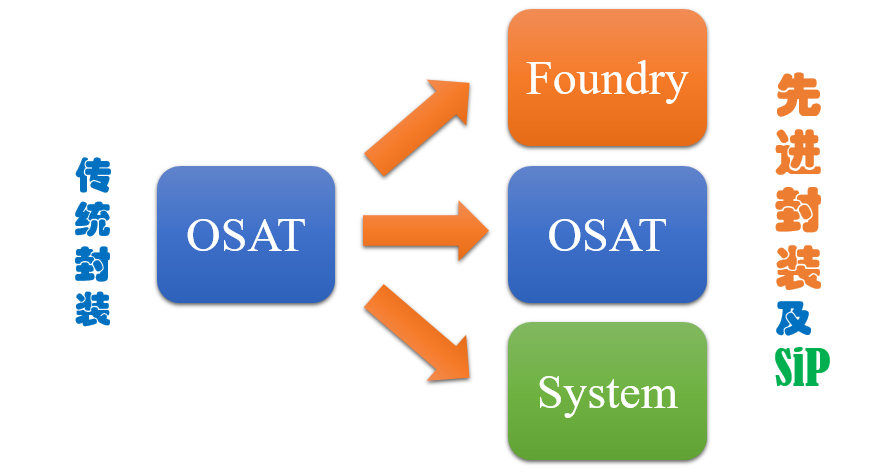

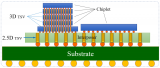

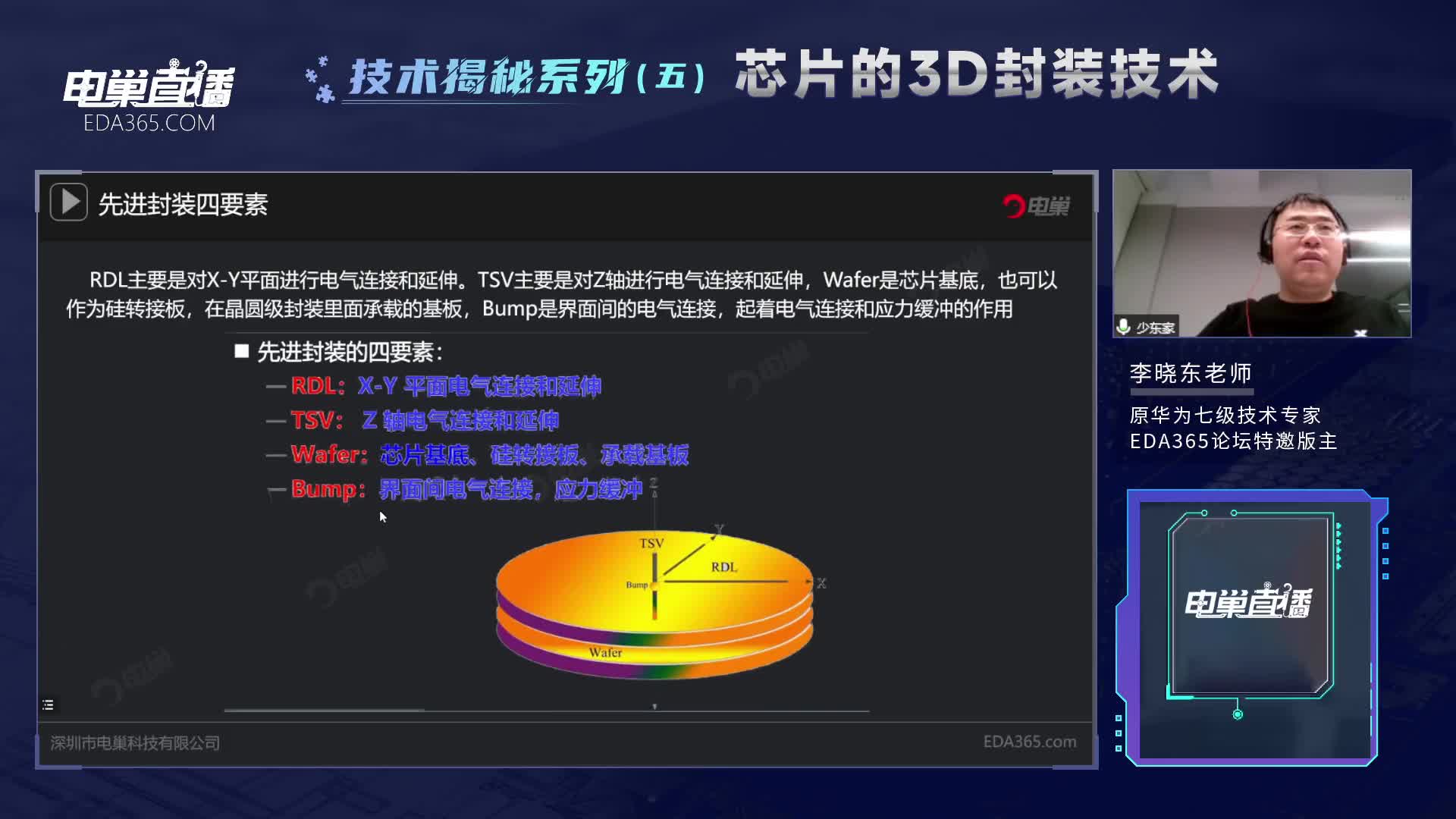

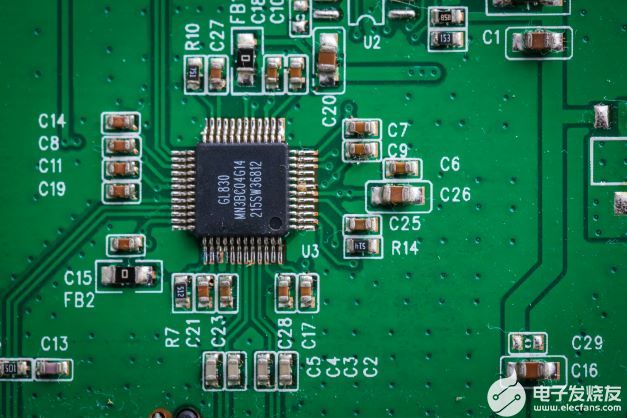

根據(jù)切割與封裝順序劃分:傳統(tǒng)封裝(先從晶圓上分離出單個芯片后再進行封裝);晶圓級封裝(WLP,在晶圓級上進行部分或全部封裝工藝,再切割成單件)。 先進封裝與傳統(tǒng)封裝最大區(qū)別在于連接芯片方式。先進封裝與傳統(tǒng)封裝的最大區(qū)別在于連接芯片的方式,先進封裝可在更小空間內(nèi)實現(xiàn)更高設備密度,并使功能得到擴展。通過硅通孔、橋接器、硅中介層或導線層完成更大規(guī)模串聯(lián),從而提高信號輸送速度,減少能耗。

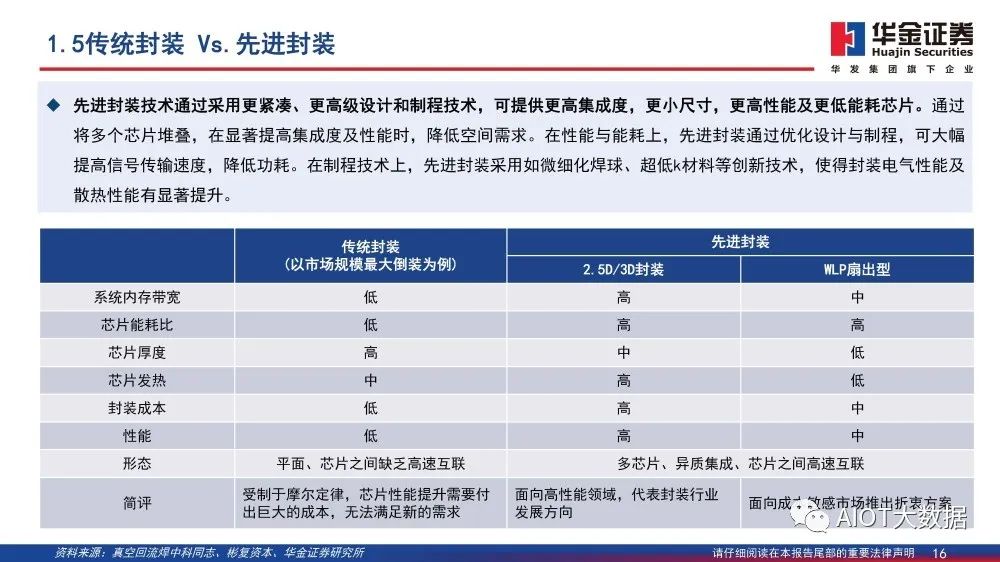

傳統(tǒng)封裝 Vs.先進封裝

先進封裝技術通過采用更緊湊、更高級設計和制程技術,可提供更高集成度,更小尺寸,更高性能及更低能耗芯片。通過將多個芯片堆疊,在顯著提高集成度及性能時,降低空間需求。在性能與能耗上,先進封裝通過優(yōu)化設計與制程,可大幅提高信號傳輸速度,降低功耗。在制程技術上,先進封裝采用如微細化焊球、超低k材料等創(chuàng)新技術,使得封裝電氣性能及散熱性能有顯著提升。

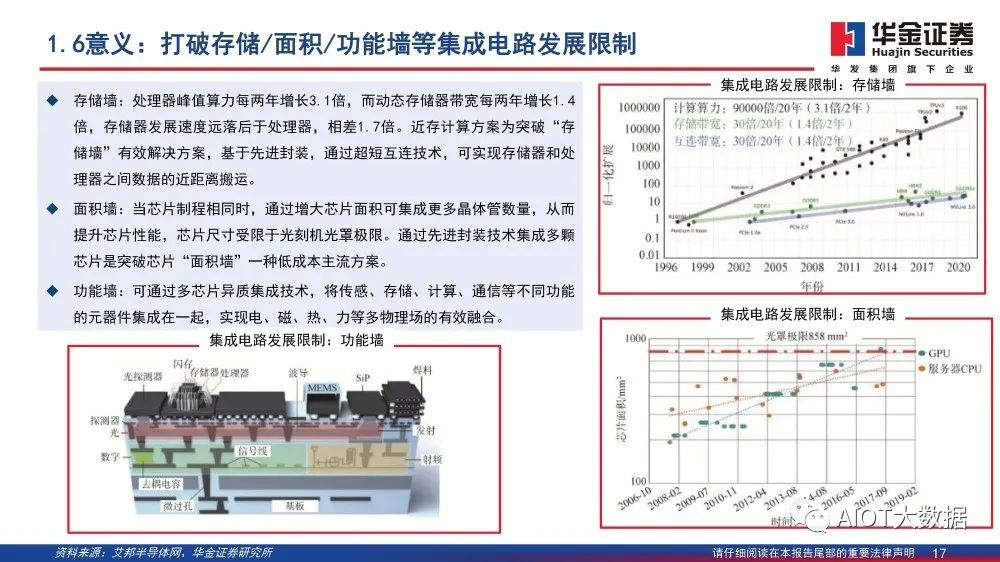

意義:打破存儲/面積/功能墻等集成電路發(fā)展限制

存儲墻:處理器峰值算力每兩年增長3.1倍,而動態(tài)存儲器帶寬每兩年增長1.4 倍,存儲器發(fā)展速度遠落后于處理器,相差1.7倍。近存計算方案為突破“存 儲墻”有效解決方案,基于先進封裝,通過超短互連技術,可實現(xiàn)存儲器和處 理器之間數(shù)據(jù)的近距離搬運。 面積墻:當芯片制程相同時,通過增大芯片面積可集成更多晶體管數(shù)量,從而 提升芯片性能,芯片尺寸受限于***光罩極限。通過先進封裝技術集成多顆 芯片是突破芯片“面積墻”一種低成本主流方案。 功能墻:可通過多芯片異質集成技術,將傳感、存儲、計算、通信等不同功能 的元器件集成在一起,實現(xiàn)電、磁、熱、力等多物理場的有效融合。

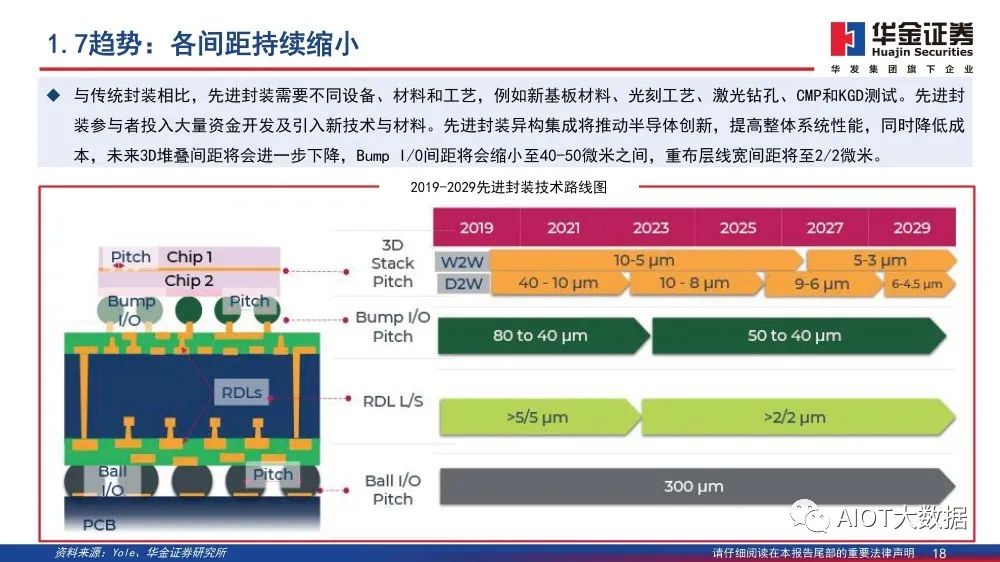

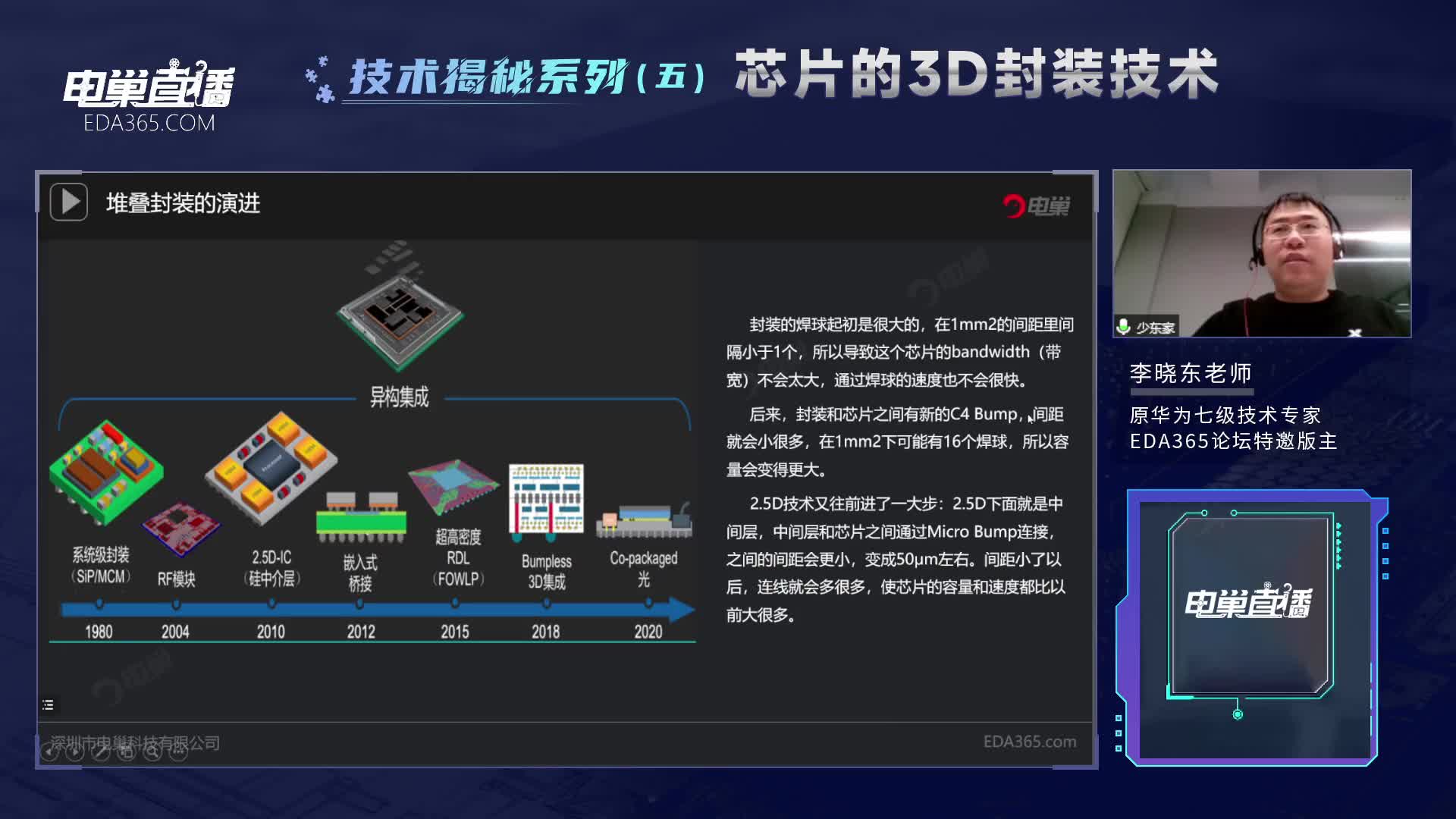

趨勢:各間距持續(xù)縮小

與傳統(tǒng)封裝相比,先進封裝需要不同設備、材料和工藝,例如新基板材料、光刻工藝、激光鉆孔、CMP和KGD測試。先進封裝參與者投入大量資金開發(fā)及引入新技術與材料。先進封裝異構集成將推動半導體創(chuàng)新,提高整體系統(tǒng)性能,同時降低成本,未來3D堆疊間距將會進一步下降,Bump I/0間距將會縮小至40-50微米之間,重布層線寬間距將至2/2微米。

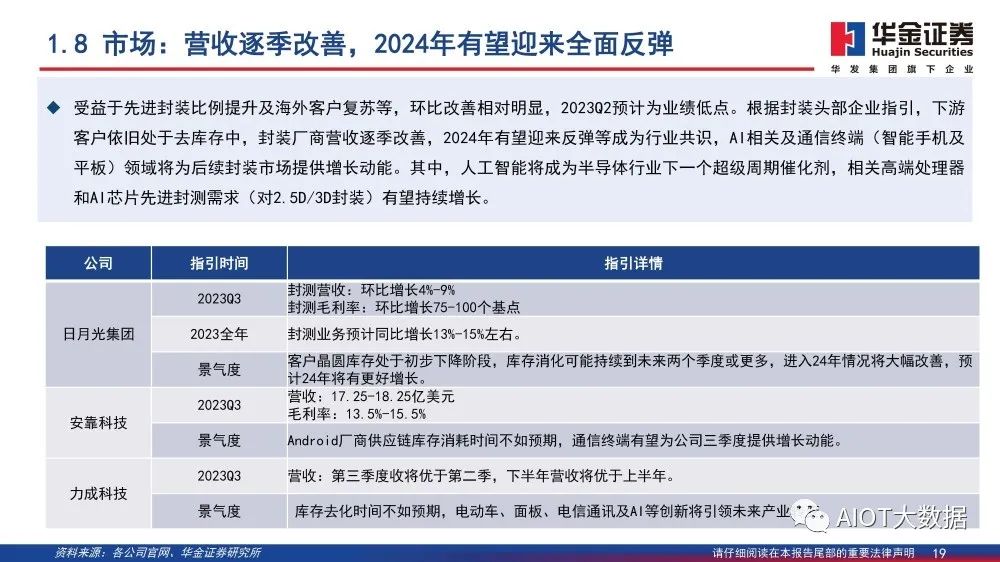

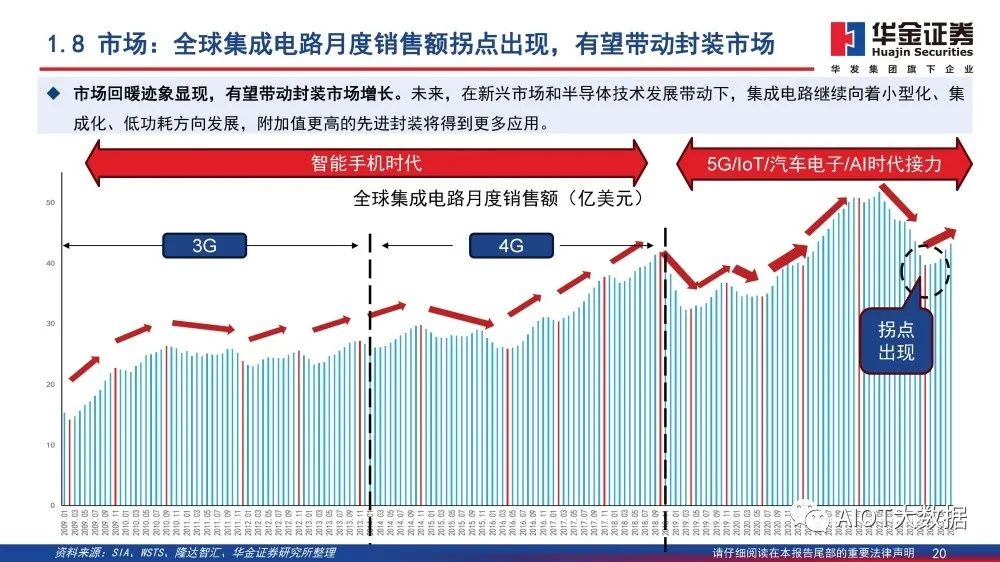

市場:營收逐季改善,2024年有望迎來全面反彈

受益于先進封裝比例提升及海外客戶復蘇等,環(huán)比改善相對明顯,2023Q2預計為業(yè)績低點。根據(jù)封裝頭部企業(yè)指引,下游客戶依舊處于去庫存中,封裝廠商營收逐季改善,2024年有望迎來反彈等成為行業(yè)共識,AI相關及通信終端(智能手機及平板)領域將為后續(xù)封裝市場提供增長動能。其中,人工智能將成為半導體行業(yè)下一個超級周期催化劑,相關高端處理器和AI芯片先進封測需求(對2.5D/3D封裝)有望持續(xù)增長。

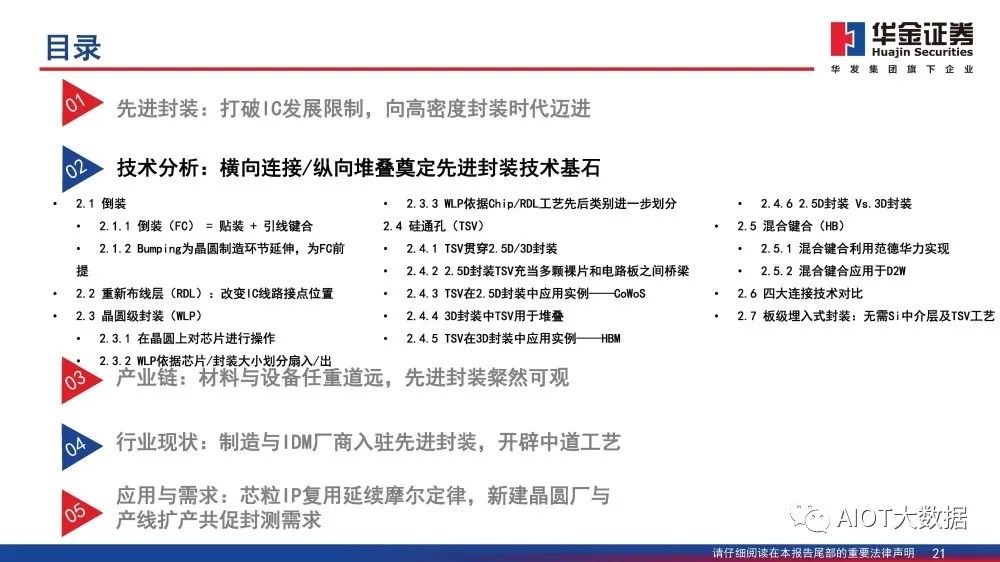

技術分析:橫向連接/縱向堆疊奠定先進封裝技術基石

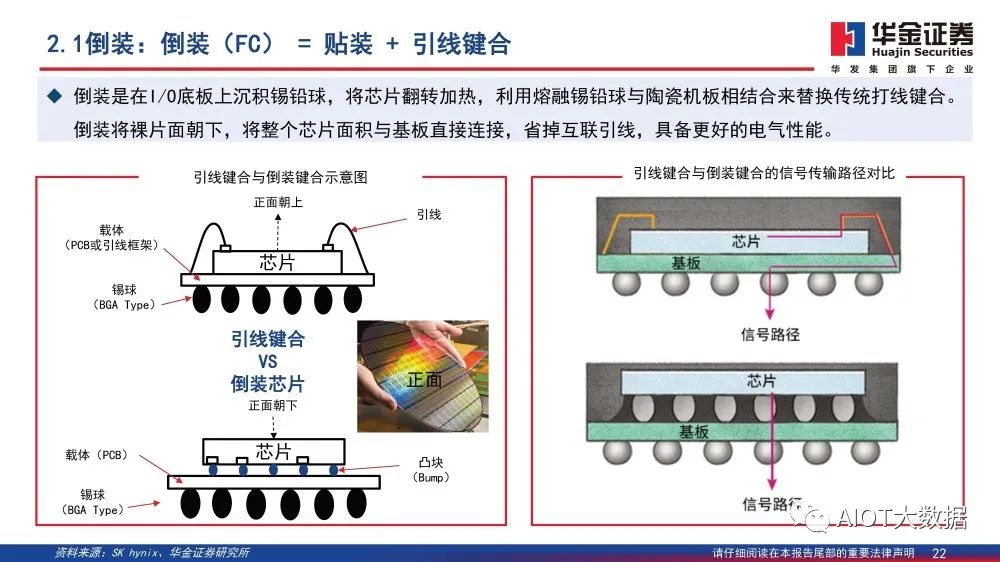

倒裝:倒裝(FC) = 貼裝 + 引線鍵合

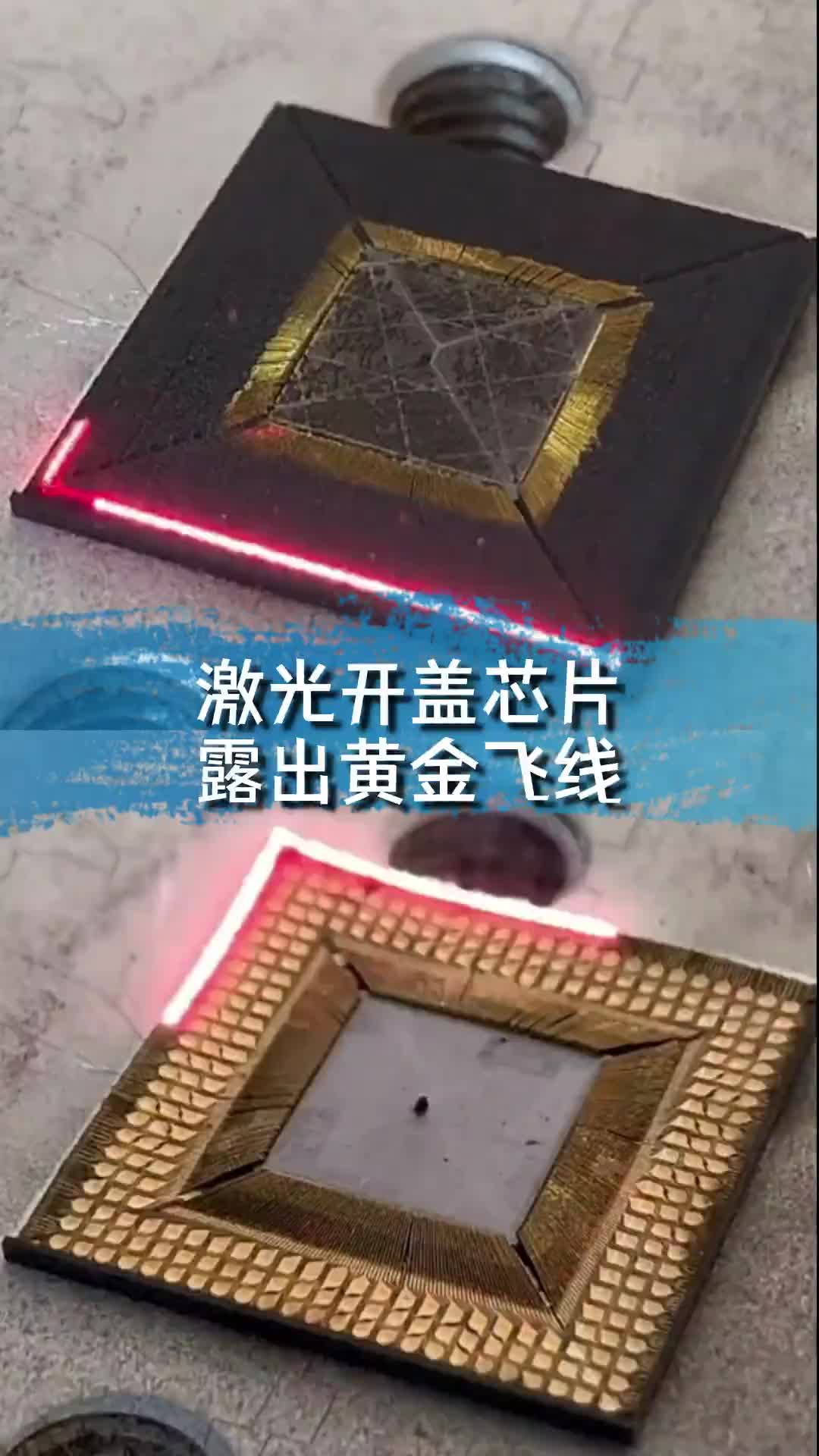

倒裝是在I/O底板上沉積錫鉛球,將芯片翻轉加熱,利用熔融錫鉛球與陶瓷機板相結合來替換傳統(tǒng)打線鍵合。倒裝將裸片面朝下,將整個芯片面積與基板直接連接,省掉互聯(lián)引線,具備更好的電氣性能。

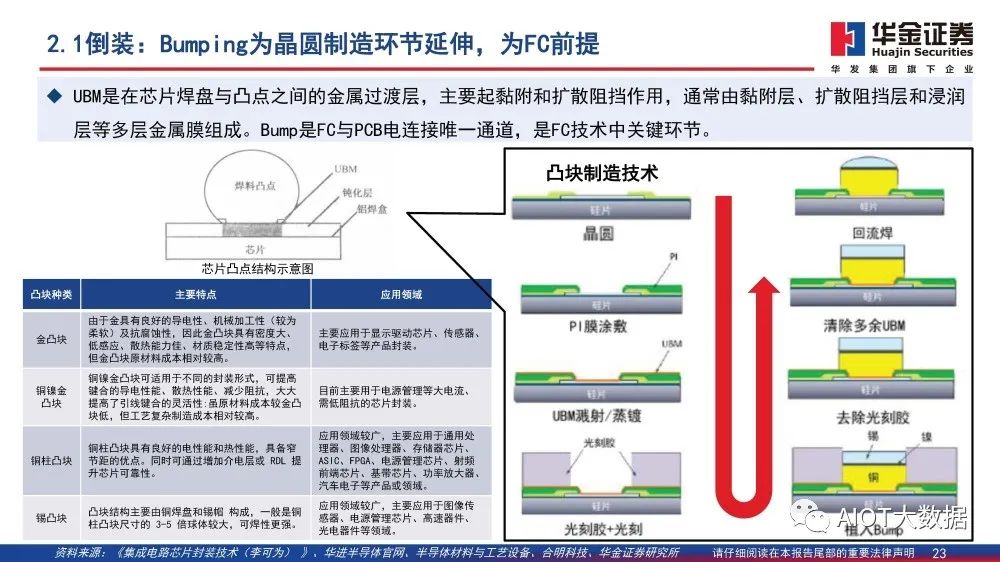

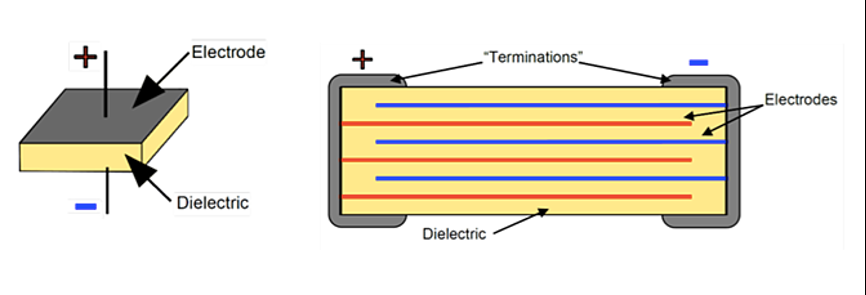

UBM是在芯片焊盤與凸點之間的金屬過渡層,主要起黏附和擴散阻擋作用,通常由黏附層、擴散阻擋層和浸潤層等多層金屬膜組成。Bump是FC與PCB電連接唯一通道,是FC技術中關鍵環(huán)節(jié)。

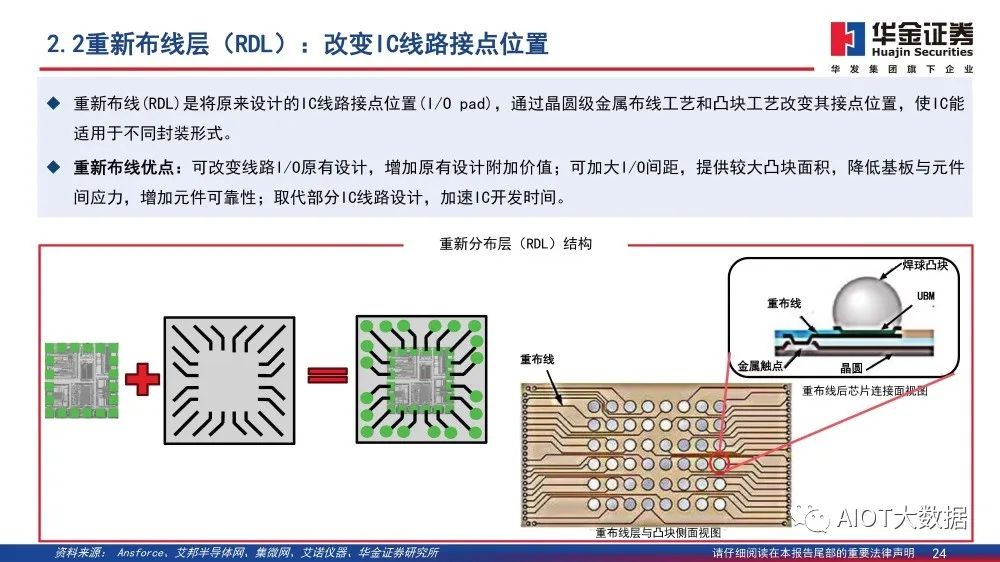

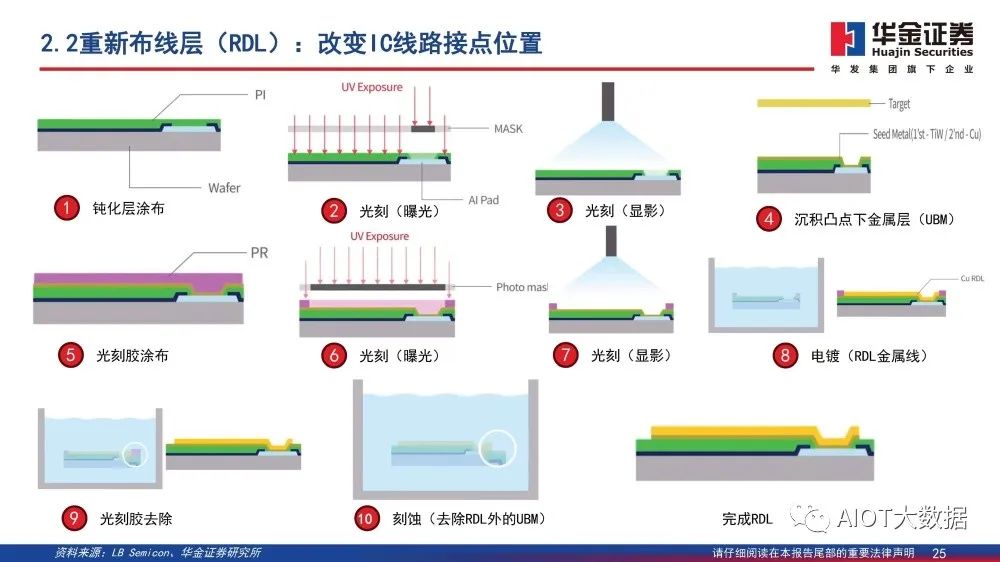

重新布線層(RDL):改變IC線路接點位置

重新布線(RDL)是將原來設計的IC線路接點位置(I/O pad),通過晶圓級金屬布線工藝和凸塊工藝改變其接點位置,使IC能適用于不同封裝形式。 重新布線優(yōu)點:可改變線路I/O原有設計,增加原有設計附加價值;可加大I/O間距,提供較大凸塊面積,降低基板與元件間應力,增加元件可靠性;取代部分IC線路設計,加速IC開發(fā)時間。

晶圓級封裝(WLP):在晶圓上對芯片進行操作

晶圓級封裝是指先在整片晶圓上同時對眾多芯片進行封裝、測試,最后切割成單個器件,并直接貼裝到基板或PCB上,生產(chǎn)成本大幅降低。 由于沒有引線、鍵合和塑膠工藝,封裝無需向芯片外擴展,使得WLP的封裝尺寸幾乎等于芯片尺寸。

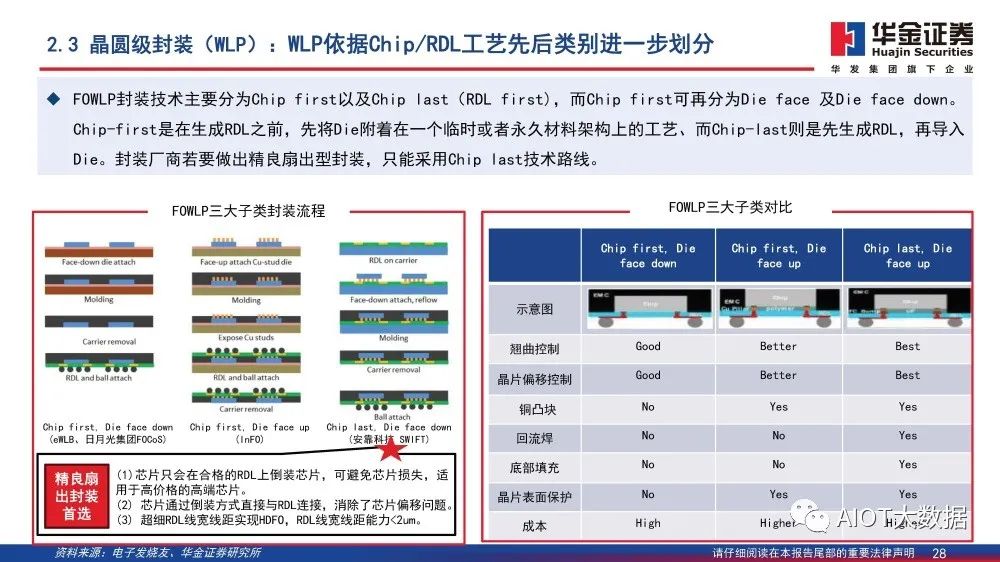

晶圓級封裝(WLP):WLP依據(jù)Chip/RDL工藝先后類別進一步劃分

FOWLP封裝技術主要分為Chip first以及Chip last(RDL first),而Chip first可再分為Die face 及Diefacedown。Chip-first是在生成RDL之前,先將Die附著在一個臨時或者永久材料架構上的工藝、而Chip-last則是先生成RDL,再導入Die。封裝廠商若要做出精良扇出型封裝,只能采用Chip last技術路線。

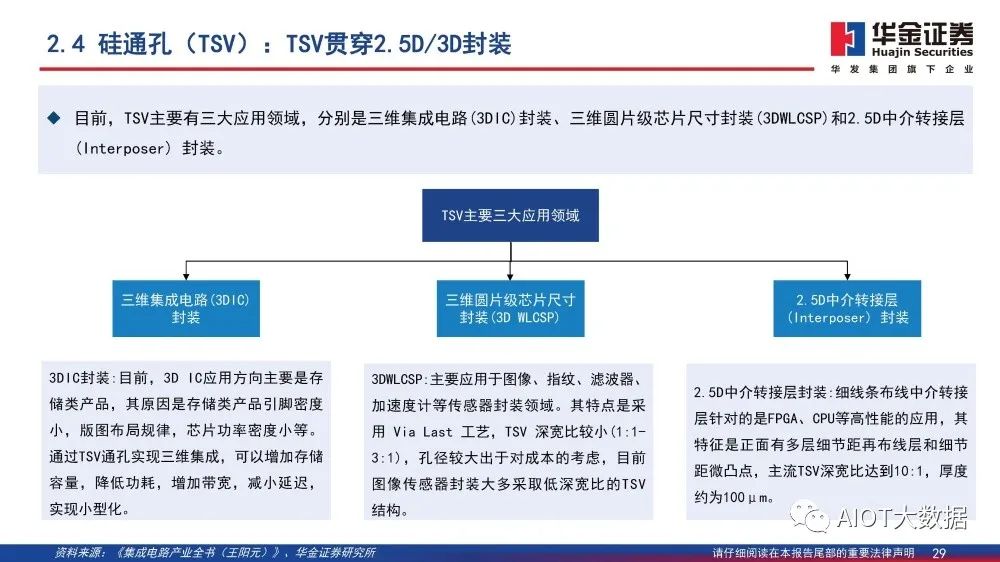

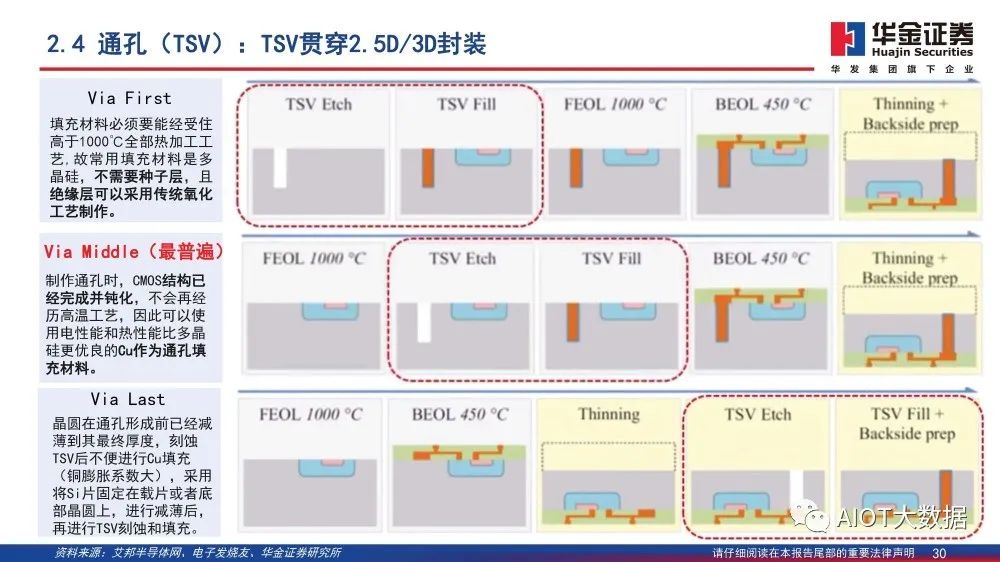

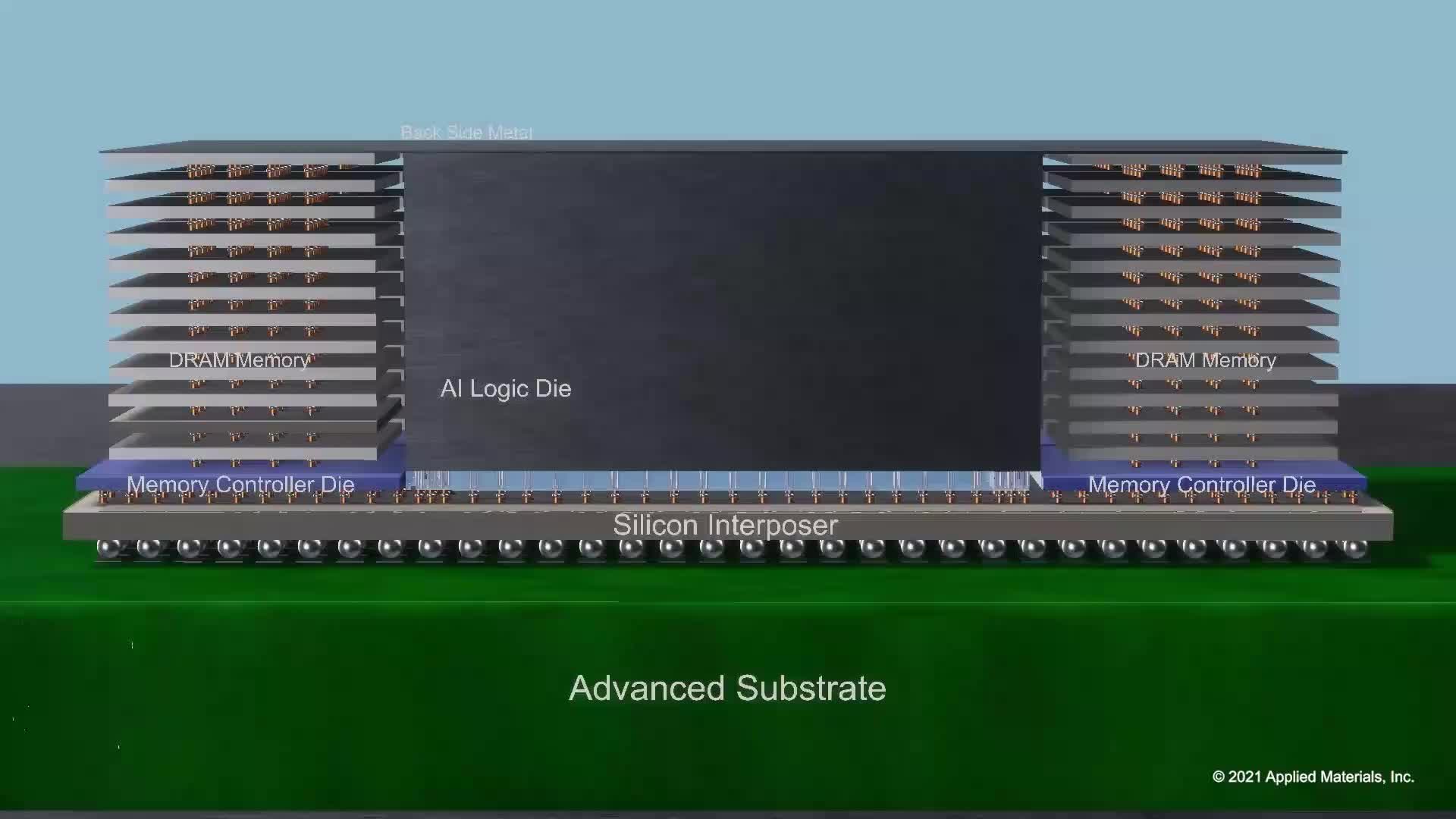

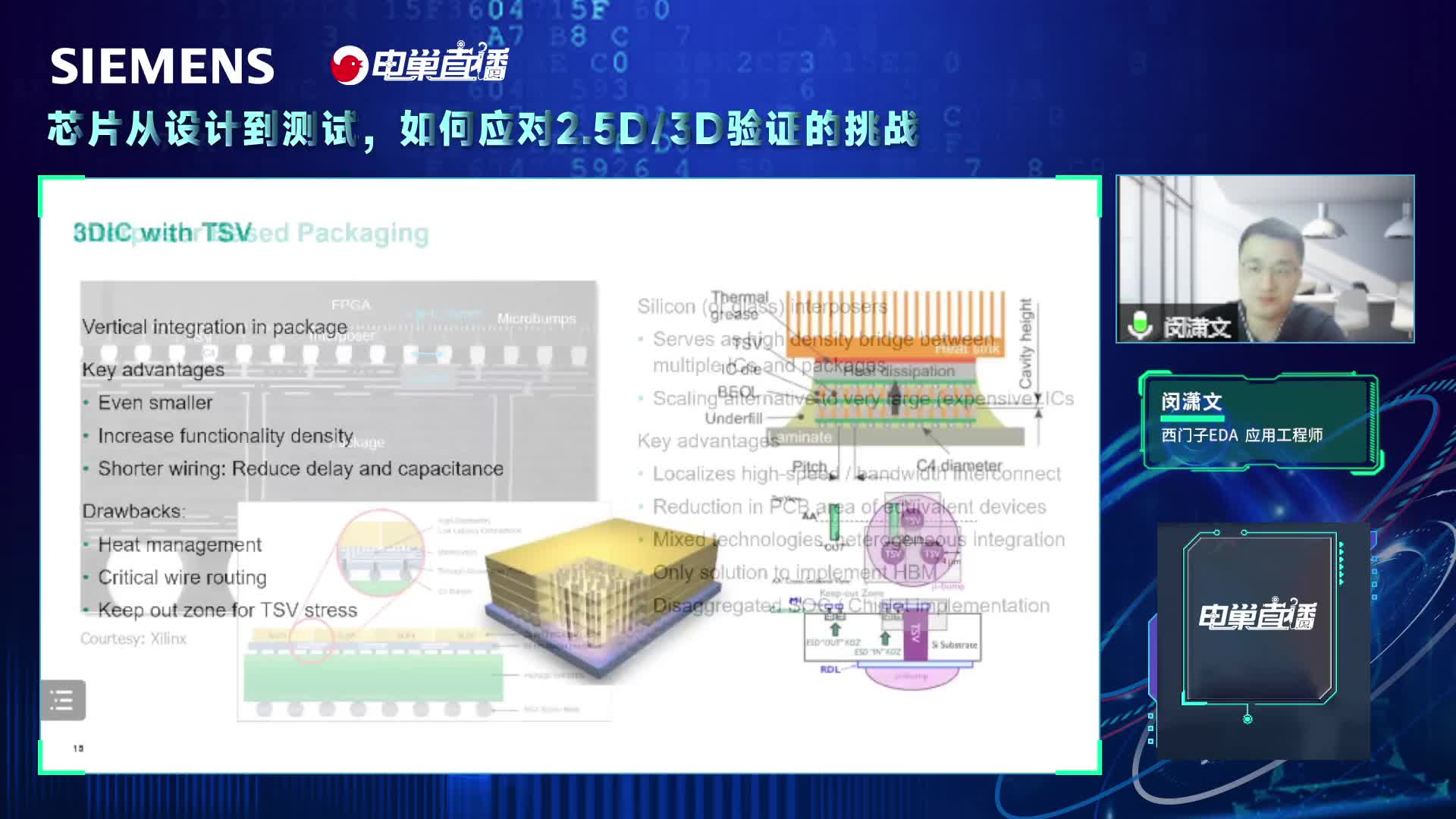

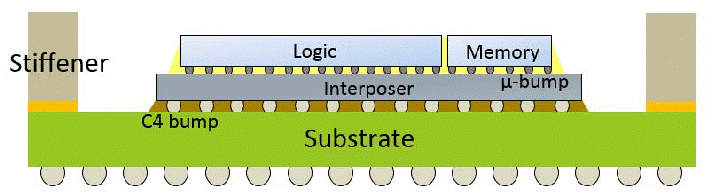

硅通孔(TSV):2.5D封裝TSV充當多顆裸片和電路板之間橋梁

中介層是一種由硅及有機材料制成硅基板,是先進封裝中多芯片模塊傳遞電信號的管道,可以實現(xiàn)芯片間的互連,也可以實現(xiàn)與封裝基板的互連,充當多顆裸片和電路板之間的橋梁。硅中介層是一種經(jīng)過驗證的技術,具有較高的細間距布線能力和可靠的TSV能力,可以實現(xiàn)高密度I/O需求,在2.5D封裝中扮演著關鍵角色。 2.5D集成關鍵在于中介層Interposer:1)中介層是否采用硅轉接板;2)中介層是否采用TSV,在硅轉接板上穿越中介層(TSV),在玻璃轉接板上穿越中介層(TGV)。

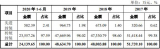

硅通孔(TSV):TSV在2.5D封裝中應用實例——CoWoS

CoWoS實質為2.5D封裝,依據(jù)中介層采用不同技術劃分為CoWoS-S、CoWoS-L及CoWoS-R三大技術。CoWoS-S采用硅中介層,為高性能計算應用提供最佳性能及最高晶體管密度;CoWoS-R類似InFO技術,利用RDL中介層進行互連,更強調小芯片間互連;CoWoS-L結合CoWoS-S及InFO技術優(yōu)點,使用夾層與LSI(局部硅互連)芯片進行互連,使用RDL層進行電源與信號傳輸,提供最靈活集成。

混合鍵合(HB):混合鍵合利用范德華力實現(xiàn)

混合鍵合是通過分子間作用力(范德華力) 實現(xiàn),使用化學機械拋光對大馬士革布線層進行表面處理,CMP過程還可以減少Cu線路腐蝕和Cu凹陷。當Cu和Si?2的光滑界面相互接觸時形成范德華力。為增強表面結合力,通常需要增加等離子體活化工序,然后再通過高精度倒裝熱壓工序,實現(xiàn)多界面之間混合鍵合。 HB技術簡化3D堆疊布線層,與含有TSV的3D堆疊技術相比,HB工藝中銅觸點pitch size少于10微米,可實現(xiàn)更高互聯(lián)密度HB技術,且可直接省略再布線,使設計難度降低,避免再布線及倒裝回流焊可提高可靠性。

板級埋入式封裝:無需Si中介層及TSV工藝

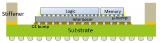

EMIB是將帶有多層導電金屬(back end of line,BEOL)互連的超 薄硅片埋入有機封裝基板的最上層,通過焊球與倒裝芯片的連接, 以實現(xiàn)兩個或多個芯片之間的局部高密度互連。與傳統(tǒng)封裝中在基 板表面貼裝芯片或元件不同,板級埋入式封裝直接將芯片或元件嵌 入基板中間,因此它具有更短的互連路徑、更小的體積、更優(yōu)的電 熱性能及更高的集成度。與臺積電的CoWoS-S封裝相比,EMIB封裝既不需要TSV工也不需要Si 中介層,因此其具有封裝良率高、設計簡單、成本更低等優(yōu)點。

產(chǎn)業(yè)鏈:材料與設備任重道遠,先進封裝粲然可觀

封裝材料:各類半導體材料集中度較低,國產(chǎn)替代呈現(xiàn)兩極分化

先進封裝發(fā)展拉動封裝材料需求,2027年市場規(guī)模有望達300美元。根據(jù)SEMI數(shù)據(jù),2022年全球半導體材料市場收入增長8.9%達727億美元,其中封裝材料市場規(guī)模為280億美元,同比增長6.3%,其中有機基板領域增長積極推動封裝材料市場;介電材料和底部填充的發(fā)展推動對扇入和扇出晶圓級封裝 (FOWLP)、倒裝芯片和 2.5D/3D 封裝的強勁需求。使用RDL(重新分布層)硅中介層和有機中介層等新型基板技術也是封裝解決方案關鍵增長動力,2027年全球半導體封裝材料市場預計達到298億美元。

高端基板:先進封裝帶動高端基板需求,國產(chǎn)化亟待突破

先進封裝技術帶動ABF載板需求。先進封裝能協(xié)助芯片整合在面積不變下,促成更高效率,透過芯片間互聯(lián)封裝技術,完成來自不同制程、不同材料各個芯片置于中介層基板之上進行整合,要將這些芯片整合在一起,就是需要更大ABF載板來放置。FCBGA憑借內(nèi)部采FC、外部采BGA的封裝方式,成為目前主流的封裝技術,作為ABF載板應用較多的封裝技術,F(xiàn)CBGAI/O數(shù)量達到32-48,因而擁有非常優(yōu)異的性能與成本優(yōu)勢。此外,2.5D封裝I/O數(shù)量是2D FC封裝數(shù)倍以上,在顯著提升高階芯片效能同時,所需的ABF載板也變得更為復雜。Intel嵌入式封裝技術,I/O數(shù)高達250-1000,提高芯片互連密度,并且將硅中介層內(nèi)嵌于ABF,增加ABF面積、層數(shù)與制作難度,將消耗更多ABF產(chǎn)能。

先進封裝設備:晶圓劃片前融入封裝工藝步驟,前道設備需求加劇

先進封裝處于晶圓制造與封測中的交叉區(qū)域。先進封裝要求在晶圓劃片前融入封裝工藝步驟,具體包括應用晶圓研磨薄化、線路重排(RDL)、凸塊制作(Bumping)及三維硅通孔(TSV)等工藝技術。先進封裝更多在晶圓層面上進行,采用前道制造方式來制作后道連接電路,工藝流程的相似性使得兩者使用設備也大致相同,其中倒裝就要采用植球、電鍍、光刻、蝕刻等前道制造的工藝,2.5D/3D封裝TSV技術就需要***、涂膠顯影設備、濕法刻蝕設備等,從而使得晶圓制造與封測前后道制程中出現(xiàn)中道交叉區(qū)域。

先進封裝:2027年先進封裝市場規(guī)模有望達650億美元

先進封裝市場有望達650億美元,芯片倒裝占比最大,芯片嵌入式封裝增速最快。根據(jù)Yole數(shù)據(jù),2021年全球先進封裝市場規(guī)模為374億美元,其中芯片倒裝占比最大為70%,2.5D/3D封裝次之;2027年全球先進封裝市場規(guī)模預計為650億美元,其中芯片倒裝占比為66%(較2021年下滑4pcts),2.5D/3D占23%,約150億美元,芯片嵌入式增速最快,21-27年CAGR為24%。

行業(yè)現(xiàn)狀:制造與IDM廠商入駐先進封裝,開辟中道工藝

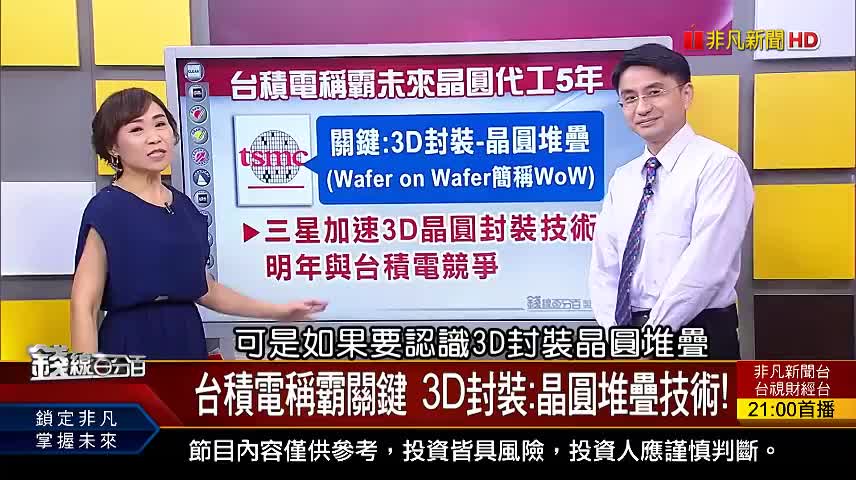

臺積電:前段(CoW/WoW)+后段(oS/InFO) = 3D Fabric

下游應用多點爆發(fā)挑戰(zhàn)計算極限,更快,更節(jié)能芯片需求增加。隨著云計算、大數(shù)據(jù)分析、人工智能、神經(jīng)網(wǎng)絡訓練、人工智能推理、先進智能手機移動計算及自動駕駛等應用領域不斷發(fā)展,需要更快、更節(jié)能的芯片來滿足計算需求。在3D芯片堆疊方面,臺積電在系統(tǒng)整合芯片(TSMC-SoIC)技術加入微凸塊,以支持更具成本敏感度應用;CoWoS平臺得以實現(xiàn)先進邏輯及高帶寬存儲器整合,適用于人工智能、機器學習及數(shù)據(jù)中心等HPC應用;整合型扇出層疊封裝技術(InFO_PoP)及InFO-3D支持移動應用,InFO-2.5D則支持HPC小芯片整合。

三星:I-Cube2.5D=I-Cube S + I-Cube E + H-Cube

I-CUBE S是一種異構技術,將一塊邏輯芯片與一組高帶寬存儲器 (HBM) 裸片水平放置在一個硅中介層上,實現(xiàn)高算力、高帶寬數(shù)據(jù)傳輸及低延遲等特點;I-Cube E技術采用硅嵌入結構,不僅具有硅橋精細成像優(yōu)勢,也同時擁有PLP(面板級封裝技術)大尺寸、無硅通孔 (TSV) 結構的RDL中介層等特點;H-Cube是一種混合基底結構,將精細成像的ABF基底和HDI(高密度互連)基底技術相結合,可在I-Cube 2.5D封裝中實現(xiàn)較大封裝尺寸。

Intel:嵌入式多芯片互連橋(EMIB)為Intel2.5D封裝亮點

結構簡單及信號干擾低是英特爾主導開發(fā)EMIB路線主要優(yōu)勢,應用這一技術,封裝過程中無需制造覆蓋整個芯片硅中介層,以及遍布在硅中介層上大量硅通孔(TSV),而只需使用較小硅橋在裸片間進行互聯(lián)即可。與普通封裝技術相比,由芯片I/O 至封裝引腳連接并未發(fā)生變化,而無需再通過TSV或硅中介層進行走線。在降低不同裸片間傳輸延時同時也減少信號傳輸干擾。

安靠科技:深度布局TSV-less工藝(FOWLP,Chip last, Die face down)

SLIM及SWIFT方案均采用TSV-less工藝,簡化2.5D TSV硅中介層運用時PECVD及CMP工序。SLIM利用前道代工,在硅片表面的無機介質層上制作1μm,甚至亞微米金屬布線,再用有機介質層制作金屬布線,通過倒裝互連、芯片塑封后,刻蝕去掉硅片,再制作BGA,完成三維集成。SWITT特點是在Carrier基板上制作多層布線,與芯片通過微凸點倒裝,然后塑封,通過穿透模塑料高銅柱實現(xiàn)三維垂直互連,進一步在背面再做一層布線,用于與上封裝體進行高密度互連。

應用與需求:芯粒IP復用延續(xù)摩爾定律,新建晶圓廠與產(chǎn)線擴產(chǎn)共促封測需求

Chiplet:大道至簡,芯粒IP復用構建高集成度芯片

Chiplet(芯粒,也叫小芯片)將一類滿足特定功能Die(裸片)通過Die-to-Die內(nèi)部互聯(lián)技術將多個模塊芯片與底層基礎芯片封裝在一起,形成一個系統(tǒng)芯片(Soc芯片),從而實現(xiàn)一種新形式IP復用。 Chiplet技術背景下,可將大型單片芯片劃分為多個相同或者不同小芯片,這些小芯片可以使用相同或者不同工藝節(jié)點制造,再通過跨芯片互聯(lián)及封裝技術進行封裝級別集成,降低成本的同時獲得更高的集成度。

應用: 5G/物聯(lián)網(wǎng)/高性能運算/智能駕駛/XR等帶動先進封裝需求

從長期來看,先進封裝技術必將隨著終端應用的升級和對芯片封裝性能的提升而蓬勃發(fā)展。隨著新技術演進,以2.5D/3D為代表的先進封裝工藝已深入大多數(shù)高端芯片生產(chǎn)。

應用:手機與消費領域為先進封裝最大應用領域

手機與消費領域仍為先進封裝最大應用領域,電信與基礎設施占比增速最快。根據(jù)Yole數(shù)據(jù),2022年,移動和消費者占先進封裝市場總量70%,預計2022年至2028年復合年增長率為7%,到2028年將占先進封裝收入61%。電信和基礎設施領域增長最快,預計2022年至2028年復合年增長率約為17%,預計到2028年將占先進封裝市場27%;預計2028年汽車占市場9%,而其他(醫(yī)療、工業(yè)和航空航天/國防等領域)將占3%。

需求:中國晶圓廠獨占鰲頭,預計至2024年底建立50座大型晶圓廠

中國晶圓廠數(shù)目獨占鰲頭,韓國系后起之秀。根據(jù)電子工程專輯數(shù)據(jù),截至2021年底中國(包含中國臺灣)晶圓廠數(shù)目為78座,成為世界上擁有最多晶圓廠國家,美國(46)、日本(44)分別排名第二、第三。近年來韓國加大集成電路投資規(guī)模,2014年超過德國成為世界第四大晶圓制造國家,截至2021年底韓國擁有25座晶圓廠,后發(fā)動力不可小覷。根據(jù)SEMI數(shù)據(jù),預計至2024年底,中國將新建立50座大型晶圓廠,其中中國臺灣預計投入19座。

報告節(jié)選:

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論