電子發燒友網: 繼 Virtex-7 2000T 之后,賽靈思日前又推出一款 7 系列的高端器件 Virtex-7 H580T,這是全球首款異構 3D FPGA,該技術是在堆疊硅片互聯(SSI)技術的基礎上,對 FPGA 和 28Gbps收發器

2012-07-06 10:42:43 1056

1056

1. BGA和CSP封裝技術詳解 2.?干貨分享丨BGA開路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 5181

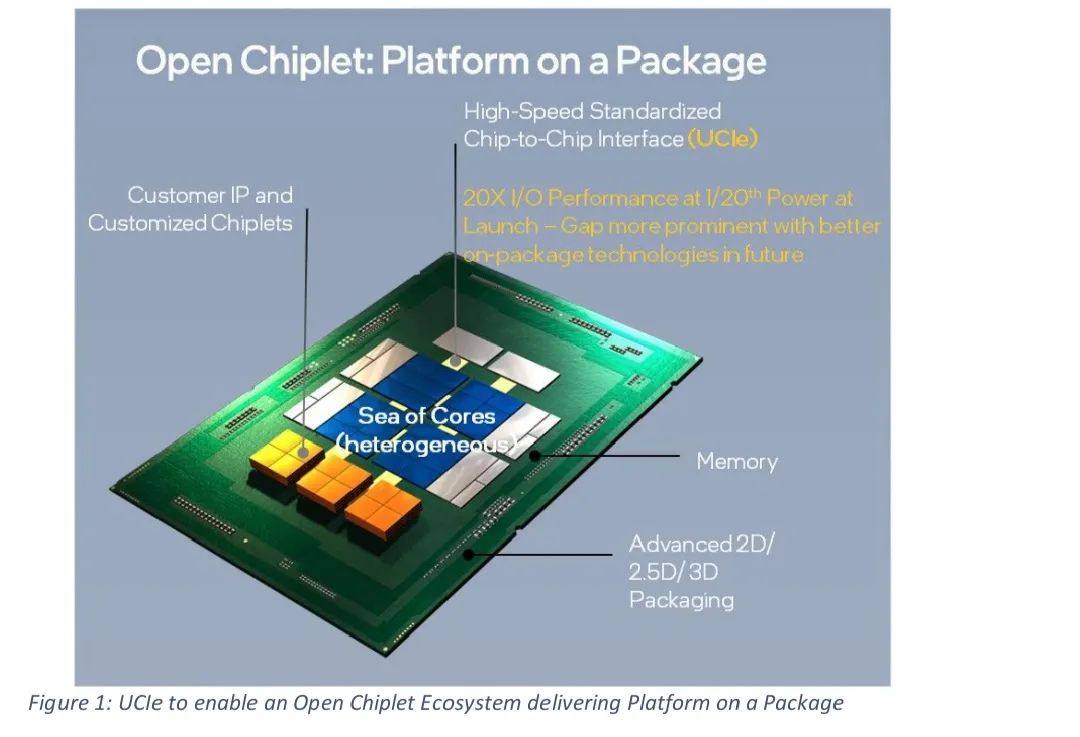

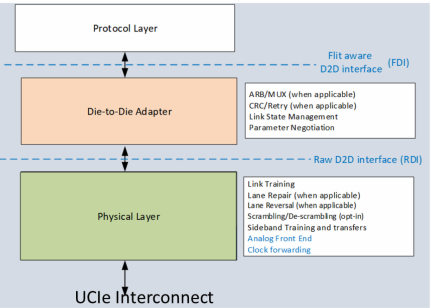

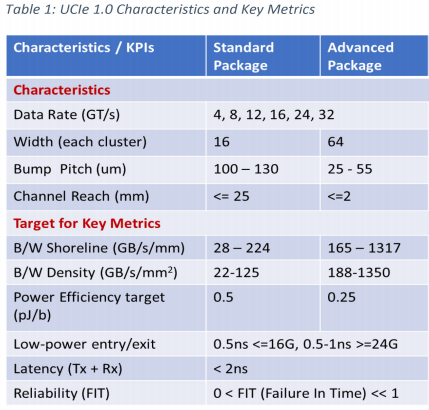

5181 UCIe[4]是一種開放的行業標準互連,為異構芯片間提供了高帶寬、低延遲、高電源效率和高性價比的封裝內連接,以滿足整個計算系統的需求。

2022-10-10 09:33:49 2181

2181 )在后摩爾時代的技術趨勢下, 射頻系統可持續吸收異構集成(HETEROGENEOUS INTEGRATION) / 系統級封裝的最新技術, 實現更復雜、 更高性能的系統集成

2022-12-14 10:35:13 1001

1001 為適應異構集成技術的應用背景,封裝天線的實現技術也應有所變化,利用封裝工藝的優點以實現更佳的性能。

2024-02-29 11:11:30 157

157

,戈登·摩爾就知道芯片級別的異構集成將是一種前進的方式。這就是英特爾今天所做的:使用先進的封裝技術,將公司的所有技術集成到一個集成電路中。 第二個層次 系統異構 第二個異構集成級別是在系統級。我們

2020-07-07 11:44:05

令集、不同功能的算力單元,組合起來形成一個混合的計算系統,使其具有更強大、更高效的功能。如何在異構計算場景下構建可信執行環境呢?華為可信計算首席科學家、IEEE硬件安全與可信專委會聯席主席金意兒教授在第一屆

2023-08-15 17:35:09

,無論是神經網絡處理器還是圖像處理器。異構計算的存在可以說創造了另一個維度,這個維度上我們又有了堆性能的空間,小至手機SoC、汽車芯片,大到服務器芯片和超算處理器,異構帶來了更大的算力。但與此同時

2021-12-26 08:00:00

詳解面向TDD系統手機的SAW濾波器的技術動向

2021-05-10 06:18:34

詳解高亮度LED的封裝設計

2021-06-04 07:23:52

研究院(先進電子封裝材料廣東省創新團隊)、上海張江創新學院、深圳集成電路設計產業化基地管理中心、桂林電子科技大學機電工程學院承辦的 “第二期集成電路封裝技術 (IC Packaging

2016-03-21 10:39:20

《集成電路芯片封裝技術》是一本通用的集成電路芯片封裝技術通用教材,全書共分13章,內容包括:集成電路芯片封裝概述、封裝工藝流程、厚膜與薄膜技術、焊接材料、印制電路板、元件與電路板的連接、封膠材料

2012-01-13 13:59:52

和其他LSI集成電路都起著重要的作用。新一代CPU的出現常常伴隨著新的封裝形式的使用。芯片的封裝技術已經歷了好幾代的變遷,從DIP、QFP、PGA、BGA到CSP再到MCM,技術指標一代比一代先進,包括

2018-08-28 11:58:30

集成電路芯片封裝技術知識詳解本電子書對封裝介紹的非常詳細,所以和大家分享。因為太大,沒有上傳。請點擊下載。[此貼子已經被作者于2008-5-12 22:45:41編輯過]

2008-05-12 22:44:28

別告訴我把它打開,然后把那里面的庫提取出來。我以前在選PCB封裝時,可以直接選集成庫里的封裝,最近不知怎么的集成庫里的封裝就不顯了,我希望可以把這個功能調出來,使用時會方便很多。電腦重啟了,軟件重裝

2012-11-09 18:40:18

封裝技術在電子行業中將具有越來越廣泛的應用前景。作為一種集成度高、密度大、功耗低的封裝方式,BGA封裝技術不僅能夠提高電子產品的性能和可靠性,而且還能夠幫助企業降低成本和提高市場競爭力。 總之

2023-04-11 15:52:37

DIP封裝(Dual In-line Package),也叫雙列直插式封裝技術,指采用雙列直插形式封裝的集成電路芯片,絕大多數中小規模集成電路均采用這種封裝形式,其引腳數一般不超過100。DIP封裝

2018-08-23 09:33:08

所謂“CPU封裝技術”是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術。以CPU為例,我們實際看到的體積和外觀并不是真正的CPU內核的大小和面貌,而是CPU內核等元件經過封裝后的產品

2018-08-29 10:20:46

解析HSA----CPU+GPU異構系統架構

2021-02-03 07:07:34

1、MPU6050使用詳解及DMP姿態解算MPU-60X0 是世界上第一款集成 6 軸 MotionTracking 設備。它集成了 3 軸 MEMS 陀螺儀,3 軸 MEMS加速度計,以及一個可

2022-04-14 16:04:14

, 繼承了該接口的諸多優點,也更適合此類場景應用,為用戶提供了一種算力邊緣側部署的解決方案,同時MXM接口還可以為用戶提供其它架構算力模塊搭配方案,如MXM界面的寒武紀算力卡,MXM界面的登臨算力卡等

2022-05-18 15:52:40

PCB封裝詳解手冊

2012-08-20 15:06:23

PCB封裝詳解:包含各種集成電路的PCB封裝,給需要的你。

2012-03-18 00:18:42

;lt;font face="Verdana">PCB封裝詳解手冊下載</font><br/>

2009-11-30 17:16:42

PCB封裝詳解目錄

2012-08-18 00:07:47

NPU算力集成有哪些特性呢?RK1808內置的NPU算力集成有何功能?

2022-02-16 07:52:14

不同制程架構、不同指令集、不同功能的算力單元,組合起來形成一個混合的計算系統,使其具有更強大、更高效的功能。如何在異構計算場景下構建可信執行環境呢?華為可信計算首席科學家、IEEE硬件安全與可信專委會

2023-04-19 15:20:32

目的本文介紹廣州星嵌DSP C6657+Xilinx Zynq7035平臺下Xilinx Zynq7035算力指標。基本概念FLOPs/FLOPSFLOPs,Floating Point

2022-12-15 21:19:38

—KHeavyHash。在市場上,有一款挖掘機可以滿足這個要求,那就是iBeLink ks max 10.5T。

iBeLink ks max 10.5T是一款專為Kaspa挖掘而設計的挖掘機,它的算力

2024-02-20 16:11:20

已下是rx580顯卡算力9-11 Mh 沒有開啟計算模式,挖幾分種重啟自動開啟,計算模式只支持WIN1022-28 Mh 原版BIOS,開啟時序,并設置超頻29-32 Mh 正常算力,卡體質不同算力

2021-07-23 06:59:09

神經網絡處理內核 NPU,算力達到 128 GOPS。多核異構的設計使芯片能以較低功耗滿足音頻及圖像視頻的 AI 應用需求。 環境搭建 本次體驗使用的開發環境是 Ubuntu 20.04

2022-11-23 16:09:42

1、什么是性能?什么是算力?這兩個概念是統一的,性能是微觀的概念,而算力是宏觀的概念。性能和算力的關系,如下面這個簡化公式:總算力 = 芯片性能 x 芯片數量 x 算力利用率。這三個參數,也對應了算

2022-11-24 16:37:10

什么是異構多處理呢?為什么需要異構多處理系統

2021-02-26 06:59:37

一、概述V853 是一顆面向智能視覺領域推出的新一代高性能、低功耗的處理器SOC,芯片采用三核異構設計,同時搭配了全志自研的新一代視覺處理引擎和疾風系統,最高算力可達1T的NPU助力V853可廣泛

2022-07-01 17:41:20

(INT8)稠密算力。啟明930可獨立用于AI加速卡,亦可通過D2D擴展多種功能型Side Die進行集成,具備多種產品形態。北極雄芯由清華大學姚期智院士創建的交叉信息核心技術研究院自2018年起孵化

2023-02-21 13:58:08

【作者】:荀小苗;羅進文;【來源】:《電信快報》2010年02期【摘要】:MIH(介質獨立切換)是實現下一代異構網絡融合的關鍵技術。文章分析了基于MIH的WLAN-UMTS(無線局域網-通用無線通信

2010-04-24 09:10:39

沒有讀者認識到發生在3DIC集成中的技術進步,他們認為該技術只是疊層和引線鍵合,是一種后端封裝技術。而我們該如何去拯救3DIC集成技術?

2021-04-07 06:23:51

如何往AD集成庫增加PCB封裝?

2019-09-16 10:28:13

背景介紹數據、算法和算力是人工智能技術的三大要素。其中,算力體現著人工智能(AI)技術具體實現的能力,實現載體主要有CPU、GPU、FPGA和ASIC四類器件。CPU基于馮諾依曼架構,雖然靈活,卻

2021-07-26 06:47:30

`求教大蝦,附圖所示的SOP20封裝集成電路是啥?最好有詳細的相關技術資料。`

2018-04-08 08:12:57

我有一個reference capacitor 50pF一個variable capacitor 50 + (0-5)pF是用來計算其壓力有什麼IC適合我使用 THANKS!

2018-09-30 14:10:24

目前市場上炙手可熱的芯片礦機 當數芯動 A10PRO , 7g 版本的 算力750m 功耗 1300w 這款機器廠家出廠時預定價格在 48900 左右那時候定的客戶到如今 機器價格已經漲到

2021-07-23 07:39:58

;?引腳數。引腳數越多,越高級,但是工藝難度也相應增加;其中,CSP由于采用了FlipChip技術和裸片封裝,達到了 芯片面積/封裝面積=1:1,為目前最高級的技術;芯片封裝測試流程詳解ppt[hide]暫時不能上傳附件 等下補上[/hide]

2012-01-13 11:46:32

車載移動異構無線網絡架構及關鍵技術是什么?

2021-06-07 06:29:57

集成電路封裝技術詳解包括了概述,陶瓷封裝,塑料封裝,金屬封裝,其它封裝等。

2008-05-12 22:41:56 702

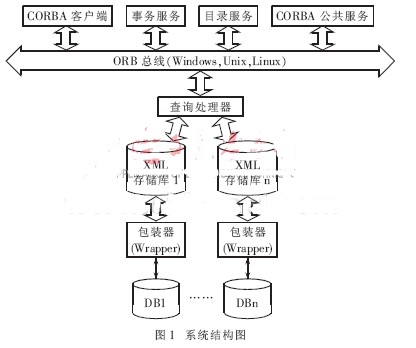

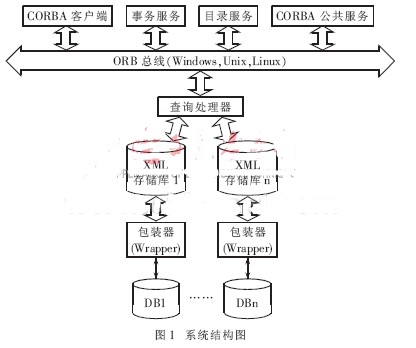

702 為解決企業分布式多源異構地理空間數據互操作的瓶頸問題,設計了基于WebServices 的四層多源異構空間信息集成框架。利用Web Services 技術,OGC 地理信息服務實現規范,和W3C 標準的

2009-08-15 08:11:48 20

20 針對傳統技術在分布式異構系統集成領域存在的問題,提出了基于Web Services 的系統應用集成解決方案。通過對Web Services 技術的特點、體系結構及其核心技術的分析,設計了基于We

2009-08-21 11:31:01 22

22 本文給出了一種基于本體的異構數據源的集成方案,該方案從根本上解決了企業內部數據源的語法異構和語義異構;同時,也為企業內部的信息

2009-09-04 09:24:50 13

13 本文件提供了異構數據源集成方案本體論為基礎,這項計劃平息基本上句法和語義的異構數據源的非均質性,同時也規定了企業內部信息的有效技術措施,及時

2009-09-09 09:13:01 36

36 基于中間件技術的異構機器人系統設計及實現:基于C++CORBA中間件的技術規范和具體應用,對異構機器人系統的集成技術進行了研究.以ACE?TAO作為開發平臺,

2010-03-18 16:23:48 17

17 分析了數字化校園建設過程中異構數據集成的重要性,詳細介紹了異構數據庫系統的特征和異構數據集成的幾種方法,研究XML在異構數據集成方面的應用。在此基礎上,設計出基于XM

2010-12-24 15:59:25 14

14 針對高校多業務系統異構 數據庫 的特征,提出基于Web Services 的校園異構數據庫數據集成的框架體系結構,并對數據集成的關鍵技術進行研究和設計,為校園數據共享和互聯互通提供一

2011-06-07 17:18:02 18

18 LED 在照明領域的廣泛應用,集成封裝也將得到快速發展。 目前,實現大功率LED 照明的方法有兩種:一是對單顆大功率LED 芯片進行封裝,二是采用多芯片集成封裝。對于前者來說,隨著芯片技術的發展,尺寸增大,品質提高,可通過大電流驅動實現

2017-10-10 17:07:20 9

9 為了提高飛機維修排故效率,針對飛機維修排故信息多源性、分布式和異構的特點,鑒于本體在解決語義異構問題上的優勢,研究提出了基于本體的多源異構飛機維修排故信息協同集成技術路線,給出了飛機維修排故本體信息

2017-11-27 14:47:38 0

0 。利用中間件(Middleware)技術集成各種異構數據時,不用改變原始數據的存儲和管理方式,可集中為異構數據源提供一個統一的高層檢索服務,是實現異構數據集成的理想解決方案。

2019-05-09 08:17:00 2083

2083

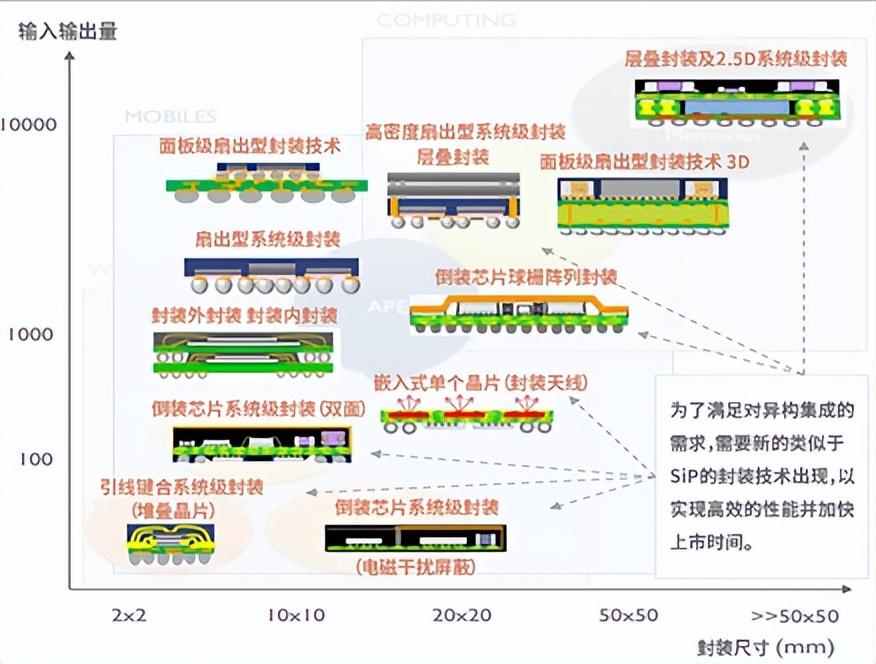

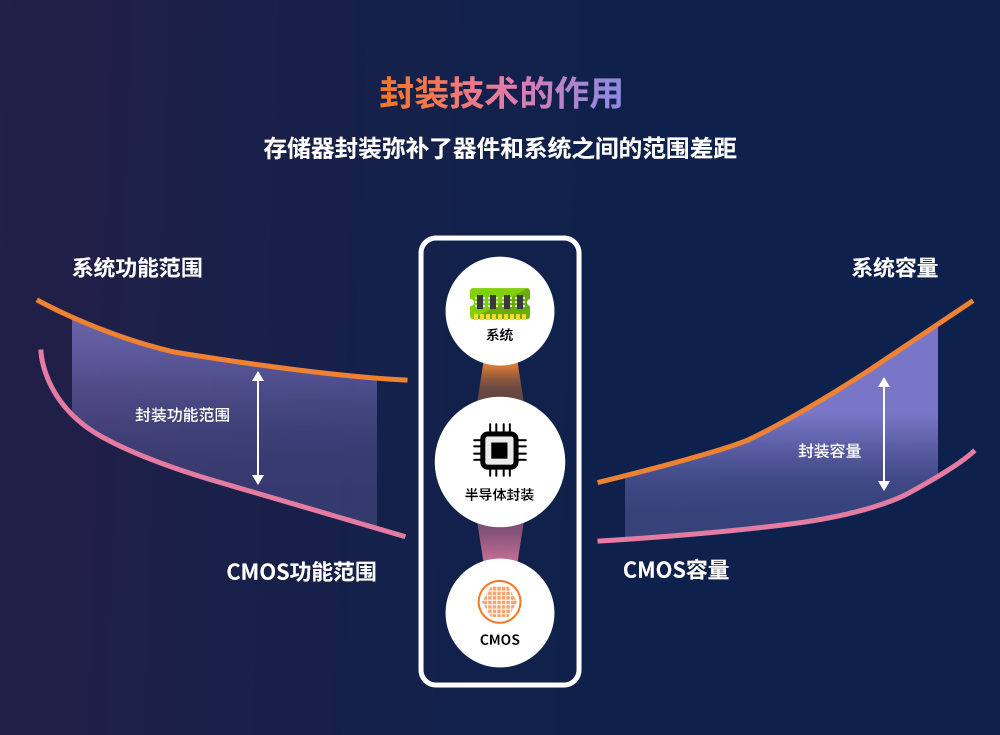

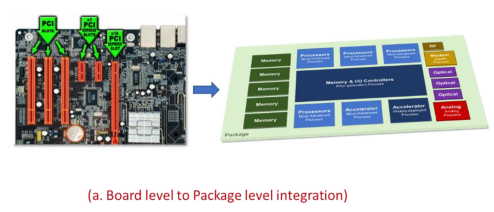

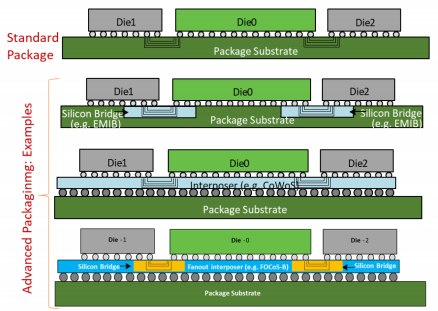

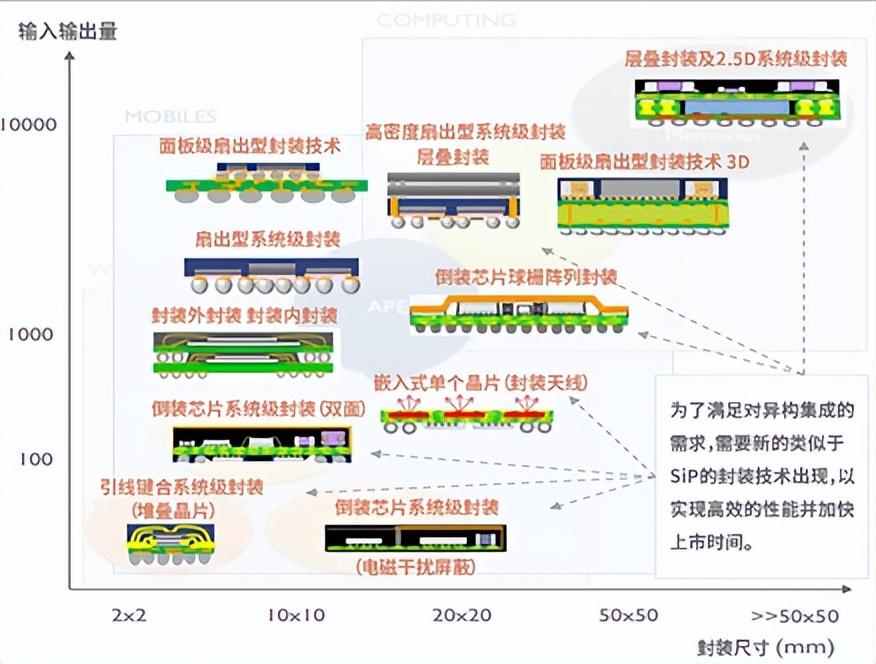

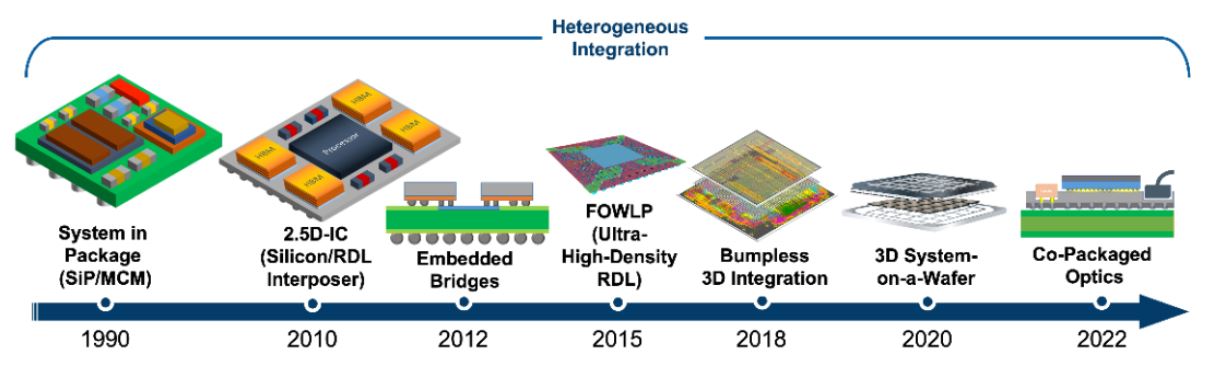

異構 3D 系統級封裝集成 3D 集成與封裝技術的進步使在單個封裝(包含采用多項技術的芯片)內構建復雜系統成為了可能。 過去,出于功耗、性能和成本的考慮,高級集成使用單片實施。得益于封裝與堆疊技術

2021-03-22 09:27:53 2028

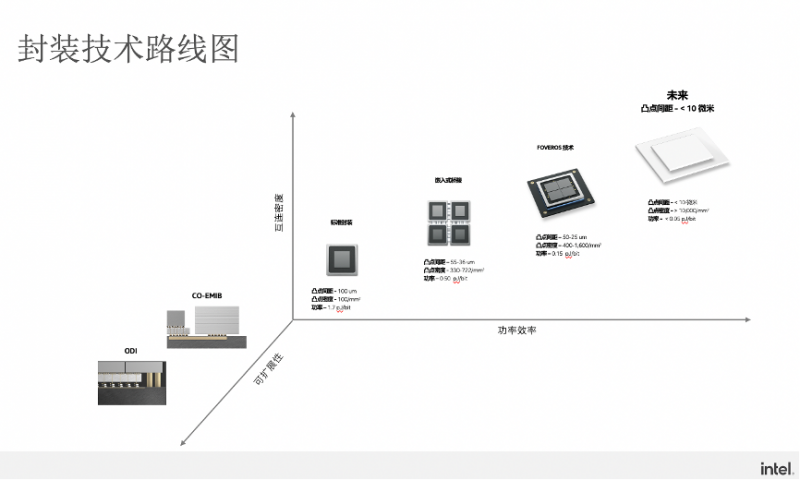

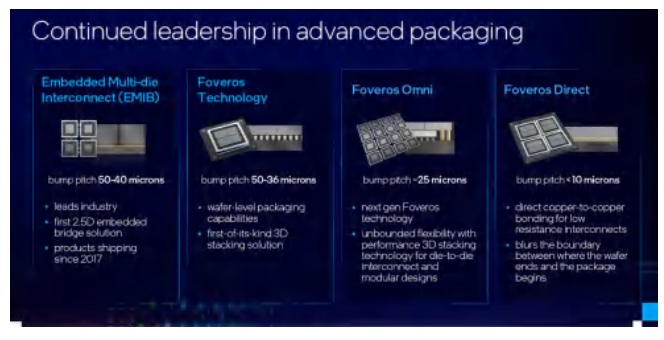

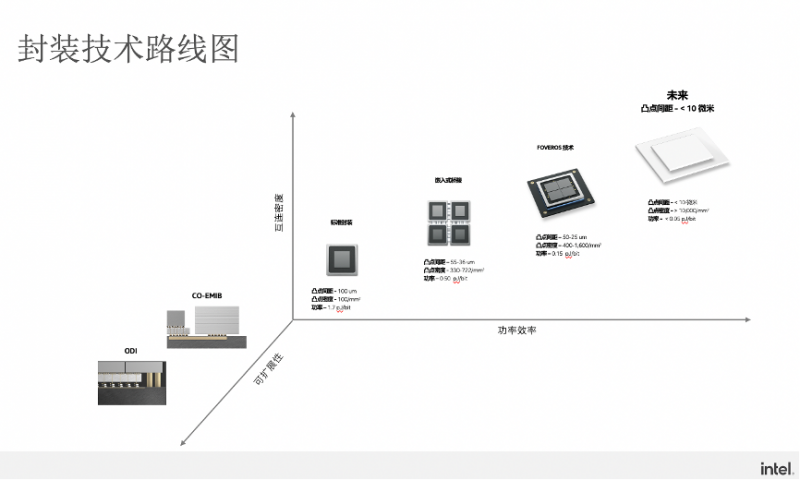

2028 外形尺寸和提高帶寬的機會。?從Intel 的先進封裝技術路線圖可以看出,三大維度是未來方向:X軸代表功率效率,Y軸代表互連密度,Z軸代表可擴展性。??多區塊異構集成提升功率效率?Johanna

2021-06-25 11:13:24 1259

1259

異構集成基礎:基于工業的2.5D/3D尋徑和協同設計方法

2021-07-05 10:13:36 12

12 MOS管表面貼裝式封裝方式詳解

2021-07-07 09:14:48 0

0 今年3月,由日月光、AMD、ARM、谷歌 Cloud、英特爾、微軟、高通、三星和臺積電十家公司成立UCIe(Universal Chiplet Interconnect Express)產業聯盟。該聯盟是由全球科技行業巨頭共同推出的一個全新的通用芯片互連標準。

2022-04-07 11:12:03 804

804 上月初,英特爾攜手日月光半導體(ASE)、AMD、Arm、谷歌云、Meta、微軟、高通、三星和臺積電等廠商發起UCIe產業聯盟(通用芯粒高速互連),意欲推行開放的晶片間互連標準。可以說UCIe的出現

2022-04-08 11:26:53 791

791 三維集成技術可分為三維晶圓級封裝、基于三維中介層(interposer)的集成、三維堆疊式集成電路(3D staked IC,3D-SIC)、單片三維集成電路、三維異構集成等。

2022-04-25 15:35:42 1513

1513 國產EDA行業的領軍企業芯和半導體近日宣布正式加入UCIe(Universal Chiplet Interconnect Express)產業聯盟。芯和半導體早在去年年底已全球首發了“3DIC先進封裝設計分析全流程”EDA平臺,是其成為首家加入UCIe聯盟的中國本土EDA企業的關鍵推動力。

2022-05-09 11:28:07 2194

2194 實現Chiplets封裝集成的動機有很多。為了滿足不斷增長的性能需求,芯片面積不斷增加,有些設計甚至會超出掩模版面積的限制,比如具有數百個核心的多核 CPU,或扇出非常大的交換[曹1] 電路(Switch)。

2022-07-25 17:30:52 752

752 UCIe 是唯一為芯片到芯片接口定義完整堆棧的規范。其他標準僅關注特定層,并且與 UCIe 不同,不為協議棧的完整裸片到裸片接口提供全面的規范。

2022-09-28 10:30:34 805

805 UCIe能夠滿足幾乎所有計算領域,包括云端、邊緣端、企業、5G、汽車、高性能計算和移動設備等,對算力、內存、存儲和互連不斷增長的需求。UCIe 具有封裝集成不同Die的能力,這些Die可以來自不同的晶圓廠、采用不同的設計和封裝方式。

2022-11-02 12:51:37 621

621 世芯電子正式宣布以貢獻者(Contributor)會員身份加入UCIe?(Universal Chiplet Interconnect Express?)產業聯盟,參與UCIe技術標準的研究,結合

2022-12-22 14:55:26 948

948 技術標準的研究,結合本身豐富的先進封裝(2.5D及CoWoS)量產及HPC ASIC設計經驗,將進一步鞏固其高性能ASIC領導者的地位。 UCIe可滿足來自不同的晶圓廠、不同工藝、有著不同設計的各種

2022-12-22 20:30:36 1989

1989 一文詳解精密封裝技術

2022-12-30 15:41:12 1239

1239 的領先企業,廣立微將與聯盟內的其他成員一道,共同致力于下一代UCIe技術標準的研究與應用,結合自身在測試芯片設計和良率分析領域的優勢 ,為推動先進封裝技術的開發做出積極貢獻。 關于UCIe UCIe成立

2023-02-21 09:43:29 458

458

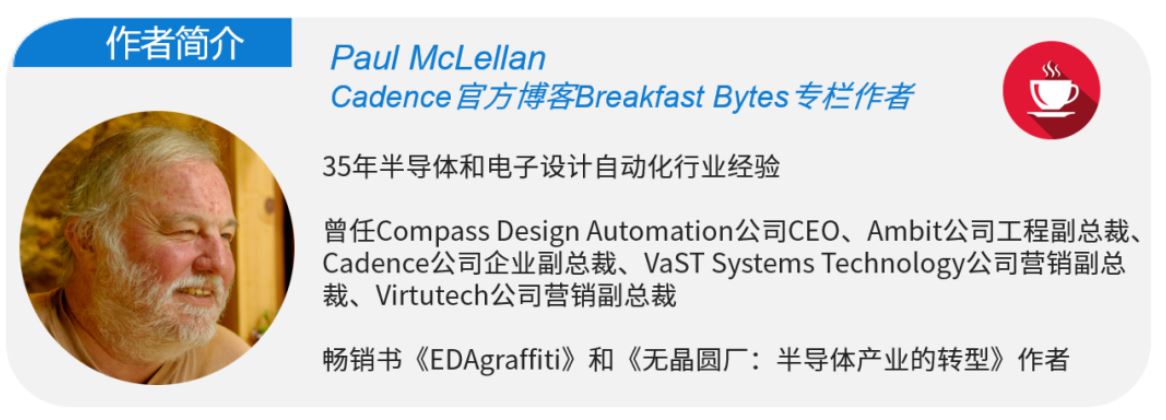

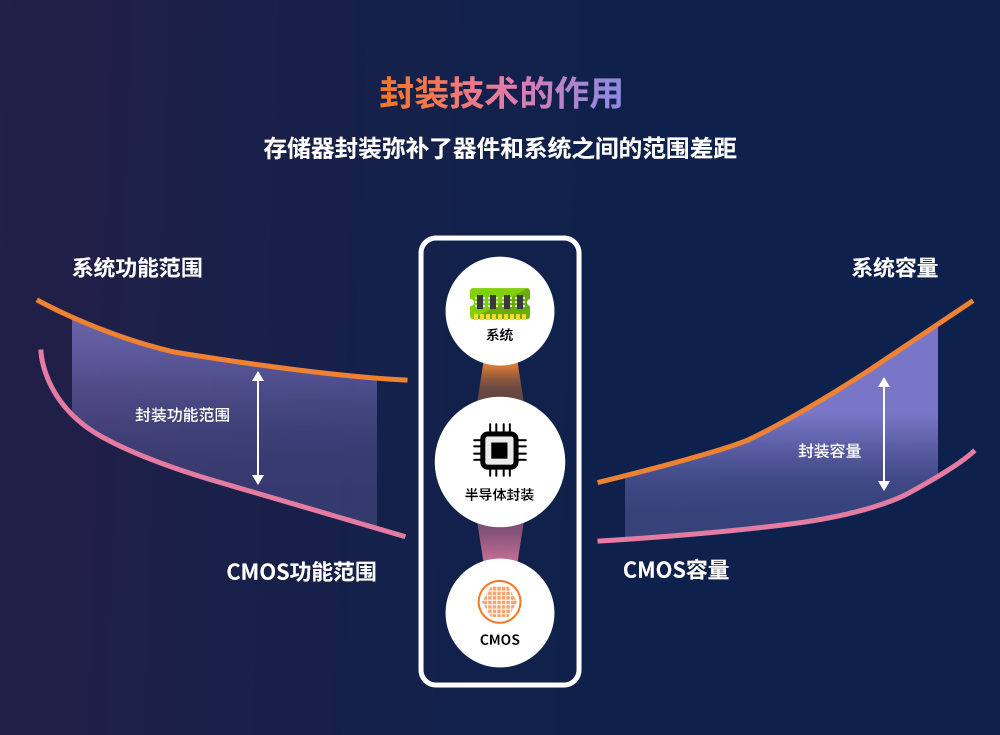

晶體管微縮成本的不斷提升,促使行業尋找創新方法,更新迭代提升芯片和系統的性能。正因此,異構集成已成為封裝技術最新的轉折點。

2023-04-06 18:04:08 395

395 作者:泛林集團Sabre 3D產品線資深總監 John Ostrowski 異構集成(HI)已成為封裝技術最新的轉折點 l對系統級封裝(SiP)的需求將基板設計推向更小的特征(類似于扇出型面板級封裝

2023-04-11 17:46:27 350

350

高性能計算芯片發展需要基于異質異構集成的高性能封裝。同時,Die-to-Die 2.5D/3D封裝是邏輯、模擬射頻、功率、光、傳感器等小芯片形成異質集成的重要途徑。同時,SIP技術發展至今已經形成了更高密度,更高帶寬的連接,從國際學術上來看,高密度SIP技術也是異質異構集成的重要路徑。

2023-04-25 10:44:32 718

718 來源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺積電 3nm(N3E)工藝技術的 Cadence? 16G UCIe? 2.5D 先進封裝 IP 成功流片。該 IP 采用

2023-04-27 16:35:40 452

452

隨著摩爾定律的放緩以及前沿節點復雜性和成本的增加,先進封裝正在成為將多個裸片集成到單個封裝中的關鍵解決方案,并有可能結合成熟和先進的節點。

2023-06-16 17:50:09 340

340

異構集成(Heterogeneousintegration,HI)和系統級芯片(SystemonChip,SoC)是設計和構建硅芯片的兩種方式。異構集成的目的是使用先進封裝技術,通過模塊化方法來應對

2023-01-05 15:44:26 1128

1128

芯片異構集成的概念已經在推動封裝技術的創新。

2023-07-03 10:02:20 1608

1608

異構集成推動面板制程設備(驅動器)的改變

2023-07-10 14:54:30 256

256

隨著每個 OSAT 和代工廠提供自己的技術,支持小芯片和異構結構的 IC 封裝選項也不斷傳播。結果,術語變得相當混亂。值得慶幸的是,這些封裝結構比目前行業中存在的術語簡單得多。

2023-07-29 14:25:28 880

880

BGA和CSP封裝技術詳解

2023-09-20 09:20:14 951

951

關于異構集成和高級封裝的任何討論的一個良好起點是商定的術語。異構集成一詞最常見的用途可能是高帶寬內存 (HBM) 與某種 GPU/NPU/CPU 或所有這些的某種組合的集成。

2023-10-12 17:29:42 703

703

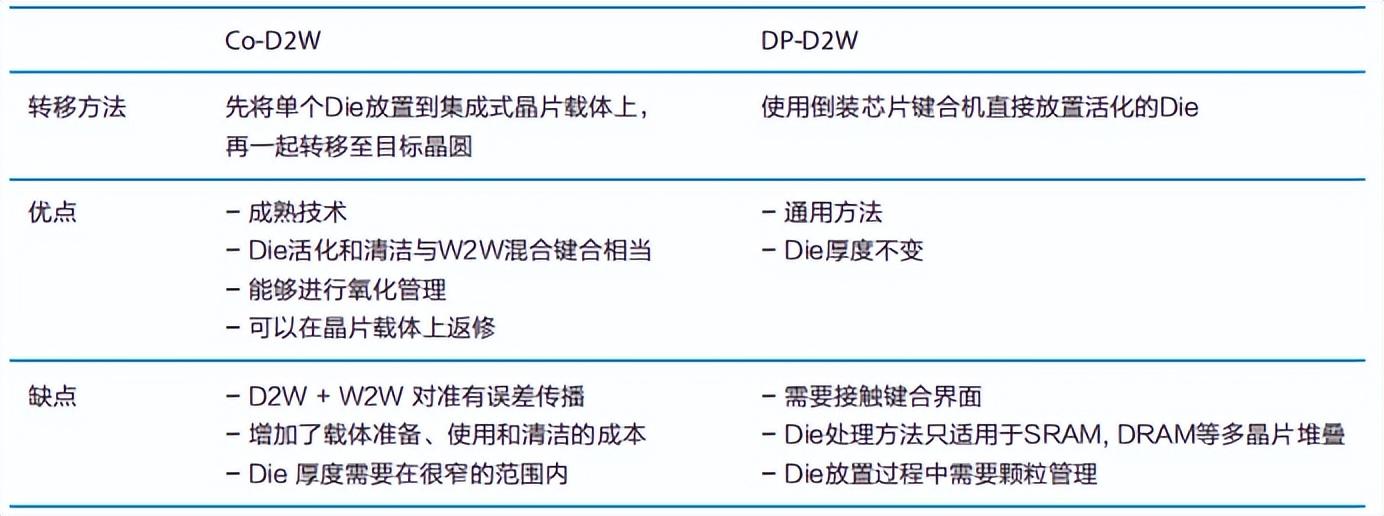

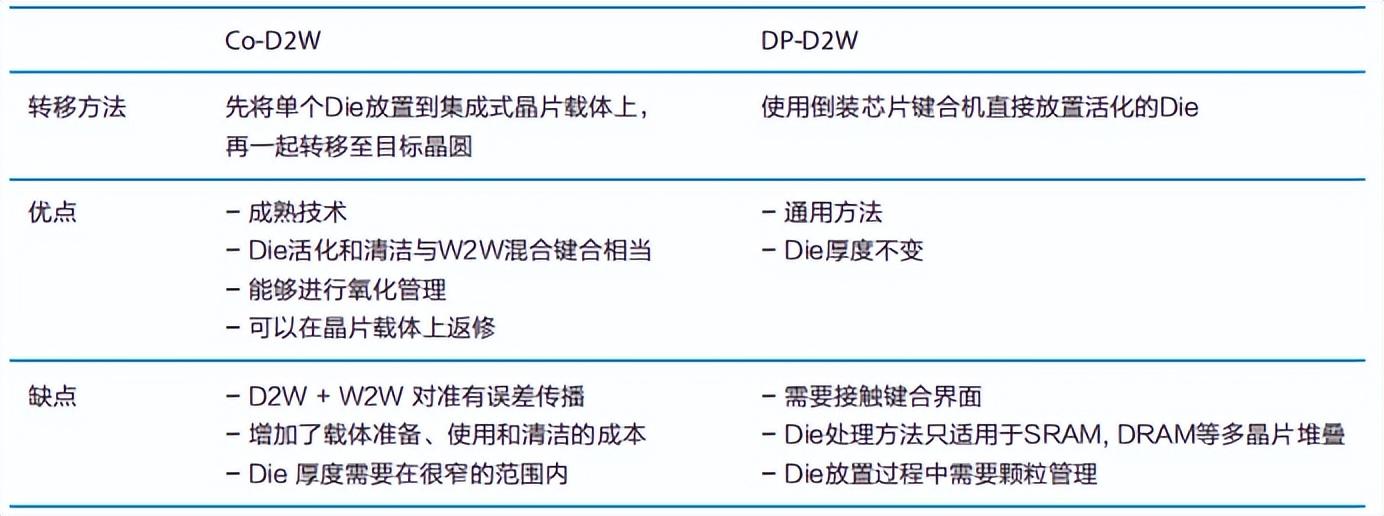

傳統的二維硅片微縮技術達到其成本極限,半導體行業正轉向異構集成技術。異構集成是指不同特征尺寸和材質的多種組件或晶片的制造、組裝和封裝,使其集成于單個器件或封裝之中,以提高新一代半導體器件的性能。 ? 經過集成式晶片到晶圓鍵

2023-10-30 16:07:32 358

358

當芯片變身 3D 系統,3D 異構集成面臨哪些挑戰

2023-11-24 17:51:07 244

244

3D 異構集成與 COTS (商用現成品)小芯片的發展問題

2023-11-27 16:37:16 219

219

異構集成時代半導體封裝技術的價值

2023-11-28 16:14:14 223

223

異構集成 (HI) 與系統級芯片 (SoC) 有何區別?

2023-11-29 15:39:38 440

440

該中心將專注于 3D 異構集成微系統(3DHI)——一種先進的微電子制造方法。3DHI 研究的前提是,通過以不同的方式集成和封裝芯片組件,制造商可以分解內存和處理等功能,從而顯著提高性能。

2023-11-24 17:36:57 989

989 異構集成主要指將多個不同工藝節點單獨制造的芯片封裝到一個封裝內部,以增強功能性和提高性能。

2023-11-27 10:22:53 1828

1828

詳解汽車LED的應用和封裝

2023-12-04 10:04:54 221

221

Universal Chiplet Interconnect Express (UCIe) 是一個開放的行業互連標準,可以實現小芯片之間的封裝級互連,具有高帶寬、低延遲、經濟節能的優點。

2023-12-11 10:37:32 374

374

先進的封裝技術可以將多個半導體芯片和組件集成到高性能的系統中。隨著摩爾定律的縮小趨勢面臨極限,先進封裝為持續改善計算性能、節能和功能提供了一條途徑。但是,與亞洲相比,美國目前在先進封裝技術方面落后

2023-12-14 10:27:14 383

383

華芯邦科技將chiplet技術應用于HIM異構集成模塊中伴隨著集成電路和微電子技術不斷升級,行業也進入了新的發展周期。HIM異構集成模塊化-是華芯邦集團旗下公司深圳市前海孔科微電子有限公司KOOM的主營方向,將PCBA芯片化、異構集成模塊化真正應用于消費類電子產品行業。

2024-01-18 15:20:18 194

194 Cadence 與 Intel 代工廠合作開發并驗證了一項集成的先進封裝流程。該流程能利用嵌入式多晶粒互連橋接(EMIB)技術來應對異構集成多芯粒架構不斷增長的復雜性。

2024-03-11 11:48:05 210

210 UCIe 具有封裝集成不同Die的能力,這些Die可以來自不同的晶圓廠、采用不同的設計和封裝方式。

2024-03-11 14:22:12 47

47

近日,業界領先的電子設計自動化解決方案提供商Cadence宣布與Intel代工廠達成重要合作,共同開發并驗證了一項集成的先進封裝流程。這一流程將利用嵌入式多晶粒互連橋接(EMIB)技術,有效應對異構

2024-03-14 11:33:28 323

323

電子發燒友App

電子發燒友App

評論