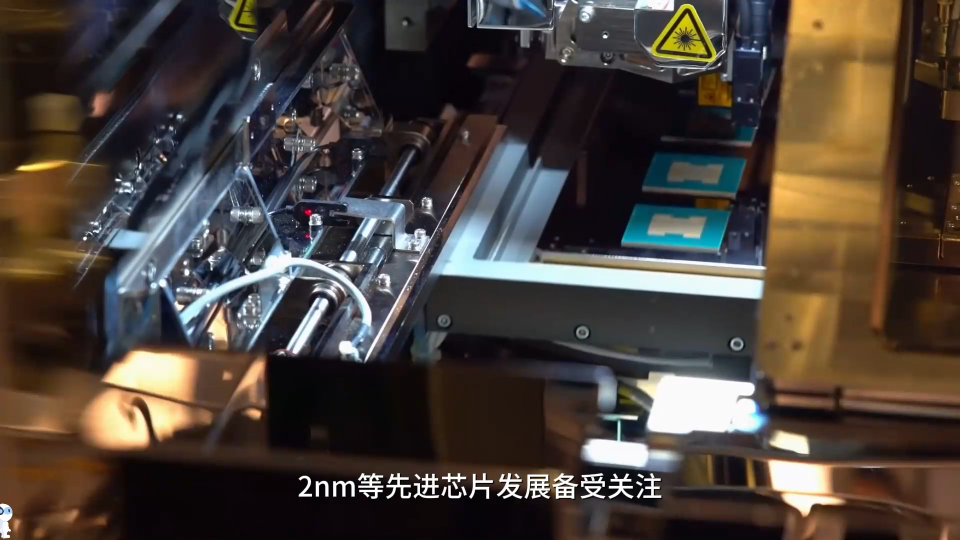

如今,芯片制造技術的競爭愈發激烈。臺積電與英特爾這兩大巨頭在2nm到1nm制程領域競相推出更先進的制程工藝,力圖搶占市場先機。

在這場先進制程的對決中,你是更為信任臺積電?還是更加看好英特爾?

在技術方面,臺積電以其先進的制程工藝聞名于世。從7nm到3nm,臺積電始終保持領先地位,不斷刷新半導體工藝的極限。而英特爾雖然此前一度在制程技術上領先,但在10nm工藝節點上遭遇了多次延期,之后多年的工藝制程一直相對落后。

在此背景下,不少人認為,迎戰臺積電是英特爾的激進之舉。那么英特爾為什么敢于迎戰臺積電呢?這兩大廠商背后的推動力量又有哪些?

在了解這些因素之前需要了解一下這些年來,臺積電與英特爾的競爭歷史。

01臺積電與英特爾的競爭歷史

在PC時代,英特爾毫無疑問是行業霸主,坐擁個人電腦和服務器的CPU市場。英特爾的商業模式是把芯片設計和制造牢牢捆綁在一起,設計部門不斷研發迭代,設計出更新、更快的CPU,制造部門則投入巨額資金,生產出一代又一代的新產品。

在過去的二十多年里,英特爾處理器緊扣“摩爾定律”,從45nm、到32nm、再到22nm,一路都是水到渠成。

在14nm工藝節點之前,英特爾一直保持領先。

臺積電與英特爾的IDM模式不同,其商業定位從一開始就很明確:只做下游的制造,不和客戶在芯片設計上競爭。在臺積電創辦的二十余年里,一度都是以英特爾“小弟”的角色存在。

憑借持續的創新和技術積累,臺積電吸引了蘋果的注意。從2014年開始,自研芯片的蘋果開始將芯片代工訂單交給臺積電,收獲了蘋果這個大客戶后,臺積電不但獲得了技術快速進步的機會,還收獲了今后十年的業務增長。此后,臺積電的訂單紛至沓來,高通、英偉達、AMD等幾乎所有芯片設計巨頭都開始和臺積電合作。臺積電也逐漸有了與英特爾分庭抗禮的實力。

直至10nm,英特爾受到良率問題的限制,其10nm節點沒有選擇EUV,選擇繼續使用ArF DUV,并且沒有按照摩爾定律晶體管密度提高2倍,而是冒險地提高了2.7倍,以及在10nm時英特爾引入了昂貴材料鈷替代銅,鈷的硬度也帶來了各種各樣的問題。

在這個階段,英特爾兩年一次的升級規律被按下暫停鍵,臺積電開始反超英特爾。此后從7nm到3nm,參賽者從三家變成臺積電和三星兩家,甚至于在臺積電先進制程的“誘惑”下,英特爾開始將芯片制造外包給臺積電。

在臺積電與三星之后的比拼中,臺積電以良率優勢斬獲了更多的先進制程訂單。三星也把提升良率列為重中之重,大力發展 3nm。就在臺積電與三星圍繞3nm先進制程激戰正酣之際,沉寂已久的巨頭英特爾悄然卷入這場戰局,并在下一代的制程工藝中向臺積電發起挑戰。

不少人認為,英特爾此舉過于激進,畢竟在先進制程領域它已落后多年。不過英特爾首席執行官帕特·基辛格卻表示,英特爾將在未來幾年擊敗臺積電。

02英特爾反擊的兩大驅動因素

筆者認為基辛格下此決心原因有二,其一為帕特·基辛格對兩家公司當前的差距有著深入分析和更為清楚認知,這讓他能夠更好地評估英特爾和臺積電的優劣勢。

外界宣言臺積電當前的工藝制程已發展至3nm,相比之下,英特爾目前還停留在Intel 4(5nm)制程階段。實則鮮有人知道,如今工藝制程的命名,本身就是一場“游戲”。

在1990年之前,柵極長度的減小幾乎完全線性,每代晶體管的長和寬都是上一代的0.7倍(長度0.7*寬度0.7=0.49),也就是單個晶體管的面積縮小到原來的0.5倍,印證摩爾定律晶體管密度翻倍的描述。比如 180nm》130nm》90nm》65nm》45nm》32nm》22nm ,其中“X”指的就是芯片柵極的長度,也就是MOS 晶體管的源極到漏極的距離。隨著先進制程的數字越小,對應的晶體管密度越大,芯片功耗也就越低,性能則越高。

在之后的技術演進中,制程節點減小速度加快,大約為0.72倍, 并且不再完全線性。場效應晶體管也逐漸脫離原本固定的結構,比如FinFET的空間結構晶體管出現,溝道變成了三維環繞,溝道長度逐漸不能代表工藝的最高精度。7nm、5nm、3nm也不再是溝道長度的代表,它作為一個等效長度,只是一個數字。

此后,臺積電和三星兩大芯片制造商的制程命名規則也在悄然之中發生變化。

英特爾在10nm制程的柵極間距是臺積電和三星在7nm才能達到的技術水平;即使是在邏輯晶體管密度的對比中,英特爾也占據著相當的優勢。10nm時英特爾的邏輯晶體管密度大約1.01億個/mm2,臺積電只有0.48億個/mm2。

值得注意的是,各家在各項指標的計算方式上也存在一些不同。

正如臺積電的研究副總裁的Philip Wong在Hot Chips 31上所說:現在“Xnm”代表的只是技術的迭代,就像汽車型號一樣不具有明確的意義。這也是后來英特爾“芯片新工藝命名新規”,采用Intel 7、Intel 4、Intel 3、Intel 20A、Intel 18A等規則來重新定義芯片制程工藝的原因。芯片的工藝先進性也不能只通過多少納米制程來判斷。

毋庸置疑的是,臺積電在先進制程的步伐確實要更快且更穩,多年來臺積電積累的豐厚訂單,無疑為其提供了巨大的動力和資源,不斷推動其在技術研發和良品率提升方面取得更大的突破。因此想要挑戰臺積電也絕非易事。

其二,不管是技術創新還是產能儲備,英特爾都醞釀已久,英特爾正在靜候時機打響這場反擊戰。接下來看一看,英特爾都準備了哪些“大招”準備迎戰臺積電?

03為了迎戰臺積電,英特爾做了哪些準備?

分拆代工業務

2023年6月,英特爾發布新聞稿宣布組織架構重組,旗下制造業務(包括現有的自用的IDM制造及晶圓代工業務(IFS))未來將獨立運作并產生利潤。而在這種新的“內部代工廠”模式中,英特爾的產品業務部門將以與無晶圓廠半導體公司(Fabless)與外部晶圓代工廠類似的合作方式與公司制造業務集團進行合作。

英特爾分拆代工業務優勢也有二。其一為降本增效。在帕特·基辛格的計劃中分拆之后,2023年可以節省30億美元成本,貢獻6%的利潤。2023 年代工收入將超過200億美元,取代三星,成為全球第二大的代工廠。未來三年減少300億美元的成本,到2025年可以節省80億~100億美元。并且分拆代工業務后,英特爾可以像AMD那樣選擇臺積電等代工廠進行芯片制造,利用代工廠最新的制造技術,提高芯片性能和降低成本。這將使英特爾在市場上更有競爭力,能夠更好地應對AMD等競爭對手的挑戰。

其二,分拆代工業務可以避免與客戶產生競爭,因為英特爾在調查中發現,所有潛在的代工業務大客戶都表示如果需要同英特爾自身競爭代工資源,那么就不會選擇英特爾的代工服務。不僅如此,為打消代工客戶的顧慮,英特爾將設置防火墻區分客戶信息,保護客戶敏感設計數據。如此一來,日后英特爾便有望獲得來自蘋果、英偉達等芯片大廠的先進制程訂單。

引入背面供電技術和RibbonFET

基辛格在2023年12月的采訪中強調了18A工藝(1.8nm)與臺積電的 N2(2nm)節點。18A 和 N2 都將利用 GAA 晶體管 (RibbonFET), 18A將采用BSPND(背面供電網絡),一種可優化功率和時鐘的背面功率傳輸技術。

背面供電技術是一項頗具潛力的創新,英特爾成為首家將其實踐應用的公司,通過將電力傳送到芯片背面而非正面,為熱管理和整體性能提供了優勢。有效的散熱和電力傳輸有助于優化芯片布局和設計,改進功能和熱量分布。

PowerVia 是一項完全革命性的技術。對于大多數讀者來說最好的類比是 EUV。早在 2019 年臺積電就開始在芯片量產中使用 EUV 光刻機,要知道EUV帶來的是全新的挑戰,特別是 EUV 掩模污染和一些抗蝕劑等一系列難以解決的全新問題。而英特爾在2023年量產Intel4時才使用到EUV。

BSPDN 也需要進行類似幅度的流程改進。據悉,臺積電插入 BSPDN 最晚可能會在 2026 年發生。在未來幾年,BSPDN有可能擁有多種設計優勢的機會,英特爾也很有可能領跑PowerVia 。

基辛格指出,英特爾在背面供電技術方面提供了更好的面積效率。這意味著更低的成本、更好的動力輸出和更高的性能。他認為Intel 18A略微領先于N2,因為其晶體管更強大且功率傳輸能力更強。此外,與臺積電相比,英特爾可以提供更有競爭力的價格優勢。

拿下首套 High-NA EUV

近日,英特爾宣布,已經接收市場首套具有0.55數值孔徑(High-NA)的ASML極紫外光刻機,預計在未來兩到三年內用于Intel18A工藝技術之后的制程節點。

相較之下,臺積電則采取更加謹慎的策略,業界預計臺積電可能要到A1.4制程,或者是2030年之后才會采用High-NA EUV光刻機。

根據此前報道,ASML將在2024年生產最多10臺新一代高NA EUV光刻機,其中Intel就預定了多達6臺。業界指出,至少在初期,High-NA EUV 的成本可能高于 Low-NA EUV,這也是臺積電暫時觀望的原因,臺積電更傾向于采用成本更低的成熟技術,以確保產品競爭力。High-NA EUV 需要更高的光源功率才能驅動更精細的曝光尺寸,這會加速投影光學器件和光罩的磨損,抵消了更高產能的優勢。

但是可以確定的是,在高數值孔徑學習方面,英特爾將領先于其競爭對手,這將為其帶來多項優勢。具體來說,由于英特爾很可能是第一家使用高數值孔徑工具啟動大批量生產的公司,因此晶圓廠工具生態系統將不可避免地遵循其要求。上述要求可能會轉化為行業標準,這可能會使英特爾比臺積電和三星更具優勢。

擴產先進封裝

英特爾積極投入先進制程研發之際,在先進封裝領域同步火力全開。

2023年英特爾擴增了其位于馬來西亞的先進封裝產能,目標是在 2025 年將先進封裝的產能較當前提升4倍。外界預期,英特爾結合先進制程與先進封裝能力后,“一條龍生產”實力大增,在晶圓代工領域更具競爭力。

臺積電、三星都在積極布局先進封裝技術。臺積電方面,主打“3D Fabric”先進封裝,包括InFo、CoWoS與SoIC方案;三星也發展I-cube、X-Cube等封裝技術。英特爾的先進封裝技術包括2.5D EMIB與3D Foveros方案。

英特爾并未透露現階段其3D Foveros封裝總產能,僅強調除了在美國俄勒岡州與新墨西哥州之外,在未來的檳城新廠也有相關產能建置,這三個據點的3D封裝產能合計將于2025年時增為目前的四倍。英特爾副總裁Robin Martin表示,未來檳城新廠將會成為英特爾最大的3D Foveros先進封裝據點。

隨著先進制程的演進,小芯片(Chiplet)與異質整合的發展趨勢明確,外界認為,英特爾的2.5D/3D先進封裝布局除了強化自身處理器等產品實力之外,也是其未來爭取更多晶圓代工服務生意的一大賣點。

量產時間更早

按照英特爾新的說法,采用Intel 18A工藝制造的芯片將會在2024年第一季度出現,首批量產產品會在2024年下半年上市。相比之下,臺積電的N2工藝要等到2025年下半年才量產,理論上英特爾在時間上還要領先一年。

面對英特爾的一系列重拳出擊,臺積電又怎么看?

04臺積電多項先發優勢加身

面對英特爾的挑戰,臺積電并未示弱。

臺積電總裁魏哲家表示,根據內部評估,N3P工藝在性能與能效上與Intel 18A技術相當,但上市時間更早,技術上也更為成熟,而且成本還要低得多。同時還重申臺積電的N2工藝優于競爭對手的Intel 18A,2025年推出時將成為半導體行業最先進的技術。

臺積電計劃在2nm制程節點采用GAAFET晶體管,同時將會在 2026 年發布的N2P工藝引進Nanosheet GAA 晶體管并添加背面電源軌技術,制造的過程仍依賴于現有的EUV光刻技術。臺積電認為引入新一代技術后,N2工藝將在功率、性能、面積上全面勝出。

多項技術優勢的積累

在與三星的3nm制程競賽中,臺積電并沒有急于使用GAAFET。憑借工藝領先性和生產良率上的技術優勢和積累完全有實力與采用MBCFET(三星的多橋溝道晶場效應晶體管技術,可歸類為 GAA 技術)架構的三星抗衡。

臺積電的成功源于多項技術優勢的積累。首先是其長期投入獲得領先的技術研發優勢。比如,為配合新制程工藝的良率,臺積電在 Nano-Sheet 結構上面,已經成功生產出了 32 Mb nano-sheet 的 SRAM,在低電壓功耗上面具有明顯優勢;在 2D 材料上,臺積電基于包括硫化鉬和硫化鎢在內的 2D 硫化材料獲得性能非常高的 On-current;在電源管理上,臺積電的研究人員用碳納米管嵌入到一個 CMOS 的設計中,用來替代 Power Gating 的控制電流作用,給未來的進一步微縮提供新的思路。

其次是對工藝流程的優化改造。為了應對摩爾定律接近失效的危機,僅僅從微縮晶體管,提高密度以提升芯片性能的角度正在失效。臺積電推動了多項前段和后段的 3D 封裝技術,來提升芯片性能。比如在芯片制造前段實現的 SOIC 3D 堆疊技術,在后段實現的 CoWoS 和 InFo 的 3D 封裝技術。這些技術在幫助實現晶體管微縮的同時,進一步提高了良率。

首次使用GAA

臺積電在2nm制程中首次使用的 GAAFET技術,區別于 3nm 和 5nm 制程所采用的鰭式場效晶體管(FinFET)架構,GAAFET架構是以環繞閘極(GAA)制程為基礎的架構,可以解決 FinFETch 因為制程微縮而產生的電流控制漏電等物理極限問題。

臺積電被廣泛認為是一個保守但穩健的制程技術開發者,他們傾向于確保新技術的成熟和可靠性,然后再進行部署,而不是急于將新技術推向市場。這種方法可以降低技術失敗的風險,提高其芯片的產量和質量,從而確保客戶的滿意度。例如,三星在2018年開始在其7nm工藝中使用EUV,然而臺積電選擇等待。直到EUV工具的穩定性和成熟性得到確認,以及相關問題得到解決或至少得到確定,才在2019年的N7+工藝中開始使用EUV。

這種謹慎的方法有助于臺積電確保其制程技術的穩定性和可預測性,從而提供高質量的芯片給其客戶。

臺積電本次使用GAA想必是做好了充分的準備和規劃,2nm世代或許有望看到臺積電新一輪爆發。

臺積電N2是N3的延伸

臺積電的2nm技術是3nm技術的延續。一直以來,臺積電堅定地遵循著每一步一個工藝節點的演進策略,穩扎穩打,不斷突破。如今,在邁向2nm制造的征程中,我們可以預見,它將承襲3nm技術的眾多優勢,如同接力賽中的優秀接力手,將前一棒的優秀成果傳遞至下一棒。因此在這場先進制程大戰中,臺積電不管是技術的成熟度還是良率的把控都有著先發的優勢。

客戶的信任

臺積電的成功不僅取決于先進的芯片制造技術,更取決于其只做代工的經營模式、良好的良率以及客戶的信任。在3nm世代,臺積電的報價超過2萬美元,較4nm/5nm代工價格高出4000美元。這種高價讓許多客戶望而生畏,然而蘋果仍然選擇臺積電代工,并占用了所有的產能。盡管三星力圖在晶圓代工領域超越臺積電,但臺積電依然保持著絕對的領先地位,承接了市場上大部分的3nm訂單。如今除了蘋果以外,英偉達、AMD、高通和聯發科等客戶都計劃購買第二代3納米工藝(N3E)產能。

不過需要注意的是,芯片制造商為了掌握更多的話語權想必也不希望芯片制造環節一家獨大,一旦英特爾先進制程芯片的良品率等數據優于或者只是跟臺積電持平,那么蘋果、高通、英偉達等眾多美企大概率會選擇英特爾。畢竟此前英偉達高管就明確表態,愿意考慮讓英特爾代工芯片。

最后英特爾與臺積電之間的制程技術之爭無疑將成為未來幾年半導體產業關注的焦點。從目前披露的時間線來看,針對2nm制程的研發答案將于2025年揭曉。未來技術如何演變?我們拭目以待。同樣我們也期待著在2025年及以后的時間里,看到更多的創新和技術突破。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論