????高性能的PCB設計離不開先進的EDA工具軟件的支撐。Cadence的PSD系列在高速PCB設計方面的強大功能,其前后仿真模塊,確保信號質量,提升產品的一次成功率;其物理、電氣規則的使用,可智能化的實現諸如差分布線、等長控制等技術要求;支持并行設計、縮短研發時間;支持模塊重用、重視技術沉淀,保證了設計質量,提高設計效率。擁有一個高性能的EDA工具軟件,配合經驗豐富的PCB設計工程師,高性能的PCB設計實現也就有了切實的保證。

一、硬件必備基礎

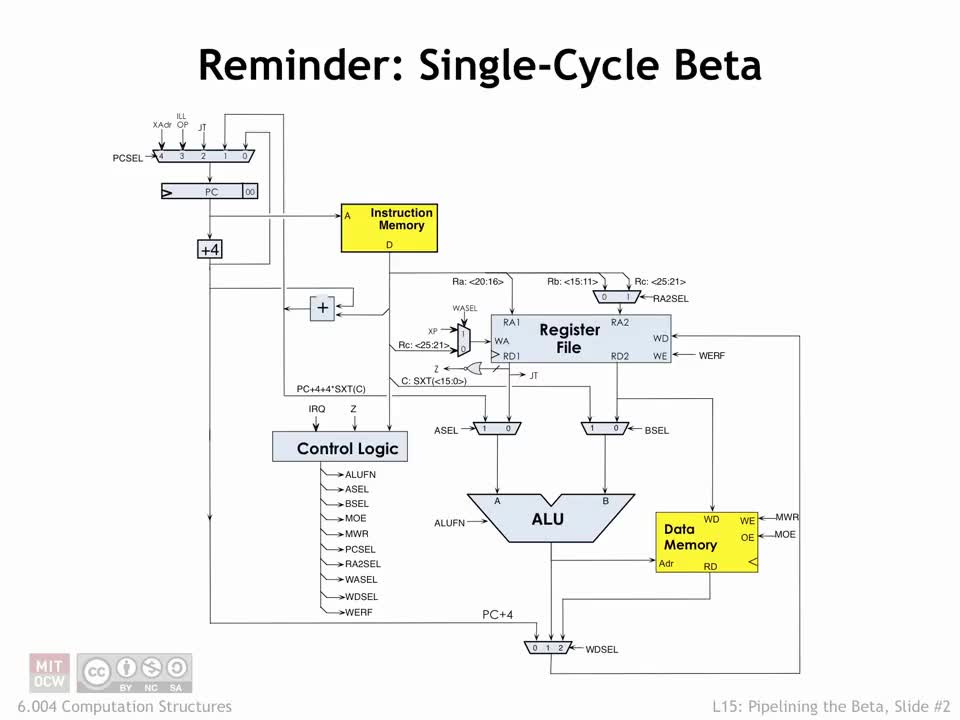

????自從PCB設計進入高速時代,以傳輸線理論為基礎的信號完整性知識勢頭蓋過了硬件基礎知識。有人提出,十年后的硬件設計只有前端和后端。只要有一個系統工程師把他們整合一下就夠了。這很容易讓人懷疑學習硬件基礎知識的必要性。事實上,不管是IC工程師還是PCB工程師,都必須具備諸如R、L、C以及基本的門電路知識。高性能的PCB設計離不開電源基礎知識,少不了FPGA常識。即使以傳輸線理論為基礎的信號完整性分析也是從研究以R、L、C為基礎的微元考慮。PCB設計工程師必須具備基本的電路基本知識,如高頻、低頻、數字電路、微波、電磁場與電磁波等。熟悉并了解所設計產品的基本功能及硬件基礎知識,是完成一個高性能的PCB設計的基本條件。

二、高速的挑戰

????隨著信號速率的不斷提升,信號完整性不斷困擾著研發人員,包括總線驅動能力、信號的反射、串擾、過沖、振蕩、回溝、衰減等;有時也把時序劃歸到信號完整性范圍內。Allegro中基于IBIS模型的仿真模塊Signoise,可以方便地搭建拓撲進行仿真。Allegro的這個仿真工具與布線平臺有良好的接口,在PCB布線完成以后,還可以從PCB板上直接提取布線參數到Signoise平臺中,進行后仿真以驗證布線的效果。仿真提取的布線約束可以直接導入到Allegro的電氣規則管理器中,這個管理器可以方便地對時序要求的等長規則進行約束,在布線時,當長度不符合所規定的規則時,Allegro可以實時進行告警。

三、電源、地噪聲的挑戰

????電源、地平面作為信號線的參考平面、回流通道,電源、地的噪聲會直接串入以其為參考平面的信號。解決電源、地噪聲的問題,不僅僅是考慮供電電源的自身電平穩定問題,還是解決高速信號的可靠性問題的重要因素。高速PCB的電源設計首先要理清電源樹,分析電源通道合理性。

????首先,在大電流的載流能力上,必須在考慮裕量的前提下分配恰當的布線寬度;同時,因為實際布線有電阻,從電源輸出端到實際負載的路線上有壓降,而高速電路器件的電壓特別是core電壓往往很低,壓降對供電效果有直接的影響。電流的載流能力,與線寬、內外層、銅厚度、允許溫升相關。其次,在電源的濾波效果上,需要考慮電源的阻抗。因為電源通道實際上不是一個理想的通道,而是有電阻和阻抗的,高速電路在門電路翻轉時需要瞬間的電源供給,而電流從電源模塊給各個門電路翻轉提供能量是需要各級路徑分配的,需要時間,這可理解為一個分級充電的過程,

四、EMC問題:

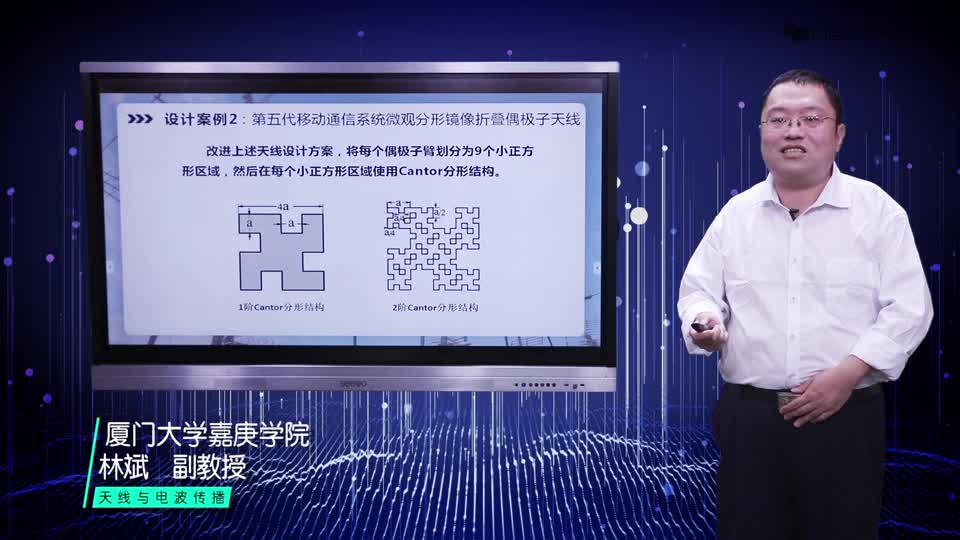

????隨著人們生活水平的提高以及對包括電磁污染在內的環保的關注,EMC問題成為所有電子產品研發中繞不過去的彎。作為一個“Black?Magic”,EMC問題越來越困擾開發人員。EMC要從源頭設計。作為產品EMC的源頭,單板/PCB的EMC性能愈發引起關注,在EMC眾多的指標中,最讓硬件工程師頭痛的是RE指標問題。出于模型的限制,即使業界公認的頂級EMC仿真軟件,至今也不能仿真出和實際測試數據可比擬的數據出來。其只能給出某些特定條件下的簡化了的單輻射源的輻射場分布情況,進而提供設計參考。

五、DFM的挑戰

????解決DFM問題,除了單板工藝工程師制定適合本公司的工藝標準外,需要對PCB設計工程師進行系統、全面的DFM常識培訓,PCB工程師需要不斷了解業界的PCB生產加工能力現狀,結合本公司的實際情況,選擇合適的工藝路線和設計參數。在電氣性能和DFM方面的取舍上,綜合考慮。此外,在PCB的封裝庫上,必須有專職的建庫人員,從源頭上解決DFM問題。Allegro有一個專用的建庫模塊,可以按器件的datasheet方便地設計封裝庫,以及封裝庫的焊盤。良好的封裝設計是DFM設計的基礎。

一、硬件必備基礎

????自從PCB設計進入高速時代,以傳輸線理論為基礎的信號完整性知識勢頭蓋過了硬件基礎知識。有人提出,十年后的硬件設計只有前端和后端。只要有一個系統工程師把他們整合一下就夠了。這很容易讓人懷疑學習硬件基礎知識的必要性。事實上,不管是IC工程師還是PCB工程師,都必須具備諸如R、L、C以及基本的門電路知識。高性能的PCB設計離不開電源基礎知識,少不了FPGA常識。即使以傳輸線理論為基礎的信號完整性分析也是從研究以R、L、C為基礎的微元考慮。PCB設計工程師必須具備基本的電路基本知識,如高頻、低頻、數字電路、微波、電磁場與電磁波等。熟悉并了解所設計產品的基本功能及硬件基礎知識,是完成一個高性能的PCB設計的基本條件。

二、高速的挑戰

????隨著信號速率的不斷提升,信號完整性不斷困擾著研發人員,包括總線驅動能力、信號的反射、串擾、過沖、振蕩、回溝、衰減等;有時也把時序劃歸到信號完整性范圍內。Allegro中基于IBIS模型的仿真模塊Signoise,可以方便地搭建拓撲進行仿真。Allegro的這個仿真工具與布線平臺有良好的接口,在PCB布線完成以后,還可以從PCB板上直接提取布線參數到Signoise平臺中,進行后仿真以驗證布線的效果。仿真提取的布線約束可以直接導入到Allegro的電氣規則管理器中,這個管理器可以方便地對時序要求的等長規則進行約束,在布線時,當長度不符合所規定的規則時,Allegro可以實時進行告警。

三、電源、地噪聲的挑戰

????電源、地平面作為信號線的參考平面、回流通道,電源、地的噪聲會直接串入以其為參考平面的信號。解決電源、地噪聲的問題,不僅僅是考慮供電電源的自身電平穩定問題,還是解決高速信號的可靠性問題的重要因素。高速PCB的電源設計首先要理清電源樹,分析電源通道合理性。

????首先,在大電流的載流能力上,必須在考慮裕量的前提下分配恰當的布線寬度;同時,因為實際布線有電阻,從電源輸出端到實際負載的路線上有壓降,而高速電路器件的電壓特別是core電壓往往很低,壓降對供電效果有直接的影響。電流的載流能力,與線寬、內外層、銅厚度、允許溫升相關。其次,在電源的濾波效果上,需要考慮電源的阻抗。因為電源通道實際上不是一個理想的通道,而是有電阻和阻抗的,高速電路在門電路翻轉時需要瞬間的電源供給,而電流從電源模塊給各個門電路翻轉提供能量是需要各級路徑分配的,需要時間,這可理解為一個分級充電的過程,

四、EMC問題:

????隨著人們生活水平的提高以及對包括電磁污染在內的環保的關注,EMC問題成為所有電子產品研發中繞不過去的彎。作為一個“Black?Magic”,EMC問題越來越困擾開發人員。EMC要從源頭設計。作為產品EMC的源頭,單板/PCB的EMC性能愈發引起關注,在EMC眾多的指標中,最讓硬件工程師頭痛的是RE指標問題。出于模型的限制,即使業界公認的頂級EMC仿真軟件,至今也不能仿真出和實際測試數據可比擬的數據出來。其只能給出某些特定條件下的簡化了的單輻射源的輻射場分布情況,進而提供設計參考。

五、DFM的挑戰

????解決DFM問題,除了單板工藝工程師制定適合本公司的工藝標準外,需要對PCB設計工程師進行系統、全面的DFM常識培訓,PCB工程師需要不斷了解業界的PCB生產加工能力現狀,結合本公司的實際情況,選擇合適的工藝路線和設計參數。在電氣性能和DFM方面的取舍上,綜合考慮。此外,在PCB的封裝庫上,必須有專職的建庫人員,從源頭上解決DFM問題。Allegro有一個專用的建庫模塊,可以按器件的datasheet方便地設計封裝庫,以及封裝庫的焊盤。良好的封裝設計是DFM設計的基礎。

電子發燒友App

電子發燒友App

評論