思維再縝密的程序員也不可能編寫完全無缺陷的C語言程序,測試的目的正是盡可能多的發現這些缺陷并改正。這里說的測試,是指程序員的自測試。前期的自測試能夠更早的發現錯誤,相應的修復成本也會很低,如果你不徹底測試自己的代碼,恐怕你開發的就不只是代碼,可能還會聲名狼藉。

2023-09-19 16:24:41 313

313

的測試設計顯得尤為重要。對于單片或者數量很小的幾片嵌入式SRAM,常用的測試方法是通過存儲器內建自測試MBIST來完成,實現時只需要通過EDA軟件選取相應的算法,并給每片SRAM生成MBIST控制邏輯

2019-10-25 06:28:55

和應用可靠性所要求的測試水平之間存在著一個非常大的差距。這通常意味著板級ESD元件(如多層壓敏電阻、聚合物ESD抑制器和硅保護陣列)必須填補這一差距。要注意的一點是,這些技術的ESD保護性

2019-05-22 05:01:12

設計技術,按照該準則設計即可保證模塊的測試性要求 :(1)在模塊連接器上可以存取所有BIT的控制和狀態信號,從而可使 ATE直接與BIT電路相連;(2)在模塊內裝入完整的 BIT 功能和機內檢測設備

2018-01-11 11:16:01

電路在線測試技術的原理是什么?測試儀由那幾部分構成?

2021-04-25 06:50:44

從根本上講,市場是電路板級仿真的強勁動力。在激烈競爭的電子行業,快速地將產品投入市場至關重要,傳統的PCB設計方法要先設計原理圖,然后放置元器件和走線,最后采用一系列原型機反復驗證/測試。修改

2018-08-24 16:48:08

電路板級的EMC設計(3) PCB布線技術文章目錄電路板級的EMC設計(3) PCB布線技術文檔簡介第三部分:印制電路板的布線技術1.PCB基本特性2.分割3.局部電源和IC間的去耦4.基準面的射頻

2021-11-12 08:43:48

電路板改板設計中的可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即:麥|斯

2013-10-09 10:57:40

電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即: 1 檢測產品是否符合技術

2018-09-14 16:25:59

本帖最后由 gk320830 于 2015-3-4 13:43 編輯

電路板設計可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單

2013-10-08 11:26:12

本帖最后由 gk320830 于 2015-3-7 13:19 編輯

電路板設計可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單

2013-10-16 11:41:06

電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即: 1 檢測產品是否符合技術

2018-11-27 10:01:40

如題目,電路板信號經過一級三極管,兩級運放放大,電路板不動的時候,電路正常工作;電路板震動的時候,電路自動產生干擾信號,干擾信號波形與振鈴波形類似,震動停止則干擾波形消失。第一次遇到這種問題,上論壇來請教下大家。

2019-05-13 03:25:58

AMBA測試接口控制器(TIC)是一個ASB總線主設備,它接受來自外部測試總線(32位外部數據總線,如果可用)的測試向量,并啟動總線傳輸。

TIC鎖存來自測試總線的地址向量并驅動ASB地址總線

2023-08-22 08:10:20

系統外部的一個模塊,它驅動測試接口線以訪問ASB總線,然后施加來自測試輸入文件的測試矢量(參見圖1-1)。

此測試輸入文件是運行用TICTalk命令語言編寫的C程序的輸出。

2023-08-21 06:43:36

自己做的板子,現在用F28069調試CAN通信,應用controlsuite例程自測試功能,可以運行,收發正常,將自測試改成正常模式,就無法正常工作

2018-09-07 11:24:11

法是一種針對時序電路芯片的DFT方案.其基本原理是時序電路可以模型化為一個組合電路網絡和帶觸發器(Flip-Flop,簡稱FF)的時序電路網絡的反饋。內建自測試 內建自測試(BIST)設計技術通過在

2011-12-15 09:35:34

8章中提到的寄存器都沒有引用這個自測試位。能否指出這個自測試位在哪個寄存器中。#lsm330dlc自檢以上來自于谷歌翻譯以下為原文 Hello, For a project we

2019-02-20 06:41:24

應用程序: 此示例代碼是MA35D1系列微處理器的實時處理器( RTP) 的自測試庫。 此庫執行芯片的自測試功能, 以滿足市場要求的安全要求。 當芯片出現錯誤時, 可以實時檢測, 系統可以保持功能

2023-08-29 07:04:24

打開MAX中仿真采集板的測試面板出現錯誤提示“經自測,驅動程序與通訊失敗”,重置MAX和重裝labview和DAQmx還是解決不了,該怎么處理

2016-11-03 10:50:00

到電路板和我的電腦,并將以太網接口IP設置為192.168.1.100步驟2:設置視頻(DVI或VGA)連接 - 使用DVI到VGA適配器將vga電纜連接到顯示器和電路板步驟3:以太網連接的跳線 - 已

2019-09-18 10:42:00

測試點應均勻布在插件板上 每個節點至少有一個測試點(100%通道) 備用或不用的門電路都有測試點 供電電源的多外測試點分布在不同位置 元件標志 標志文字同一方向 型號、版本

2018-11-23 17:07:53

達到測試目的。基于以上原因,這種測試方法正逐漸被掃描測試和內建自測試技術(BIST)所取代。2.掃描技術印制電路中一般都包括了時序邏輯和組合邏輯兩部分。組合邏輯使現有測試技術能較好地測試生成;而時序

2018-09-19 16:17:24

本帖最后由 大彭 于 2014-11-20 10:35 編輯

?PCB設計常用板級信號完整性分析模型為了進行電路模擬,必須先建立元器件的模型,也就是對于電路模擬程序所支持的各種元器件,在

2014-11-20 10:31:44

邊界掃描和集成自測試技術基礎上的測試戰略肯定會增加費用。開發工程師必然要在電路中使用的邊界掃描元件(IEEE-1149.1-標準),并且要設法使相應的具體的測試引線腳可以接觸(如測試數據輸入-TDI

2014-11-19 11:47:21

STC8951單片機不斷電下載的方法(親自測試過)對于STC89C51系列單片機如果要下載程序,我們需要先斷電,點擊下載,再給單片機上電這時,他就會自動下載程序。這是因為單片機在冷啟動時,首先執行

2013-04-30 01:04:20

dft可測試性設計,前言可測試性設計方法之一:掃描設計方法可測試性設計方法之二:標準IEEE測試訪問方法可測試性設計方法之三:邏輯內建自測試可測試性設計方法之四:通過MBIST測試寄存器總結...

2021-07-22 09:10:42

msp430x14x用TINERB產生6路PWM信號,親自測試可行

2016-07-19 21:52:22

設計了一種多通道頻率測量系統。系統由模擬開關、信號調理電路、FPGA、總線驅動電路構成,實現對頻率信號的分壓、放大、濾波、比較、測量,具備回路自測試功能,可與主設備進行數據交互,具有精度高、可擴展

2019-06-27 07:23:11

目前隨著使用大規模集成電路的產品不斷出現,相應的PCB的安裝和測試工作已越來越困難。雖然印制電路板的測試仍然使用在線測試技術這一傳統方法,但是這種方法由于芯片的小型化及封裝而變得問題越來越多

2018-09-10 16:50:00

大家,可以幫我推薦一下不同速率電路板級間的連接器嗎?具體要求是如下這樣:實現兩塊電路板的連接,它們分別含有一塊FPGA的電路板的,其中包括低速的控制信號的傳播和高速數據信號的傳輸,低速信號至少有八個,高速信號有上百個,請各位大神推薦一下。如果能介紹下接口選型的經驗就更好了。

2017-09-23 21:45:54

我修改了add.S文件,想讓make run_test SIM=iverilog后出現file.可是編譯不了,add.S文件也沒顯示更新。

可是我在測試自測試用例的時候,make compile

2023-08-12 06:50:38

技術的主要缺點是通孔要占用所有層的珍貴空間,而不考慮該層是否需要進行電氣連接。 2 埋孔 埋孔是連接多基板的兩層或更多層的鍍通孔,埋孔處于電路板的內層結構中,不出現在電路板的外表面上。圖2 為具有

2018-11-27 10:03:17

本文介紹了一種基于信號完整性計算機分析的高速數字信號PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設計的解

2018-08-29 16:28:48

環境的多模型機動目標跟蹤算法。仿真結果驗證了該算法跟蹤性能的有效性。 0 引言 隨著信息技術的快速發展和現代軍事及民用需求的不斷提高,對目標跟蹤的精度也相應地提出了更高的要求。在真實的目標跟蹤系統

2018-12-05 15:16:23

,實際板卡與簡化的板卡仿真模型之間的差異將對熱仿真結果帶來不可預知的影響?板級熱仿真技術仍存在諸多問題: 1) 板卡芯片熱輸入數據不統一?不確定?不準確,沒有科學有效的測量計算方法? 2) 板卡EDA

2018-09-26 16:22:17

掃描技術應用在電路板快速測試系統中,設計了一套具有自 主知識產權的邊界掃描測試系統,并對系統的故障分析策略進行了討論研究,提出對周期信 號采用信號統計法和數據分析法的故障分析策略。參考文獻:[1

2018-09-10 16:28:11

個位大佬你們是如何測試STM32中斷搶占的,我的測試步驟如下:第一步、我配置了兩個定時器,定時器2優先級為3,定時器3優先級為4,

第二步、我各自測試都可以發生中斷

第三步、在定時器3中加

2024-04-22 06:31:54

工程師來說,建立在邊界掃描和集成自測試技術基礎上的測試戰略肯定會增加費用。開發工程師必然要在電路中使用的邊界掃描組件( IEEE-1149.1- 標準),并且要設法使相應的具體的測試引線腳可以接觸(如測試

2015-01-14 14:34:27

測試性。對此可使用邊界掃描和集成自測試技術來縮短測試完成時間和提高測試效果。 對于開發工程師和測試工程師來說,建立在邊界掃描和集成自測試技術基礎上的測試戰略肯定會增加費用。開發工程師必然要在電路中使

2017-11-06 09:11:17

能處于插件板的背面? 測試點應均勻布在插件板上? 每個節點至少有一個測試點(100%通道)? 備用或不用的門電路都有測試點? 供電電源的多外測試點分布在不同位置 元件標志 ? 標志文字同一

2017-11-06 10:33:34

放大電路和加法器電路各自測試時都對,但放大器輸出之后接加法器的時候輸出不對!新手求助

2016-04-28 08:41:31

近期安泰維修中心接修到一臺E8267C信號發生器,客戶描述儀器自測試未通過,下面就來看看這臺儀器的損壞原因以及維修過程。故障現象自測試未通過,頻率3.2G以上功率無輸出。檢測過程外觀完好,自檢

2020-09-18 14:23:21

的接口。它們帶有元件編號和序列號數據等等,還包括最近故障檢測日志。PCI-DIO-96 被作為一個使用CPLD、有160 個管腳的DIO,CPLD 將來自測試控制器PC 的I/O 板卡的輸出和輸入進行

2013-10-28 14:41:12

)設備的接口。它們帶有元件編號和序列號數據等等,還包括最近故障檢測日志。PCI-DIO-96 被作為一個使用CPLD、有160 個管腳的DIO,CPLD 將來自測試控制器PC 的I/O 板卡的輸出和輸入

2018-09-10 16:49:58

,同時將調節元器件放置和布線所需要的時間加以計劃,以便調整信號完整性設計的指針。 6 技術選擇 不同的驅動技術適于不同的任務。信號是點對點的還是一點對多抽頭的?信號是從電路板輸出還是留在相同的電路板上

2015-01-07 11:44:45

( 甚至是多板系統 ) ,自動屏蔽 SI 問題并生成精確的“引腳到引腳”延遲參數。只要輸入信號足夠好,仿真結果也會一樣好。這使得器件模型和電路板制造參數的精確性成為決定仿真結果的關鍵因素。很多設計工程師將

2014-11-18 10:20:50

和布線所需要的時間加以計劃,以便調整信號完整性設計的指標。 6、技術選擇 不同的驅動技術適于不同的任務。信號是點對點的還是一點對多抽頭的?信號是從電路板輸出還是

2009-05-24 23:02:49

、未來技術的趨勢 設想系統中所有輸出都可以調整以匹配布線阻抗或者接收電路的負載,這樣的系統測試方便, SI 問題可以通過編程解決,或者按照 IC 特定的工藝分布來調整電路板使 SI 達到要求,這樣

2018-08-23 08:42:59

本帖最后由 一只耳朵怪 于 2018-6-14 10:25 編輯

eCan 自測試模式下可以產生中斷嗎? F2812

2018-06-14 01:20:48

基于DSP的測試技術與傳統的測試技術相比,有哪些優勢?基本的混合信號測試技術包括哪些?采樣和重建在混合信號測試中的應用

2021-04-21 06:41:10

繼電器來選擇所需的測試。圖 1 是整體測試電路。在圖 2 至圖 13 中,信號路徑以紅色顯示,以便與前兩篇文章中所介紹的方法進行比較。圖 1.該電路整合了用于測試運算放大器的自測試電路及雙運算放大器環路

2018-09-07 11:04:41

測試,從而利用JTAG邊界掃描架構測試高速系統級芯片(SoC)的互連上發生的時延破壞。ALT="圖1:信號完整性故障模型。"> 互連中的信號完整性損耗對于數千兆赫茲高度

2009-10-13 17:17:59

一、電路在線測試技術 1、在線測試原理:在線測試的基本原理是測試儀為印制電路板上的被測芯片提供輸入激勵,同時在計算機控制下自動采集記錄被測芯片的輸出響應和狀態值,通過計算機將其記錄的所有狀態值

2018-09-10 16:28:17

高速電路PCB板級設計技巧改進電路設計規程提高可測試性隨著微型化程度不斷提高,元件和布線技術也取得巨大發展,例如BGA外殼封裝的高集成度的微型IC,以及導體之間的絕緣間距縮小到0.5mm,這些僅是

2009-05-16 20:41:11

上,主要應用于集成電路的設計。而MicroSim公司(后來被OrCAD公司兼并,而OrCAD又被Cadence公司兼并)開發的PSPICE運行于PC上,主要應用于PCB板級和系統級的設計。 SPICE

2018-08-31 14:55:27

電工技術(電工學I)典型題解析及自測試題是根據國家教育部(前國家教委)1995年修訂的“高等工業學校電工技術(電工學Ⅰ)課程教學基本要求“編寫的學習指導書,主要內容是

2008-09-20 21:46:12 0

0 近幾年基于預定制模塊IP(Intellectual Property)核的SoC(片上系統)技術得到快速發展,各種功能的IP 核可以集成在一塊芯片上,從而使得SoC 的測試、IP 核的

2009-09-09 08:33:41 24

24 嵌入式存儲器內建自測試的一種新型應用孫華義 鄭學仁 閭曉晨王頌輝吳焯焰 華南理工大學微電子研究所廣州 510640摘要:當今,嵌入式存儲器在SoC 芯片面積中所占的比例越來

2009-12-20 09:26:11 38

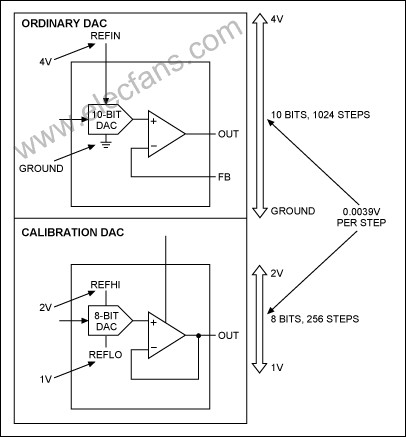

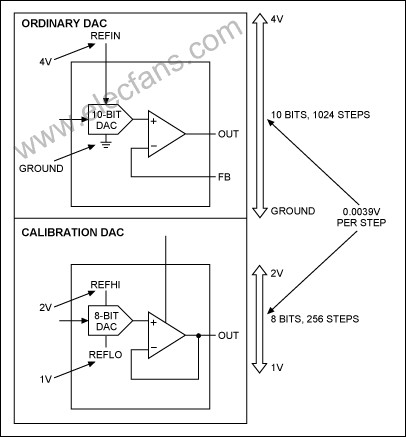

38 本設計指南探討了信號調理、調整和校準電路,用于修正系統誤差,從而以合理的成本確保工業設備安全、精確。校準部分討論了利用最終測試補償元件誤差,通過上電自測試和連

2010-07-30 11:34:32 8

8 本文介紹了一款RISC_CPU的可測性設計,為了提高芯片的可測性,采用了掃描設計和存儲器內建自測試,這些技術的使用為該芯片提供了方便可靠的測試方案。

2010-07-30 17:19:51 20

20 芯片間的互連速率已經達到GHz量級,相比較于低速互連,高速互連的測試遇到了新的挑戰。本文探討了高速互連測試的難點,傳統互連測試方法的不足,進而介紹了互連內建自測試(I

2010-07-31 17:00:16 15

15 內建自測試是一種有效的測試存儲器的方法。分析了NOR型flash存儲器的故障模型和測試存儲器的測試算法,在此基礎上,設計了flash存儲器的內建自測試控制器。控制器采用了一種23

2010-07-31 17:08:54 35

35 隨著超大規模集成電路(VLSI)制造密度的提高.使得電子電路和系統變得日益復雜.也顯著地拉加了模擬和數字集成電路充分測試的難度.另外.市場競爭的壓力對集成電路(Ic)的-惻試

2010-08-06 15:53:29 39

39 介紹了用于IP核測試的內建自測試方法(BIST)和面向測試的IP核設計方法,指出基于IP核的系統芯片(SOC) 的測試、驗證以及相關性測試具有較大難度,傳統的測試和驗證方法均難以滿足

2010-12-13 17:09:11 10

10 在BIST(內建自測試)過程中,線性反饋移位寄存器作為測試矢量生成器,為保障故障覆蓋率,會產生很長的測試矢量,從而消耗了大量功耗。在分析BIST結構和功耗模型的基礎上,針

2010-12-23 15:35:11 0

0

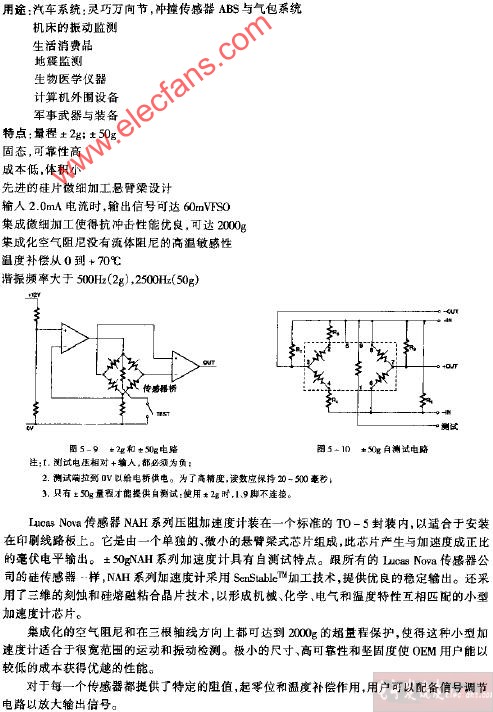

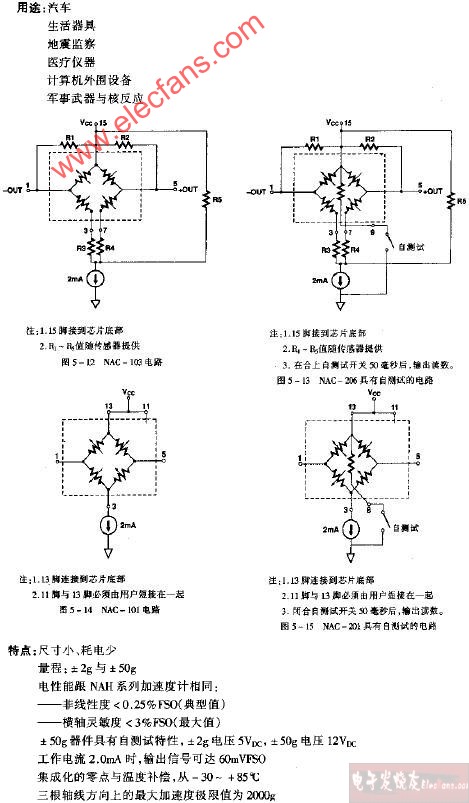

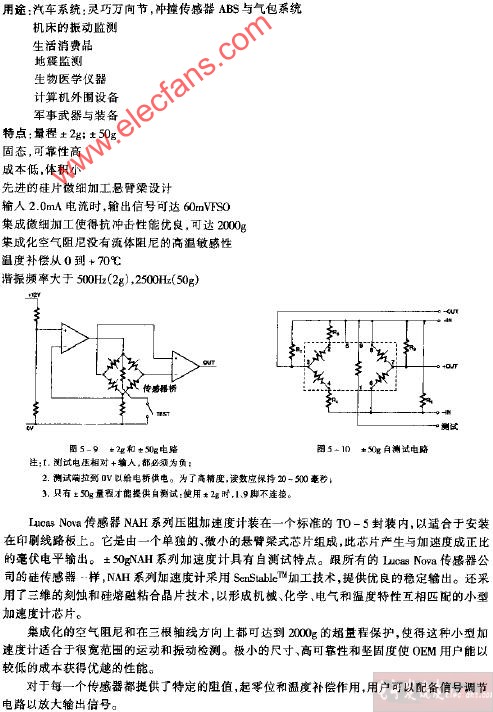

±50g自測試電路圖

2009-07-03 12:03:06 411

411

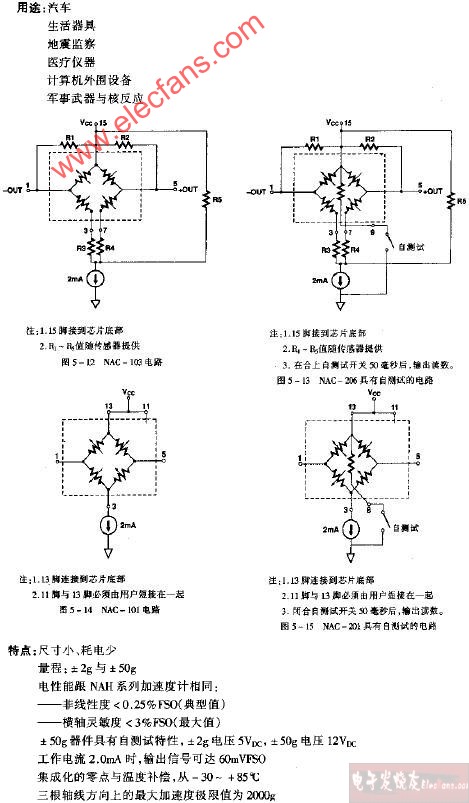

NAC-201具有自測試的電路圖

2009-07-03 13:09:10 409

409

NAC-206具有自測試的電路圖

2009-07-03 13:09:35 478

478

本設計指南探討了信號調理、調整和校準電路,用于修正系統誤差,從而以合理的成本確保工業設備安全、精確。校準部分討論了利用最終測試補償元件誤差,通過上電自測試和連

2010-07-24 12:08:27 626

626 本設計指南探討了信號調理、調整和校準電路,用于修正系統誤差,從而以合理的成本確保工業設備安全、精確。校準部分討論了利用最終測試補償元件誤差,通過上電自測試和連

2010-07-27 18:09:20 693

693

通常我們在設計芯片的同時,可以根據芯片本身的特征,額外地把可測性電路設計(Design For Testability)在芯片里。談到可測性的電路設計,內建自測試(BIST)和基于掃描Scan—Based)的電路設計

2011-06-10 10:13:45 2157

2157

隨著集成電路的規模不斷增大,集成電路的可測性設計正變得越來越重要.綜述了可測性設計方案掃描通路法、內建自測試法和邊界掃描法,并分析比較了這幾種設計方案各自的特點及應

2011-10-28 17:28:51 46

46 在集成電路內建自測試的過程中,電路的測試功耗通常顯著高于正常模式產生的功耗,因此低功耗內建自測試技術已成為當前的一個研究熱點。為了減少被測電路內部節點的開關翻轉活

2012-02-01 14:00:36 21

21 usb口轉串口的驅動,本人親自測試通過,請放心使用

2015-11-10 17:06:56 24

24 本人親自測試的Jlink刷機教程,很有含量哦

2015-11-06 16:56:38 15

15 XDS100V3原理圖,是按照官方的原理圖重新畫的,親自測試通過。

2015-12-02 10:22:11 157

157 溫度控制系統,親自測試,可以使用,十分強大,感興趣的可以看看。

2016-07-22 16:53:46 0

0 一種基于包的邏輯內置自測試電路設計方法

2017-02-07 16:14:56 12

12 在本系列的第 1 部分中,我們為大家介紹了三種運算放大器測試電路:自測試電路、雙運算放大器環路以及三運算放大器環路。這些電路有助于測試失調電壓 (VOS)、共模抑制比 (CMRR)、電源抑制

2017-04-08 06:06:34 4888

4888

TMS570LS系列微控制器與可編程內置自測試(pbist)實現建筑。的pbist架構提供了一種存儲器BIST引擎不同的覆蓋水平在許多嵌入式內存實例中。TMS570LS系列微控制器可分為兩類:130

2018-04-16 16:03:38 12

12 隨著集成電路復雜度越來越高,測試開銷在電路和系統總開銷中所占的比例不斷上升,測試方法的研究顯得非常突出。目前在測試源的劃分上可以采用內建自測試或片外測試。

2019-04-26 09:12:00 1030

1030

仿真結果:為了評價BIC監測儀用于新型并行模擬自測試的可行性,進行了故障仿真。全差分電流傳送器被用作被測器件。在監視通過/失敗輸出(圖2)的同時,將每個典型的MOS晶體管的終端故障(短路和開路)分別

2019-11-26 16:36:30 0

0 VLSI測試技術導論, 可測試性設計, 邏輯與故障模擬,測試生成,邏輯自測試,測試壓縮,邏輯電路故障診斷,存儲器測試與BIST,存儲器診斷與BISR,邊界掃描與SOC測試,納米電路測試技術,復習及習題

2020-10-09 08:00:00 1

1 開關電源(Buck電路)的小信號模型及環路設計(實用電源技術答案)-開關電源(Buck電路)的小信號模型及環路設計???????????

2021-09-18 10:03:12 78

78 糕的是,您可能很晚才發現,而此時糾正該問題已經更難了。 自測試補償 以最簡單的形式看,圖 1 中的自測試電路實際上是一款增益為 1201 的閉環系統。如果將 R1 減小至 5kW,閉環增益就是 301。因此,它具有固有的穩定性,即使采用未

2021-11-23 17:46:33 1648

1648 作者:Martin Rowe — 2011 年 11 月 16 日

在本系列的第 1 部分中,我們為大家介紹了三種運算放大器測試電路:自測試電路、雙運算放大器環路以及三運算放大器環路。這些電路

2021-11-23 17:41:50 1456

1456 LBIST (Logic build-in-self test), 邏輯內建自測試。和MBIST同理,在關鍵邏輯上加上自測試電路,看看邏輯cell有沒有工作正常。BIST總歸會在芯片里加入自測試邏輯,都是成本。

2022-08-29 15:33:30 2266

2266 NMOS管,其電路模型可分為大信號模型和小信號模型。

2022-10-14 13:04:13 5835

5835 UM2986 STM32U5系列IEC 60730自測試庫用戶指南

2022-11-22 08:21:45 0

0 大信號模型和小信號模型是電子工程和通信領域中常用的兩種模型,它們在描述和分析電子電路或系統時具有不同的特點和應用范圍。以下是關于大信號模型和小信號模型區別的介紹。 大信號模型:大信號模型主要用于描述

2023-12-19 11:35:55 3424

3424

電子發燒友App

電子發燒友App

評論