由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。

2023-07-18 09:22:31 875

875

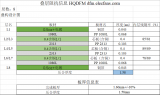

、PCB供應(yīng)商反饋信息等,而最終得出此推薦設(shè)計(jì)。適用于大部分PCB供應(yīng)商的制程工藝標(biāo)準(zhǔn)和具有阻抗控制要求的PCB板設(shè)計(jì)。 一、 雙面板阻抗設(shè)計(jì) 100歐姆差分阻抗推薦設(shè)計(jì)①、包地設(shè)計(jì):線寬、間距 7/5/7 mil地線寬度20mil信號(hào)與地線距離6mil,每400mil內(nèi)加接地過孔;②

2020-11-02 14:05:20 11194

11194 相信大家在接觸高速PCB設(shè)計(jì)的時(shí)候都會(huì)了解到阻抗的一個(gè)概念,那么我們?cè)诟咚?b class="flag-6" style="color: red">PCB設(shè)計(jì)是為什么需要控阻抗呢,哪些信號(hào)需要控阻抗以及不控阻抗對(duì)我們的電路有什么影響呢?

2022-10-18 09:09:22 2947

2947 隨著高速信號(hào)傳輸,對(duì)高速PCB設(shè)計(jì)提出了更高的要求,阻抗控制是高速PCB設(shè)計(jì)常規(guī)設(shè)計(jì),PCB加工十幾道工序會(huì)存在加工誤差,當(dāng)前常規(guī)板廠阻抗控制都是在10%的誤差。理論上,這個(gè)數(shù)值是越小越好

2023-06-25 10:05:15 528

528

可控阻抗是由PCB跡線及其相關(guān)參考平面形成的傳輸線的特性阻抗。當(dāng)高頻信號(hào)在PCB傳輸線上傳播時(shí),它是相關(guān)的。控制阻抗對(duì)于解決信號(hào)完整性問題,即無失真的信號(hào)傳播。

2023-09-28 10:01:01 2107

2107

的電路里,對(duì)交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡(jiǎn)單相加。阻抗的單位是歐姆。 PCB中的阻抗是指電路板上導(dǎo)線、電源、負(fù)載和其他元件之間的電阻抗。PCB阻抗控制是設(shè)計(jì)PCB電路板的重要

2024-01-03 08:40:18 534

534

PCB 阻抗是高頻工作時(shí)電路的電容和電感的組合,雖然也是以Ω為單位測(cè)量,但是與作為直流特性的電阻有些不同,阻抗是一種交流特性,意味著與頻率有關(guān),而電阻則不是。

2024-02-22 10:20:33 546

546

PCB阻抗控制 詳情見附件

2017-11-26 14:13:37

在實(shí)際情況中,需要在數(shù)字邊際速度高于1ns或模擬頻率超過300Mhz時(shí)控制跡線阻抗。PCB 跡線的關(guān)鍵參數(shù)之一是其特性阻抗(即波沿信號(hào)傳輸線路傳送時(shí)電壓與電流的比值)。印制電路板上導(dǎo)線的特性阻抗

2019-05-30 07:18:53

PCB阻抗控制打樣要注意哪些問題?

2023-04-14 15:55:11

PCB阻抗與連接排線的阻抗需要疊加嗎?

2023-04-11 16:17:59

盡可能地減少信號(hào)反射和損失,同時(shí)也可以提高PCB傳輸線的噪聲容限和干擾抑制能力。另外,50Ω阻抗也是一種較為常見的標(biāo)準(zhǔn)化阻抗值,易于采購和成本控制。 總的而言,選擇50Ω阻抗主要是為了確保高速信號(hào)在

2023-04-14 16:41:14

在PCB設(shè)計(jì)中,阻抗通常是指?jìng)鬏斁€的特性阻抗,這是電磁波在導(dǎo)線中傳輸時(shí)的特性阻抗,與導(dǎo)線的幾何形狀、介質(zhì)材料和導(dǎo)線周圍環(huán)境等因素有關(guān)。對(duì)于一般的高速數(shù)字信號(hào)傳輸和RF電路,50Ω是一個(gè)常用的阻抗值

2023-04-11 10:32:34

“coupon”走線的間距不同,會(huì)導(dǎo)致測(cè)試點(diǎn)與走線之間帶來阻抗不連續(xù)。而PCB板內(nèi)的真實(shí)差分走線末端(即芯片的引腳)間距往往是與走線間距相等或者非常相近的。由此會(huì)帶來阻抗測(cè)試結(jié)果的不同。第二,彎曲的走線與理想

2019-05-29 07:49:26

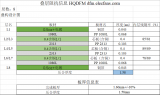

上的導(dǎo)體,其阻抗值應(yīng)控制在某一范圍之內(nèi),稱為“阻抗控制”。影響PCB走線的阻抗的因素主要有銅線的寬度、銅線的厚度、介質(zhì)的介電常數(shù)、介質(zhì)的厚度、焊盤的厚度、地線的路徑、走線周邊的走線等。所以在設(shè)計(jì)PCB

2018-09-18 15:50:04

PCB板阻抗設(shè)計(jì):阻抗線有無參考層阻抗如何變化?生產(chǎn)PCB時(shí)少轉(zhuǎn)彎的阻抗線的阻抗更容易控制穩(wěn)定性?

2023-04-10 17:03:31

摘要: 本文具體分析了PCB板的特性阻抗和特性阻抗的控制辦法。 1、電阻 交流電流流過一個(gè)導(dǎo)體時(shí),所受到的阻力稱為阻抗 (Impedance),符合為Z,單位還是Ω。 此時(shí)的阻力同直流電流所

2018-09-14 16:21:15

本文具體分析了PCB板的特性阻抗和特性阻抗的控制辦法。

2021-04-25 07:27:35

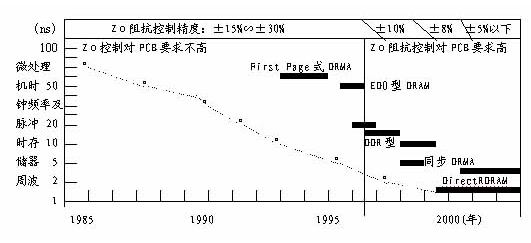

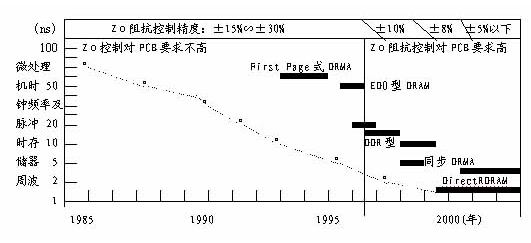

搭載RIA的計(jì)算機(jī)產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的 PCB 板件的特性阻抗控制精度不在局限于原來的±15%或士10%,有的阻抗控制精度要求提高到±8%甚至

2023-09-21 06:14:35

信號(hào)層直接相鄰,以減少串?dāng)_。 主電源盡可能與其對(duì)應(yīng)地相鄰,構(gòu)成平面電容,降低電源平面阻抗。 兼顧層壓結(jié)構(gòu)對(duì)稱,利于制板生產(chǎn)時(shí)的翹曲控制。 以上為層疊設(shè)計(jì)的常規(guī)原則,在實(shí)際開展層疊設(shè)計(jì)時(shí),PCB

2023-04-12 15:12:13

cadence pcb設(shè)計(jì)各層阻抗都是怎么定的呢?為什么每層顯示的阻抗都不一樣?

2016-01-25 22:55:40

為什么說控制阻抗在對(duì)PCB線路板如此重要?

2023-04-14 15:09:13

在能量上的傳輸。3、特性阻抗控制(Z0 )上述此種“訊號(hào)”傳輸時(shí)所受到的阻力,另稱為“特性阻 抗”,代表符號(hào)為Z0。所以,PCB導(dǎo)線上單解決“通”、“斷”和“短路”的問題還 不夠,還要控制

2015-04-10 20:52:45

問題:如何解決PCB技術(shù)在高速設(shè)計(jì)中的特性阻抗問題?

2019-09-06 09:48:13

各位pcb設(shè)計(jì)師你們好請(qǐng)問PCB布線有關(guān)的如何計(jì)算阻抗 收到者求回復(fù)感謝!

2019-09-25 03:18:38

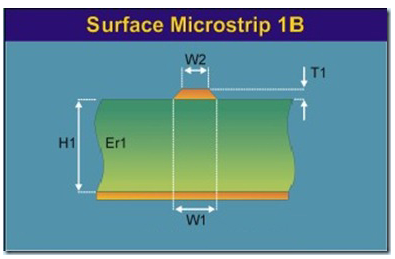

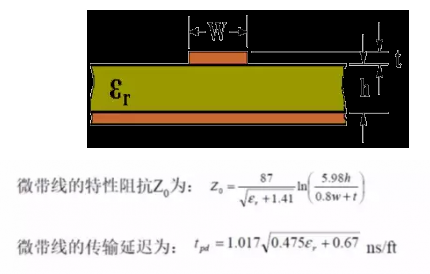

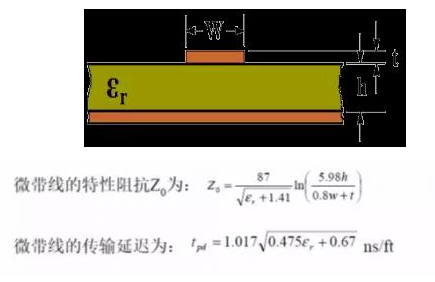

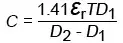

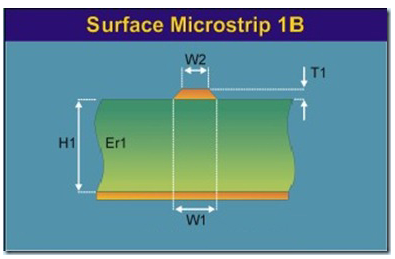

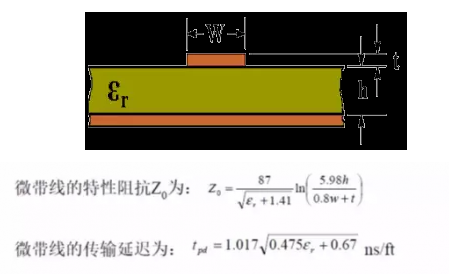

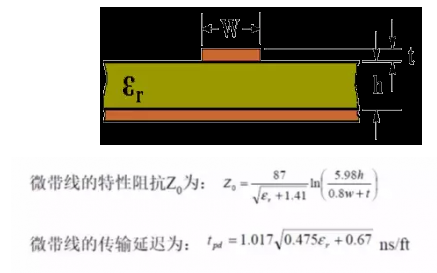

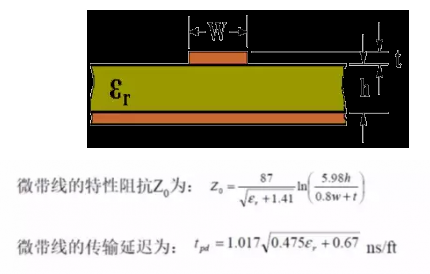

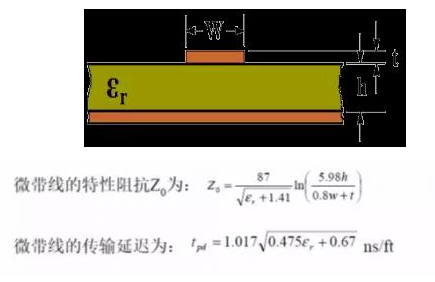

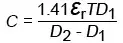

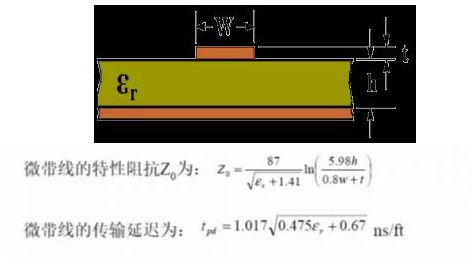

影響PCB特性阻抗的因素:介質(zhì)厚度H、銅的厚度T、走線的寬度W、走線的間距、疊層選取的材質(zhì)的介電常數(shù)Er、阻焊的厚度。 一般來說,介質(zhì)厚度、線距越大阻抗值越大;介電常數(shù)、銅厚、線寬、阻焊厚度

2020-09-07 17:54:12

制作的線路板的銅線),相對(duì)某一參考層(也就是常說的屏蔽層、影射層或參考層),其高頻信號(hào)或電磁波在傳播過程中所受的阻力稱之為特性阻抗,它實(shí)際上是電阻抗、電感抗、電容抗等一個(gè)矢量總和。2、控制PCB

2016-10-10 14:38:27

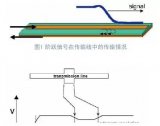

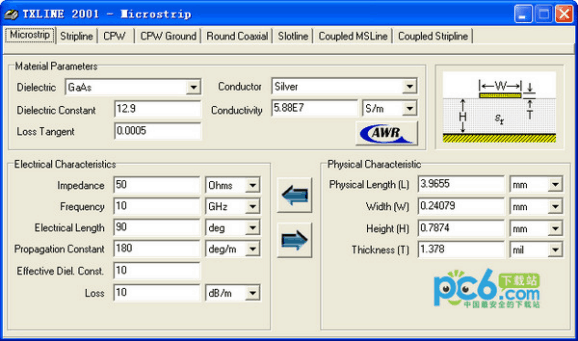

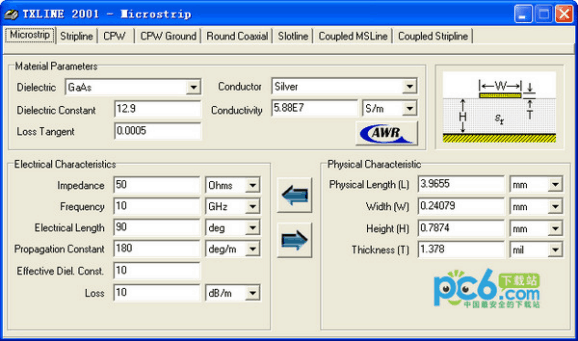

線寬的計(jì)算,然后根據(jù)計(jì)算好的線寬來進(jìn)行布線,即可達(dá)到控制特性阻抗的效果。如圖1-21所示,1.6MM的厚度的PCB板的層壓結(jié)構(gòu)。 圖1-21 1.6MM的厚度的PCB板的層壓結(jié)構(gòu) 第一步,如圖

2020-09-07 17:52:55

PCB阻抗怎么來的?如何計(jì)算?

2021-03-18 06:27:04

應(yīng)該是另作它用,與PCB制板時(shí)的阻抗控制是兩回事。因此在設(shè)計(jì)PCB時(shí),依然要控制阻抗,就像DDR的時(shí)鐘那樣。這么理解對(duì)嗎?

2017-11-20 10:21:31

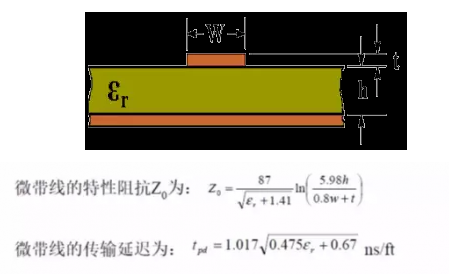

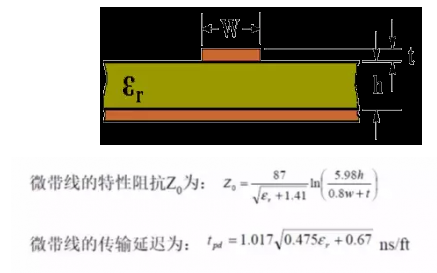

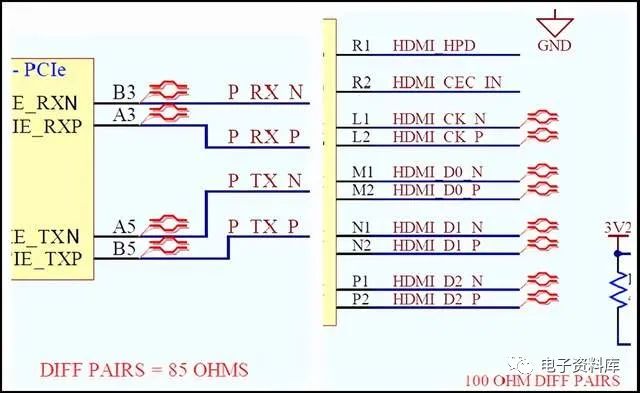

PCB設(shè)計(jì)時(shí),注意控制走線時(shí)的阻抗控制,往往可以做到很好的匹配。 對(duì)于通常的聚酯膠片PCB 來說,傳輸線的長(zhǎng)度和微帶線 Stub 效應(yīng)是需要考慮的, 在本設(shè)計(jì)指南里面,主要是針對(duì) 4 層的 1080+2116 聚酯膠片PCB 進(jìn)行相關(guān)的阻抗匹配控制。

2019-05-17 10:40:14

在正常的PCB設(shè)計(jì)條件下,主要以下幾個(gè)因素由PCB制造對(duì)阻抗產(chǎn)生影響: 1、介

2006-04-16 21:44:51 2179

2179 PCB跡線的阻抗控制簡(jiǎn)介

PCB上的阻抗控制電信和計(jì)算機(jī)設(shè)備操作的速度和切換速率正在不斷增長(zhǎng)。盡管在低頻情況下,這是一個(gè)可以

2009-09-28 14:42:44 1258

1258 隨著PCB 信號(hào)切換速度不斷增長(zhǎng),當(dāng)今的PCB 設(shè)計(jì)廠商需要理解和控制PCB 跡線的阻抗。相應(yīng)于現(xiàn)代數(shù)字電路較短的信號(hào)傳輸時(shí)間和較高的時(shí)鐘速率,PCB 跡線不再是簡(jiǎn)單的連接,而是傳輸線。

2016-03-24 14:48:57 0

0 PCB阻抗設(shè)計(jì)方面的干貨。

2017-01-13 17:13:49 0

0 PCB高級(jí)設(shè)計(jì)之共阻抗及抑制

2017-01-24 16:29:19 0

0 時(shí),若導(dǎo)線的長(zhǎng)度接近信號(hào)波長(zhǎng)的1/7, 此時(shí)的導(dǎo)線便成為信號(hào)傳輸線,一般信號(hào)傳輸線均需做阻抗控制。PCB制作時(shí),依客戶要求決定是否需管控阻抗,若客戶要求某一線寬需做阻抗控制,生產(chǎn)時(shí)則需管控該線寬的阻抗。

2017-07-27 11:20:07 0

0 阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速 PCB 設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量?jī)?yōu)劣。PCB 走線什么時(shí)候需要做阻抗匹配?

2017-08-28 16:33:23 26

26 隨著 PCB 信號(hào)切換速度不斷增長(zhǎng),當(dāng)今的 PCB 設(shè)計(jì)廠商需要理解和控制 PCB 跡線的阻抗。相應(yīng)于現(xiàn)代數(shù)字電路較短的信號(hào)傳輸時(shí)間和較高的時(shí)鐘速率,PCB 跡線不再是簡(jiǎn)單的連接,而是傳輸線

2017-11-26 14:28:01 1036

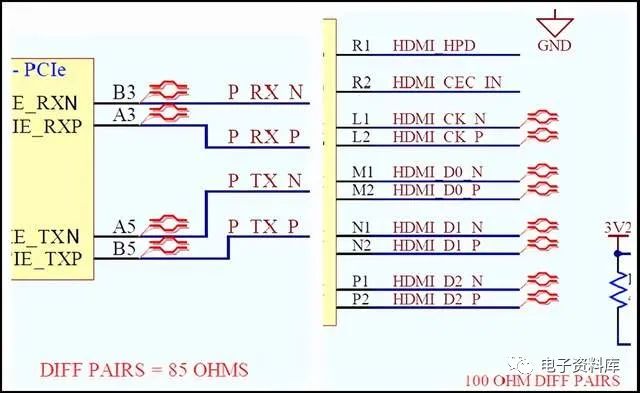

1036 FireWire1394的幾百M(fèi)bps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的幾個(gè)Gbps乃至10Gbps。計(jì)算機(jī)以及通信行業(yè)的PCB客戶對(duì)差分走線的阻抗控制

2017-12-22 13:53:24 7737

7737

PCB阻抗設(shè)計(jì)與阻抗類型圖解

2018-01-20 10:45:33 0

0 本文主要介紹的是阻抗匹配,首先介紹了阻抗匹配條件,其次闡述了如何理解阻抗匹配及常見阻抗匹配的方式,最后介紹了pcb阻抗匹配如何計(jì)算,具體的跟隨小編一起來了解一下。

2018-05-02 17:11:28 38669

38669

PCB設(shè)計(jì)實(shí)現(xiàn),對(duì)PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號(hào)完整性要求去控制走線的阻抗。

2018-10-14 09:28:00 1441

1441 PCB跡線的阻抗將由其感應(yīng)和電容性電感、電阻和電導(dǎo)系數(shù)確定。影響PCB走線的阻抗的因素主要有: 銅線的寬度、銅線的厚度、介質(zhì)的介電常數(shù)、介質(zhì)的厚度、焊盤的厚度、地線的路徑、走線周邊的走線等。PCB阻抗的范圍是 25 至120 歐姆。

2019-08-08 15:23:43 3818

3818

達(dá)到穩(wěn)態(tài),這也是不實(shí)際的因?yàn)橥ǔ_@樣做會(huì)增加PCB板層,成本提高很多。此外縮短走線在某種情況下在物理上也是不可能的。

第三個(gè)方法就是在傳輸線的兩端用等于線的特征阻抗的阻抗端接傳輸線以排除反射。

2019-05-27 14:01:27 1883

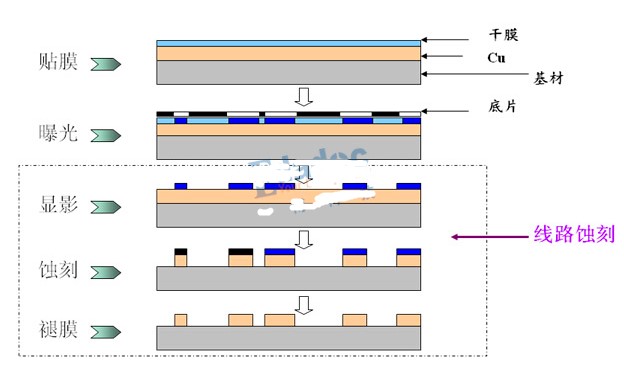

1883 具有高精度控制特性阻抗性的PCB制造,是整體把握的設(shè)計(jì)技術(shù)所保證。而這一系統(tǒng)的整體設(shè)計(jì)技術(shù),主要包括了基板材料的介電特性、部品特性、設(shè)計(jì)方法、PCB制造特性、組裝方法等的技術(shù)。正如圖1所描述那樣,高精度控制特性阻性的PCB有著三大方面(高精度層壓技術(shù)、高精度電鍍技術(shù)、高精度圖形形成技術(shù))的要素技術(shù)。

2019-05-23 14:41:46 518

518 。不僅搭載RIMM的計(jì)算機(jī)產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的PCB板件的特性阻抗控制精度不在局限于原來的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,這對(duì)PCB制造廠來說確實(shí)是很大的挑戰(zhàn)。

2019-05-21 14:47:01 818

818

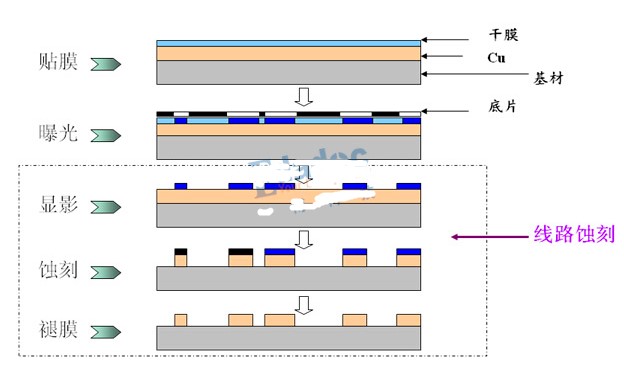

為什么常規(guī)阻抗控制只能是10%的偏差,那一定要了解加工步驟,其中包括層壓、蝕刻及PCB覆銅板材公差及PCB阻焊工序的制作。

2019-04-19 15:48:04 5655

5655

在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?

2019-06-21 17:03:47 6432

6432 我的第一塊PCB遠(yuǎn)離高速數(shù)字設(shè)備。它只是單層PCB上的放大器電路,控制阻抗甚至不是事后的想法。一旦我開始研究需要高采樣率的電光系統(tǒng),控制阻抗始終是一個(gè)關(guān)鍵的設(shè)計(jì)問題。電路板上的受控阻抗是PCB布局問題,我在處理PCB一段時(shí)間后感覺不太舒服。

2019-07-25 09:13:38 1761

1761 阻抗控制PCB 在高頻應(yīng)用中,信號(hào)不會(huì)因?yàn)樗鼈冊(cè)?b class="flag-6" style="color: red">PCB中的路徑而降級(jí)。 在PCB設(shè)計(jì)中通過疊層計(jì)算阻抗控制時(shí)需要注意的四個(gè)問題 在高速PCB設(shè)計(jì)過程中,堆棧設(shè)計(jì)和阻抗計(jì)算是邁向頂端的第一步。阻抗

2019-07-29 14:02:17 2435

2435

阻抗控制線是否會(huì)增加PCB板的成本?是的,會(huì)增加PCB的制造成本設(shè)計(jì)。但是,有3個(gè)主要元素可以控制PCB制造成本。

2019-07-31 11:09:56 2860

2860 、PCB供應(yīng)商反饋信息等,而最終得出此推薦設(shè)計(jì)。適用于大部分PCB供應(yīng)商的制程工藝標(biāo)準(zhǔn)和具有阻抗控制要求的PCB板設(shè)計(jì)。

2019-08-01 17:45:55 0

0 沒有阻抗控制的話,將引發(fā)相當(dāng)大的信號(hào)反射和信號(hào)失真,導(dǎo)致設(shè)計(jì)失敗。

2019-10-14 14:47:58 4073

4073

隨著 PCB 信號(hào)切換速度不斷增長(zhǎng),當(dāng)今的 PCB 設(shè)計(jì)廠商需要理解和控制 PCB 跡線的阻抗。

2019-08-30 08:45:40 3032

3032 阻抗控制最終需要通過PCB設(shè)計(jì)實(shí)現(xiàn),對(duì)PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號(hào)完整性要求去控制走線的阻抗。

2019-09-06 11:52:29 12487

12487

PCB設(shè)計(jì)實(shí)現(xiàn),對(duì)PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號(hào)完整性要求去控制走線的阻抗。

2019-10-04 17:17:00 10393

10393

在阻抗控制的早期,使用了固定增益的PD控制,這種方法實(shí)現(xiàn)簡(jiǎn)單,但在機(jī)器人位形、速度變化時(shí)無法保持理想阻抗。經(jīng)過學(xué)者們的努力,發(fā)展了多種阻抗控制方法,總的看來有兩類實(shí)現(xiàn)阻抗控制的方法,一類是基于動(dòng)力學(xué)模型的阻抗控制方法,另一類是基于位置的阻抗控制方法。

2019-09-25 09:28:58 15980

15980 常見的信號(hào),如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號(hào)等,均需要進(jìn)行阻抗控制。阻抗控制最終需要通過PCB設(shè)計(jì)實(shí)現(xiàn),對(duì)PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號(hào)完整性要求去控制走線的阻抗。

2019-12-31 15:42:08 2238

2238

PCB設(shè)計(jì)為何一般控制50歐姆阻抗?

2020-01-15 16:17:41 9751

9751 PCB線路板阻抗,指的是電阻和對(duì)電抗的參數(shù),對(duì)交流電所起著阻礙作用。在PCB線路板生產(chǎn)中,阻抗處理是必不可少的,PCB線路板為什么要做阻抗?

2020-02-24 11:02:21 4799

4799 本文檔的主要內(nèi)容詳細(xì)介紹的是PCB的結(jié)構(gòu)和加工流程線路阻抗控制線路阻抗計(jì)算的詳細(xì)資料簡(jiǎn)介。

2020-02-28 08:00:00 0

0 沒有阻抗控制的話,將引發(fā)相當(dāng)大的信號(hào)反射和信號(hào)失真,導(dǎo)致設(shè)計(jì)失敗。常見的信號(hào),如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)VDS信號(hào)等,均需要進(jìn)行阻抗控制。阻抗控制最終需要通過PCB

2020-07-14 10:25:00 6

6 的是,阻抗控制使 PCB設(shè)計(jì) 人員和制造商可以管理這種現(xiàn)象。 什么是阻抗? 阻抗測(cè)量交流 電流 過 電路 時(shí)的 電阻 。它是高頻電路的 電容 和感應(yīng)的結(jié)合。像電阻一樣,阻抗的單位是歐姆。但是,由于電阻是直流電的特性,因此請(qǐng)勿混淆這兩個(gè)值。當(dāng)信號(hào)

2020-09-03 19:04:58 6541

6541 如果您是超高速 PCB 或高頻 RF 器件的設(shè)計(jì)師,那么您將在 PCB 設(shè)計(jì)軟件中利用阻抗控制的路由功能。這些工具旨在確保傳輸線的阻抗在其長(zhǎng)度上保持一致,從而允許在兩端進(jìn)行端接以防止反射。一致的阻抗

2020-09-25 18:59:16 1531

1531 在 PCB 設(shè)計(jì)階段要注意阻抗控制,這一點(diǎn)很重要。阻抗控制涉及為 PCB 上的走線和傳輸線指定所需的阻抗。這對(duì)于高速信號(hào)尤其重要,并且可能會(huì)受到您的影響。基材,銅線寬度和布線。即使在布置好電路板

2020-10-09 21:12:57 1297

1297 更高速的動(dòng)作。不僅搭載 RIMM 的計(jì)算機(jī)產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的 PCB 板件的特性阻抗控制精度不在局限于原來的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,這對(duì) PCB 制造廠來說確實(shí)是很大的挑戰(zhàn)。本文主要針對(duì)如何滿足客戶

2023-02-03 14:02:05 794

794 眾所周知,阻抗控制是我們做高速設(shè)計(jì)最基本的原則,各大板廠在PCB加工也會(huì)保證10%左右的阻抗誤差。看似那么輕松的一個(gè)板廠的承諾,要是出現(xiàn)了阻抗在誤差范圍以外的時(shí)候,客戶和板廠到底誰是出問題的一方

2021-03-24 09:48:19 4578

4578 在PCB制造中,跡線代表導(dǎo)體,層壓板代表絕緣體,平面代表屏蔽。因此,印刷電路板的阻抗取決于制造過程中使用的尺寸和材料。

2021-02-27 10:26:01 2180

2180 在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?

2020-11-12 17:09:06 4684

4684 PCB布線短是為了盡量忽略信號(hào)在傳輸過程中的反射,那為什么會(huì)產(chǎn)生反射呢?

實(shí)際上反射的原因是互連線中阻抗發(fā)生了突然變化,那什么叫做阻抗,影響阻抗的因素又是什么呢?

通俗來講:傳輸線上某一點(diǎn)處的電壓與電流的比值表示在這個(gè)位置信號(hào)感受到的阻抗。

2021-01-05 17:02:00 35

35 為了很好地對(duì)PCB進(jìn)行阻抗控制,首先要了解PCB的結(jié)構(gòu)。

2021-03-22 14:30:38 0

0 在 STM32 無線系列產(chǎn)品的 PCB 設(shè)計(jì)中,需要對(duì)射頻部分電路進(jìn)行阻抗控制,良好的阻抗控制可以減少信號(hào)衰減、反射和 EMC 輻射。本篇 LAT 主要介紹印制電路板(PCB)上射頻走線阻抗仿真計(jì)算

2022-06-16 16:36:21 5063

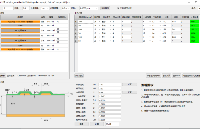

5063 單面PCB,沒有地平面,采用雙側(cè)都有地線的共面波導(dǎo)結(jié)構(gòu),就能實(shí)現(xiàn)布線阻抗控制:

2022-08-12 14:58:43 1347

1347 、PCB供應(yīng)商反饋信息等,而最終得出此推薦設(shè)計(jì)。適用于大部分PCB供應(yīng)商的制程工藝標(biāo)準(zhǔn)和具有阻抗控制要求的PCB板設(shè)計(jì)。

2022-10-12 10:23:17 5071

5071 隨著高速信號(hào)傳輸,對(duì)高速 PCB設(shè)計(jì)提出了更高的要求,阻抗控制是高速PCB設(shè)計(jì)常規(guī)設(shè)計(jì),PCB加工十幾道工序會(huì)存在加工誤差,當(dāng)前常規(guī)板廠阻抗控制都是在10%的誤差。理論上,這個(gè)數(shù)值是越小越好

2023-06-22 08:10:02 486

486

決于選擇的PCB疊層結(jié)構(gòu)。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 PCB疊層設(shè)計(jì) “ ?層的定義設(shè)計(jì)原則? 1、主芯片相臨層

2023-07-19 07:45:02 543

543 決于選擇的PCB疊層結(jié)構(gòu)。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 一、PCB疊層設(shè)計(jì) 層的定義設(shè)計(jì)原則: 1)主芯片相臨層

2023-08-01 07:45:01 1760

1760

阻抗控制pcb

2023-09-18 10:40:37 596

596 通孔的阻抗控制對(duì)PCB信號(hào)完整性會(huì)觸發(fā)什么樣的影響?

2023-10-17 11:56:11 254

254

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)阻抗不連續(xù)怎么辦?PCB設(shè)計(jì)阻抗不連續(xù)問題的解決方法。大家都知道PCB設(shè)計(jì)阻抗要連續(xù)。但是PCB設(shè)計(jì)也總有阻抗不能連續(xù)的時(shí)候。怎么辦?下面深圳PCBA

2023-09-22 09:32:05 634

634

從理論到實(shí)踐之pcb阻抗控制表的使用

2023-09-26 10:34:15 324

324 電路板中的PCB阻抗CBA

2023-10-13 11:15:19 624

624 什么是阻抗匹配?高速PCB設(shè)計(jì)為什么要控制阻抗匹配? 阻抗匹配是指在電路傳輸信號(hào)時(shí),控制電路中信號(hào)源、傳輸線和負(fù)載之間的阻抗相等的過程,從而確保信號(hào)的完整性和可靠性。在高速PCB設(shè)計(jì)中,阻抗

2023-10-30 10:03:25 924

924 PCB阻抗設(shè)計(jì)及計(jì)算簡(jiǎn)介

2022-12-30 09:20:41 11

11 沒有阻抗控制的話,將引發(fā)相當(dāng)大的信號(hào)反射和信號(hào)失真,導(dǎo)致設(shè)計(jì)失敗。常見的信號(hào),如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號(hào)等,均需要進(jìn)行阻抗控制。

2023-12-18 15:52:33 142

142

pcb電路板阻抗設(shè)計(jì),確保最佳性能

2023-12-28 10:27:22 246

246 里,對(duì)交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡(jiǎn)單相加。阻抗的單位是歐姆。 PCB中的阻抗是指電路板上導(dǎo)線、電源、負(fù)載和其他元件之間的電阻抗。PCB阻抗控制是設(shè)計(jì)PCB電路板的重要環(huán)節(jié),以

2024-01-05 08:45:02 219

219

所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡(jiǎn)單相加。阻抗的單位是歐姆。PCB中的阻抗是指電路板上導(dǎo)線、電源、負(fù)載和其他元件之間的

2024-01-05 10:44:00 308

308

pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷電路板)設(shè)計(jì)和制造過程中,通過優(yōu)化電氣特性和信號(hào)完整性,確保設(shè)計(jì)滿足特定的阻抗要求。在高速數(shù)字和模擬電路中,阻抗控制

2024-01-17 16:38:04 722

722 一站式PCBA智造廠家今天為大家講講如何解決pcb設(shè)計(jì)阻抗不連續(xù)的問題?解決PCB設(shè)計(jì)中的阻抗不連續(xù)的方法。當(dāng)涉及到PCB(Printed Circuit Board)設(shè)計(jì)時(shí),阻抗一直是一個(gè)非常重要

2024-03-21 09:32:59 89

89

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論