在網絡通訊領域,ATM交換機、核心路由器、千兆以太網以及各種網關設備中,系統數據速率、時鐘速率不斷提高,相應處理器的工作頻率也越來越高;數據、語音、圖像的傳輸速度已經遠遠高于500Mbps,數百兆乃至數吉的背板也越來越普遍。數字系統速度的提高意味著信號的升降時間盡可能短,由數字信號頻率和邊沿速率提高而產生的一系列高速設計問題也變得越來越突出。當信號的互連延遲大于邊沿信號翻轉時間的20%時,板上的信號導線就會呈現出傳輸線效應,這樣的設計就成為高速設計。高速問題的出現給硬件設計帶來了更大的挑戰,有許多從邏輯角度看來正確的設計,如果在實際PCB設計中處理不當就會導致整個設計失敗,這種情形在日益追求高速的網絡通信領域更加明顯。專家預測,在未來的硬件電路設計開銷方面,邏輯功能設計的開銷將大為縮減,而與高速設計相關的開銷將占總開銷的80%甚至更多。高速問題已成為系統設計能否成功的重要因素之一。

因高速問題產生的信號過沖、下沖、反射、振鈴、串擾等將嚴重影響系統的正常時序,系統時序余量的減少迫使人們關注影響數字波形時序和質量的各種現象。由于速度的提高使時序變得苛刻時,無論事先對系統原理理解得多么透徹,任何忽略和簡化都可能給系統帶來嚴重的后果。在高速設計中,時序問題的影響更為關鍵,本文將專門討論高速設計中的時序分析及其仿真策略。

1 公共時鐘同步的時序分析及仿真

在高速數字電路中,數據的傳輸一般都通過時鐘對數據信號進行有序的收發控制。芯片只能按規定的時序發送和接收數據,過長的信號延遲或信號延時匹配不當都可能導致信號時序的違背和功能混亂。在低速系統中,互連延遲和振鈴等現象都可忽略不計,因為在這種低速系統中信號有足夠的時間達到穩定狀態。但在高速系統中,邊沿速率加快、系統時鐘速率上升,信號在器件之間的傳輸時間以及同步準備時間都縮短,傳輸線上的等效電容、電感也會對信號的數字轉換產生延遲和畸變,再加上信號延時不匹配等因素,都會影響芯片的建立和保持時間,導致芯片無法正確收發數據、系統無法正常工作。

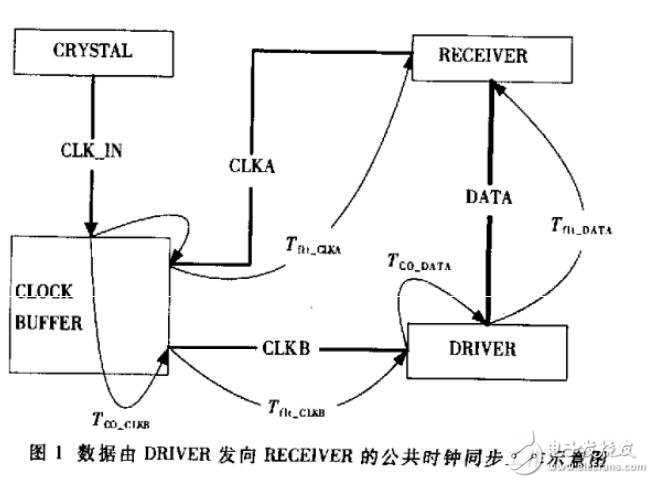

所謂公共時鐘同步,是指在數據的傳輸過程中,總線上的驅動端和接收端共享同一個時鐘源,在同一個時鐘緩沖器(CLOCK BUFFER)發出同相時鐘的作用下,完成數據的發送和接收。圖1所示為一個典型的公共時鐘同步數據收發工作示意圖。圖1中,晶振CRYSTAL產生輸出信號CLK_IN到達時鐘分配器CLOCK BUFFER,經CLOCK BUFFER分配緩沖后發出兩路同相時鐘,一路是CLKB,用于DRIVER的數據輸出;另一路是CLKA,用于采樣鎖存由DRIVER發往RECEIVER的數據。時鐘CLKB經Tflt_CLKB一段飛行時間(FLIGHT TIME)后到達DRIVER,DRIVER內部數據由CLKB鎖存經過TCO_DATA時間后出現在DRIVER的輸出端口上,輸出的數據然后再經過一段飛行時間Tflt_DATA到達RECEIVER的輸入端口;在RECEIVER的輸入端口上,利用CLOCK BUFFER產生的另一個時鐘CLKA(經過的延時就是CLKA時鐘飛行時間,即Tflt_CLKA)采樣鎖存這批來自DRIVER的數據,從而完成COMMON CLOCK一個時鐘周期的數據傳送過程。

以上過程表明,到達RECEIVER的數據是利用時鐘下一個周期的上升沿采樣的,據此可得到數據傳送所應滿足的兩個必要條件:①RECEIVER輸入端的數據一般都有所要求的建立時間Tsetup,它表示數據有效必須先于時鐘有效的最小時間值,數據信號到達輸入端的時間應該足夠早于時鐘信號,由此可得出建立時間所滿足的不等式;②為了成功地將數據鎖存到器件內部,數據信號必須在接收芯片的輸入端保持足夠長時間有效以確保信號正確無誤地被時鐘采樣鎖存,這段時間稱為保持時間,CLKA的延時必須小于數據的無效時間(INVALID),由此可得出保持時間所滿足的不等式。

1.1 數據建立時間的時序分析

由第一個條件可知,數據信號必須先于時鐘CLKA到達接收端,才能正確地鎖存數據。在公共時鐘總線中,第一個時鐘周期的作用是將數據鎖存到DRIVER的輸出端,第二個時鐘周期則將數據鎖存到RECEIVER的內部,這意味著數據信號到達RECEIVER輸入端的時間應該足夠早于時鐘信號CLKA。為了滿足這一條件,必須確定時鐘和數據信號到達RECEIVER的延時并保證滿足接收端建立時間的要求,任何比需要的建立時間多出來的時間量即為建立時間時序余量Tmargin。在圖1的時序圖中,所有箭頭線路表示數據信號和時鐘信號在芯片內部或傳輸線上產生的延時,在下面的箭頭線路表示從第一個時鐘邊沿有效至數據到達RECEIVER輸入端的總延時,在上面的箭頭線路表示接收時鐘CLKA的總延時。從第一個時鐘邊沿有效至數據到達RECEIVER輸入端的總延時為:

TDATA_DELAY=TCO_CLKB+Tflt_CLKB+TCO_DATA+Tflt_DATA

接收時鐘CLKA下一個周期的總延時為:

TCLKA_DELAY=TCYCLE+TCO_CLKA+Tflt_CLKA

要滿足數據的建立時間則必須有:

TCLKA_DELAY_MIN-TDATA_DELAY_MAX-Tsetup-Tmargin》0

展開并考慮時鐘的抖動Tjitter等因素整理后得到:

TCYCLE+(TCO_CLKA_MIN-TCO_CLKB_MAX)+ (Tflt_CLKA_MIN-Tflt_CLKB_MAX)-TCO_DATA_MAX-Tflt_DATA_SETTLE_DELAY_MAX-Tjitter-Tsetup-Tmargin》0 (1)

式(1)中TCYCLE為時鐘的一個時鐘周期;第一個括號內是時鐘芯片CLOCK BUFFER輸出時鐘CLKA、CLKB之間的最大相位差,即手冊上稱的OUTPUT-output skew;第二個括號內則是CLOCK BUFFER芯片輸出的兩個時鐘CLKA、CLKB分別到達RECEIVER和DRIVER的最大延時差。式(1)中TCO_DATA是指在一定的測試負載和測試條件下,從時鐘觸發開始到數據出現在輸出端口并到達測試電壓Vmeas(或VREF)閾值的時間間隔,TCO_DATA的大小與芯片內部邏輯延時、緩沖器OUTPUT BUFFER特性、輸出負載情況都有直接關系,TCO可在芯片數據手冊中查得。

由公式(1)可知,可調部分實際只有兩項:Tflt_CLKB_MIN-Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX。單從滿足建立時間而言,Tflt_CLKA_MIN應盡可能大,而Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX則要盡可能小。實質上,就是要求接收時鐘來得晚一點,數據來得早一點。

1.2 數據保持時間的時序分析

為了成功地將數據鎖存到器件內部,數據信號必須在接收芯片的輸入端保持足夠長時間有效以確保信號正確無誤地被時鐘采樣鎖存,這段時間稱為保持時間。在公共時鐘總線中,接收端緩沖器利用第二個時鐘邊沿鎖存數據,同時在驅動端把下一個數據鎖存到數據發送端。因此為了滿足接收端保持時間,必須保證有效數據在下一個數據信號到達之前鎖存到接收端觸發器中,這就要求接收時鐘CLKA的延時要小于接收數據信號的延時。

TCLKA_DELAY=TCO_CLKA+Tflt_CLKA

而數據延時:

TDATA_DELAY=TCO_CLKB+Tflt_CLKB+TCO_DATA+Tflt_DATA_SWITCH_DELAY

若要滿足數據的保持時間,則必須有:

TDATA_DELAY_MIN-TCLKA_DELAY_MAX-Thold-Tmargin》0

展開、整理并考慮時鐘抖動Tjitter等因素,可得如下關系:

(TCO_CLKB_MIN-TCO_CLKA_MAX)+(Tflt_CLKB_MIN-Tflt_CLKA_MAX)+TCO_DATA_MIN+Tflt_DATA_SWITCH_DELAY_MIN-Thold-Tmargin-Tjitter》0 (2)

式(2)中,第一個括號內仍然是時鐘芯片CLOCK BUFFER輸出時鐘之間的最大相位差;第二個括號內繼續可以理解為時鐘芯片輸出的兩個時鐘CLKA、CLKB分別到達RECEIVER和DRIVER的最大延時差;要滿足數據的保持時間,實際可調整的部分也只有兩項,即Tflt_CLKB_MIN-Tflt_CLKA_MAX和Tflt_DATA_SWITCH_DELAY_MIN。單從滿足保持時間的角度而言,Tflt_CLKB_MIN和Tflt_DATA_SWITCH_DELAY_MIN應盡可能大,而Tflt_CLKA_MAX則要盡可能小。也就是說,若欲滿足保持時間,就要使接收時鐘早點來,而數據則要晚點無效(invalid)。

為了正確無誤地接收數據,必須綜合考慮數據的建立時間和保持時間,即同時滿足(1)式和(2)式。分析這兩個不等式可以看出,調整的途徑只有三個:發送時鐘延時、接收時鐘延時和數據的延時。調整方案可這樣進行:首先假定發送時鐘延時嚴格等于接收時鐘延時,即?Tflt_CLKA_MIN-Tflt_CLKB_MAX =0和?Tflt_CLKB_MIN-Tflt_CLKA_MAX =0(后文將對這兩個等式的假設產生的時序偏差進行考慮),然后通過仿真可以得出數據的延時范圍,如果數據延時無解則返回上述兩個等式,調整發送時鐘延時或接收時鐘延時。下面是寬帶網交換機中GLINK總線公共時鐘同步數據收發的例子:首先假定發送時鐘延時嚴格等于接收時鐘延時,然后確定數據的延時范圍,代入各參數,(1)和(2)式分別變為:

1.5-Tflt_DATA_SETTLE_DELAY_MAX-Tmargin》0

0.5+Tflt_DATA_SWITCH_DELAY_MIN-Tmargin》0

在不等式提示下,結合PCB布局實際,確定Tflt_DATA_SETTLE_DELAY_MAX《1.1;tflt_data_switch_delay_min》-0.1,剩下0.4ns的余量分配給了兩個時鐘的時差和Tmargin。在SPECCTRAQUEST中提取拓撲并進行信號完整性仿真,進而確定各段線長及拓撲結構。對此結構(共12種組合)進行全掃描仿真,得到?Tflt_DATA_SETTLE_DELAY_MAX=1.0825? Tflt_DATA_SWITCH_DELAY_MIN =-0.0835004,符合確定的1.1和-0.1的范圍指標。由此可以得出GLINK總線數據線的約束規則:①匹配電阻到發送端的延時不應大于0.1ns;②數據線必須以0.1ns進行匹配,即每個數據線都必須在0.65ns~0.75ns之間。有了上述的約束規則就可以指導布線了。

下面再考慮硬性規定 Tflt_CLKA_MIN-Tflt_CLKB_MAX=0和Tflt_CLKB_MIN-Tflt_CLKA_MAX=0帶來的影響。事先約束發送時鐘和接收時鐘完全等長(在實際操作中以0.02ns進行匹配)?在CADENCE環境下,進行時鐘仿真,得到結果:|Tflt_CLKA_MIN-Tflt_CLKB_MAX|《0.2和|tflt_clkb_min-tflt_clka_max|《0.2。可見留給tmargin的余量為0.2ns。

最終的仿真結果是:① 匹配電阻到發送端的延時不應大于0.1ns;②數據線以0.1ns進行匹配,即每個數據線都必須在0.65ns~0.75ns之間;③發送時鐘和接收時鐘以0.02ns匹配等長;④Tmargin=0.2ns。有了上述拓撲結構樣板和約束規則就可以將SPECCTRAQUEST或ALLEGRO導入到CONSTRAINS MANAGER中。當這些設計約束規則設置好后,就可以利用自動布線器進行規則驅動自動布線或人工調線。

2 源同步時序關系及仿真實例

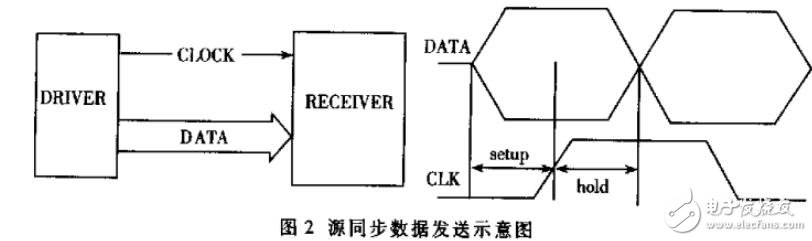

所謂源同步就是指時鐘選通信號CLK由驅動芯片伴隨發送數據一起發送,它并不象公共時鐘同步那樣采用獨立的時鐘源。在源同步數據收發中,數據首先發向接收端,經稍短時間選通時鐘再發向接收端用于采樣鎖存這批數據。其示意圖如圖2所示。源同步的時序分析較公共時鐘同步較為簡單,分析方法很類似,下面直接給出分析公式:

建立時間:Tvb_min+(Tflt_clk_min-Tflt_data_settle_delay_max)-Tsetup-Tmargin》0

保持時間:Tva_min+(Tflt_data_switch_delay min-Tflt_clk _max)-Thold-Tmargin》0

其中,Tvb為驅動端的建立時間,表示驅動端數據在時鐘有效前多少時間有效;Tva為發送端的保持時間,表示驅動端數據在時鐘有效后保持有效的時間;其他參量含義同前。下面以通信電路中很常見的TBI接口為例介紹源同步時序分析及仿真過程。TBI接口主要包括發送時鐘和10bit的發送數據、兩個接收時鐘和10bit接收數據。RBC0、RBC1為兩個接收時鐘,在千兆以太網中,這兩個時鐘頻率為62.5MHz,相差為180°,兩個時鐘的上升沿輪流用于鎖存數據。根據數據手冊的時序參數,代入上式可得:

2.5+?Tflt_clk _min-Tflt_data__settle_delay_max -1-Tmargin》0

1.5+?Tflt_data__switch_delay min-Tflt_clk _max -0.5-Tmargin》0

仿照前述分析方法:假設時鐘、數據信號線的飛行時間嚴格相等,即時鐘和數據完全匹配,然后分析它們不匹配帶來的影響。上式變為?

1.5-Tmargin》0

1-Tmargin》0

可見,無論是建立時間還是保持時間都有很大的余量。經過仿真,發現數據和時鐘完全匹配等長(以0.02ns匹配為例),仍有0.3ns的差別,即

?Tflt_clk_min-Tflt_data_settle_delay_max《0.3

?Tflt_data_switch_delay min-Tflt_clk_max《0.3

取Tmargin=0.5ns得到時鐘和數據的匹配為0.2ns,即數據和時鐘的長度匹配不應超過0.2ns。

在實際仿真中首先就時鐘和數據的信號完整性進行分析仿真,通過適當的端接匹配得到較好的接收波形。圖3是一組無源端匹配和有源端匹配時鐘線的不同仿真波形比較,從中可以看出首先進行信號完整性仿真的必要性。

在公共時鐘同步中,數據的發送和接收必須在一個時鐘周期內完成。同時器件的延時和PCB走線的延遲也限制了公共時鐘總線的最高理論工作頻率。故公共時鐘同步一般用于低于200MHz~300MHz的傳輸速率,高于這個速率的傳輸,一般應引入源同步技術。源同步技術工作在相對的時鐘系統下,采用數據和時鐘并行傳輸,傳輸速率主要由數據和時鐘信號間的時差決定,這樣可以使系統達到更高的傳輸速率。筆者通過對寬帶以太網交換機主機和子卡板進行信號完整性分析、時序分析及其仿真,大大縮短了產品的設計周期,通過分析仿真有效地解決了高速設計中出現的信號完整性、時序等方面的問題,充分保證了設計的質量和設計速度,真正做到了PCB板的一次通過。主板和子卡板目前已經通過調試,并順利轉產。

電子發燒友App

電子發燒友App

評論