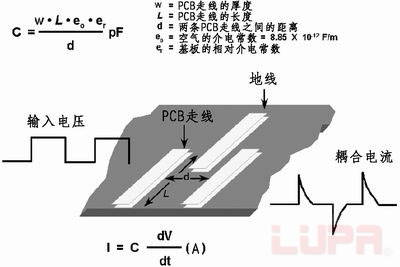

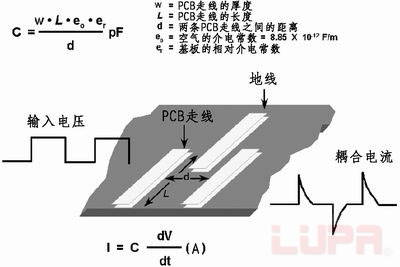

PCB布線設計時寄生電容的計算方法

在PCB上布兩條靠近的走線,很容易產生寄生電容。由于這種寄生電容的存在,

2009-09-30 15:13:33 26465

26465

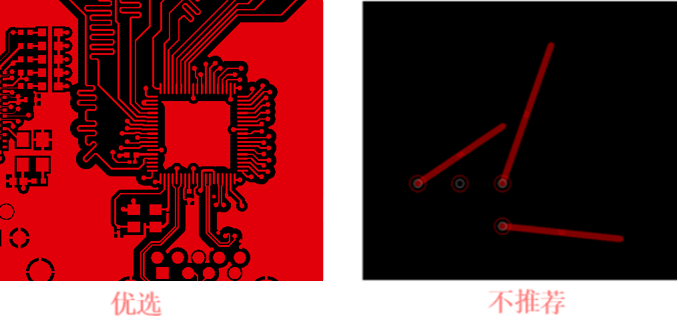

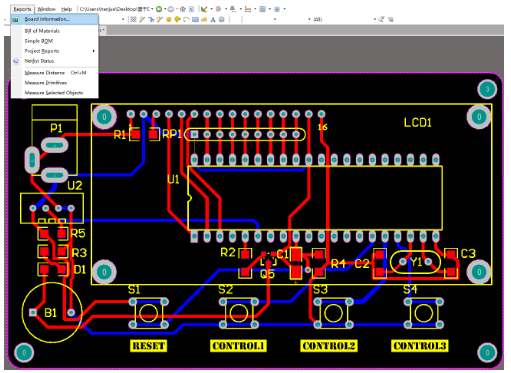

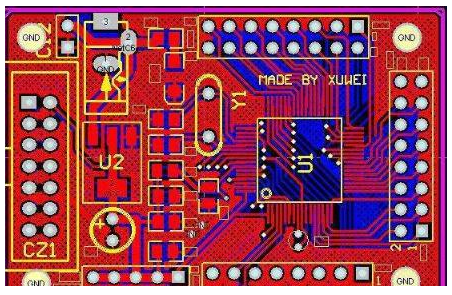

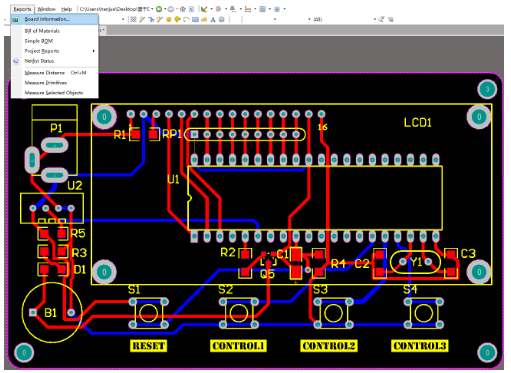

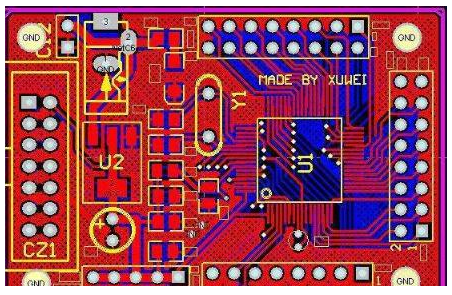

相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優等。 在上

2023-07-25 18:00:00 1319

1319

相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優等。 本篇

2023-12-05 19:40:01 723

723

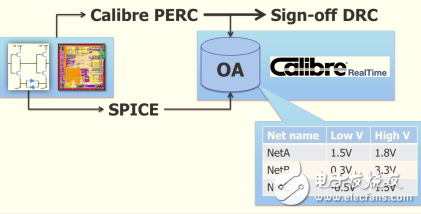

電源域隔離是電壓監控ADC系統的一個重要設計要點,不合理的電源域隔離可能導致芯片關不掉,芯片發生閂鎖,甚至芯片損壞的后果。這些問題主要是由于芯片內部ESD保護二極管的限制,那么如何更好處理電源域隔離設計呢?

2019-02-25 09:08:09

本節介紹Windows 2000/03 AD域故障的排錯。首先我們會介紹活動目錄(Active Directory)及其相關概念,然后介紹和域故障排錯相關的知識、工具軟件的使用,最后以實例的形式講解針對具體的各種域故障如何進行排錯,如何有效地利用組策略來管理AD域、管理網絡。

2019-07-18 07:09:24

解決不同的問題,本應用文章為《MDO4000 系列混合域分析儀應用之一--跨域分析發現當代數字射頻系統疑難雜癥的創新手段》,重點闡述MDO4000的第一個、也是最具創新意義的特色及其應用。其它兩個特色將在《MDO4000 系列混合域分析儀應用之二、之三》中進一步闡述,有興趣的讀者可以進一步參閱。

2019-07-19 07:02:07

分析儀的以上特色,針對不同的應用可以解決不同的問題,MDO4000 的最突出的特色—跨域分析已經在應用文章為《MDO4000 系列混合域分析儀應用之一—跨域分析發現當代數字射頻系統疑難雜癥的創新

2019-07-19 06:43:08

檢查這種布線策略時,首先發現的弊端是存在多個地環路。另外,還會發現底層的地線返回路徑被水平信號線隔斷了。這種接地方案的可取之處是,模擬器件(12位A/D轉換器MCP3202和2.5V參考電壓源

2018-08-28 15:42:19

設計時最好采用較多的電路層并使敷銅均勻分布,以避免在設計臨近結束時才發現有少量信號不符合已定義的規則以及空間要求,從而被迫添加新層。在設計之前認真的規劃將減少布線中很多的麻煩。 自動布線工具本身

2017-10-23 11:22:09

設計時最好采用較多的電路層并使敷銅均勻分布,以避免在設計臨近結束時才發現有少量信號不符合已定義的規則以及空間要求,從而被迫添加新層。在設計之前認真的規劃將減少布線中很多的麻煩。 自動布線工具本身

2018-09-19 15:58:33

、電源、地線設計、電壓誤差和由PCB布線引起的電磁干擾(EMI)等幾個方面,討論模擬和數字布線的基本相似之處及差別。 模擬和數字布線策略的相似之處 旁路或去耦電容 在布線時,模擬器件和數字器件都

2011-09-02 09:36:14

,PCB 設計的難度也越來越大。如何實現PCB 高的布通率以及縮短設計時間,在這筆者談談對PCB 規劃、布局和布線的設計技巧。 在開始布線之前應該對設計進行認真的分析以及對工具軟件進行認真的設置,這會

2018-11-22 15:25:15

盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設計的難度并不小。如何實現PCB高的布通率以及縮短設計時間呢?本文介紹PCB規劃、布局和布線的設計技巧和要點。

2021-01-22 06:44:11

PMIC 情況如何處理1 電源域設置1.1 驅動文件與 DTS 節點:驅動文件所在位置1.2 使用 IO-Domain 驅動好處:在 IO-Domain 的 DTS 節點統一配置電壓域,不需要每個驅動都去配置一次,便于管理;依照的是 Upstream 的做法,以后如果需要 Upstream 比較方便

2022-01-03 07:24:25

UNIX域套接字用于在同一臺計算機上運行的進程之間的通信。雖然因特網域套接字可用于同一目的,但UNIX域套接字的效率更高。UNIX域套接字僅僅復制數據,它們并不執行協議處理,不需要添加或刪除網絡報頭

2016-09-02 11:59:01

XP退域后怎么才能加回以前的域是這樣一件事情,我的XP電腦是不連接網絡的,但是它之前的用戶一直連接那域, 這次我修改的工作組,結果那域不見了,用戶也進不去了;請問還能加回以前的域嗎?

2012-06-09 16:41:55

pcb設計時,布線90度和兩層之間平行。為什么布線角度不能使90度,是不是想初中高中的那樣,電流流過導線,會產生電磁場,干擾信號。/ y; i9 x0 E6 G- ?+ E就像兩線平行,電流相同

2014-10-24 14:33:52

the selection cannot be launched我是菜鳥,解決不了的問題,求解答

2015-07-05 16:44:22

的設計效果。布線的基本規則PCB設計的好壞對其抗干擾能力影響很大。因此,在PCB設計時,必須遵守設計的基本原則,并應符合抗干擾設計的要求,使得電路獲得最佳得性能。印制導線得布設應盡可能短;統一元器件得

2018-12-07 22:50:21

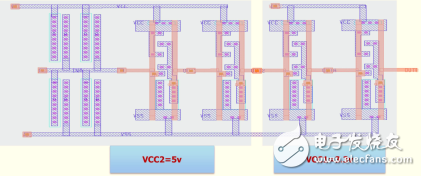

3.3V;同理IO電源域硬件配置為1.8V,則IO輸出最大電平是1.8V;這樣有利于IO電平的靈活配置;IO電源域一般都會接到PMU電源芯片不同組的LDO,由PMU配置輸出電平,因為PMU的LDO可以在DTS上配置不同的電壓;這樣不至于把IO的輸出最大的電平寫死,可動態調整;如圖中...

2021-12-27 06:44:14

什么是UPF功率域和域邊界?

2021-09-29 06:08:09

ISE中編譯為.bit文件。系統被設計為多重鎖定域,其中第一個域只是獲取數據并負責寫入和重置共享FIFO,并且從相機計時(因此也以相同的時鐘速度運行 - 大約8MHz) - 此信號用于Sys.gen。具有

2019-08-27 06:28:47

在支持位操作的單片機中,如C51,使用位域定義變量或者寄存器,操作方便并且節約空間。 問題1:但是很多單片機不支持位操作,仍然使用位域,那么匯編語言將如何執行?我理解的是,匯編間接實現位操作,但是

2016-09-16 22:25:32

一、位域描述存放一個開關量或者其他開關狀態時,用一位二進位即可。為了減少嵌入式內存資源的開銷,可以使用位域進行定義,位域是C語言支持的一種數據結構,稱為“位域”或“位段”。“位域”是把一個字節中

2021-12-15 07:47:52

#hello,JS:04作用域和作用域鏈

2019-09-10 10:21:18

最好的設計效果。布線的基本規則PCB設計的好壞對其抗干擾能力影響很大。因此,在PCB設計時,必須遵守設計的基本原則,并應符合抗干擾設計的要求,使得電路獲得最佳得性能。印制導線得布設應盡可能短;統一

2018-11-23 16:07:58

關于異步時鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時鐘域吧?大俠幫解決下我的心結呀,我這樣的理解對嗎?

2012-02-27 15:50:12

制作了一款加域工具,可以實現的功能如下,源代碼供參考:調用的是AD.au3根據地域不同,生成不同的計算機名前綴根據地域不同,分配到不同的OU在生成的計算機名后增加2位數字,且在域內進行查找,確保沒有重復的計算機名將計算機加域,且更換計算機名

2019-07-16 07:05:45

本人在設計層次原理圖設計時使用了多通道設計的方法,卻出現了如圖所示的警告,我已經網絡標號的作用域改過,卻沒效果。

2014-05-01 21:22:53

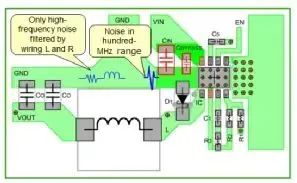

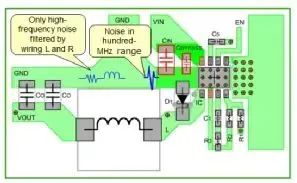

的電阻和電感反饋路徑的布線反饋信號的布線在信號布線過程中也需要特別注意。反饋信號如Figure 7-a左側的電路圖所示,輸出電壓經由布線,由電阻分壓,被反饋至電源IC的FB引腳-即誤差放大器的輸入端,電源

2018-11-30 11:49:21

在AD9787里面,數字電壓有兩個一個是DVDD33,一個是DVDD18,想問的是,哪些管腳是屬于DVDD33的電源域,哪些是屬于DVDD18的電源域?

2023-12-01 06:33:52

/s,高速D/A 通道采樣率可達125 MS /s。VHS-ADC 實現了與Simulink 的無縫連接。本文在分析系統原理和設計系統參數基礎上,在Simulink 中搭建了諧波電壓源的連續域模型

2018-10-18 16:33:25

時鐘)的邏輯。在真正的ASIC設計領域,單時鐘設計非常少。2、控制信號從快時鐘域同步到慢時鐘域與同步器相關的一個問題是來自發送時鐘域的信號可能在被慢時鐘域采樣之前變化。將慢時鐘域的控制信號同步到快時鐘域

2022-04-11 17:06:57

如何實現PCB高的布通率以及縮短設計時間呢?如何實現PCB高效自動布線的設計?

2021-04-23 06:39:20

電源域隔離是電壓監控ADC系統的一個重要設計要點,不合理的電源域隔離可能導致芯片關不掉,芯片發生閂鎖,甚至芯片損壞的后果。這些問題主要是由于芯片內部ESD保護二極管的限制,以及芯片上電時序的限制

2022-11-10 08:17:59

設計時最好采用較多的電路層并使敷銅均勻分布,以避免在設計臨近結束時才發現有少量信號不符合已定義的規則以及空間要求,從而被迫添加新層。在設計之前認真的規劃將減少布線中很多的麻煩。 自動布線工具本身

2018-09-19 15:53:39

想用一個兩我的數碼管進行倒計時,一開始倒計時45秒,然后3秒,然后30秒,然后依次循環,主要是在前面的顯示對現在顯示重疊在一起了,然后數碼管就亂碼了,求解決不辦法

2013-11-21 19:19:51

理解UPF功率域和域邊界一、介紹 在先進工藝技術的低功耗之爭中,統一功率格式(UPF)在降低動態和靜態功率方面起著核心作用。較高的流程節點絕對具有吸引力,因為在較小的die區域中可以以較低的成本

2021-07-26 06:23:19

上完成復雜的測量。 對嵌入式無線電,如圖16所示的Zigbee設計.您可以觸發 RF事件啟動,觀察微處理器控制器解碼的SPI控制線的命 令行時延、啟動過程中的漏極電流和電壓以及發生的任何 頻譜事件。您現在可以在一個畫面中,以時間相關的方式 觀察無線電的所有域:協議(數宇)、模擬和RF。

2017-08-31 08:55:59

電源域是什么?

2017-08-07 18:59:27

多層板解決方案更是工程師在設計時必需的重要考慮。本文將探討雙層板的布線方式,使用自動布線與手工布線來做模擬與混合信號電路布線的差別,如何安排接地回路等。電池供電產品的競爭市場中,考慮目標成本

2016-04-28 11:45:56

相同的IO域VDDPST和VDD的電壓輸入是一樣的嗎?RK3399中的IO域電壓該怎樣去選擇呢?

2022-03-07 07:10:14

瞬時電流達到60A的電機供電電路,PCB布局布線設計時注意事項,除了加厚加寬涂錫外,還要注意什么?

2018-05-07 15:13:54

問題描述及復現步驟:編譯kernel就一直出現這個問題解決不了,求助

2022-11-21 17:15:28

高效自動布線的設計!!盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設計的難度并不小。如何實現PCB高的布通率以及縮短設計時間呢?本文介紹PCB規劃、布局和布線

2013-01-29 10:45:49

,那么共享同一電壓軌(AD9208為0.975 V)的數字電路和模擬電路發生震顫的可能性將非常小。在硅片中,電源已被分開,接地也是如此。封裝設計繼續貫徹了這種隔離電源域處理。由此所得的同一封裝內不同電源

2018-10-30 11:49:44

Keysight 53230A 通用頻率計數器/計時器可滿足您所有的頻率和時間間隔測量需求。除了典型的頻率和時間間隔測量,它還可執行連續/無間隙測量,以進行基本調制域分析。53230A

2022-07-13 18:22:23

探索雙層板布線技藝電池供電產品的競爭市場中,考慮目標成本相對的重要。多層板解決方案更是工程師在設計時必需的重要考慮。本文將探討雙層板的布線方式,使用自動布線

2010-10-05 09:44:16 0

0 計時器,什么是計時器,計時器原理是什么

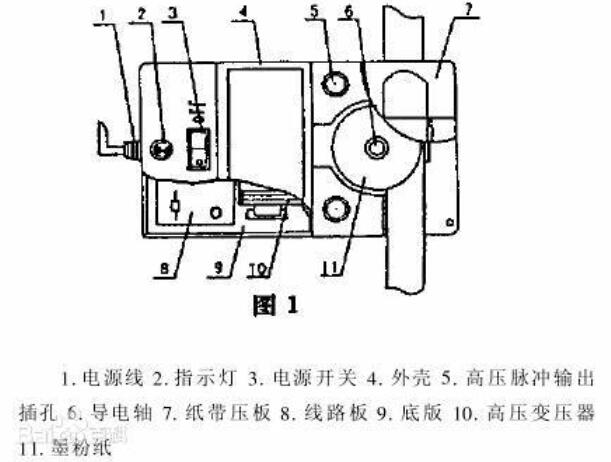

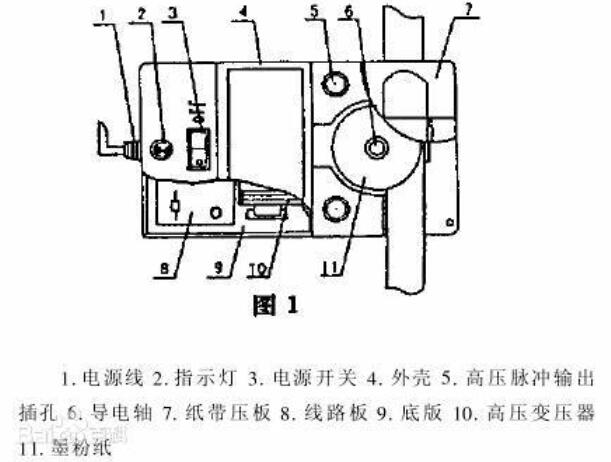

計時器,是利用特定的原理來測量時間的裝置。計時器的種類包括電磁打點計時器、電火花計時器、堅持計

2010-03-08 17:52:50 8260

8260 本文根據標準附件中有關數據中心可靠性分級的內容,介紹了數據中心通信基礎及布線設計時的冗余考慮。

2011-07-17 10:52:11 1534

1534 DS1672低電壓計時芯片包含32位計數器和電源監視電路。32位計數器用作秒計數,通過軟件算法可產生時間、星期、月、年信息。精準的溫度補償基準和比較器用來監視VCC的狀態

2011-10-18 14:53:25 2764

2764

PCB布線設計-PCB布線設計經驗大全(二)

2016-08-16 19:37:49 0

0 相鄰布線層注意在分層設計時,應避免布線層相鄰。如果無法避免,應適當拉大兩布線層上的平行信號走線會導致信號串擾。線層之間的層間距,縮小布線層與其信號回路之間的層間距,布線層1與布線層2不宜相鄰。

2017-11-27 16:02:48 8771

8771 這篇文章主要介紹了解決不重復序列的全排列問題的兩個方法:遞歸和字典序法。

2018-03-29 11:19:33 6233

6233

電路板尺寸和布線層數需要在設計初期確定。布線層的數量以及層疊(STack-up)方式會直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實現期望的設計效果。目前多層板之間的成本差別很小,在開始設計時最好采用較多的電路層并使敷銅均勻分布。

2019-06-03 14:47:45 1410

1410 布線的方式也有兩種,手工布線和自動布線。PowerPCB提供的手工布線功能十分強大,包括自動推擠、在線設計規則檢查(DRC),自動布線由Specctra的布線引擎進行,通常這兩種方法配合使用,常用的步驟是手工-自動-手工。

2019-05-31 15:22:27 3100

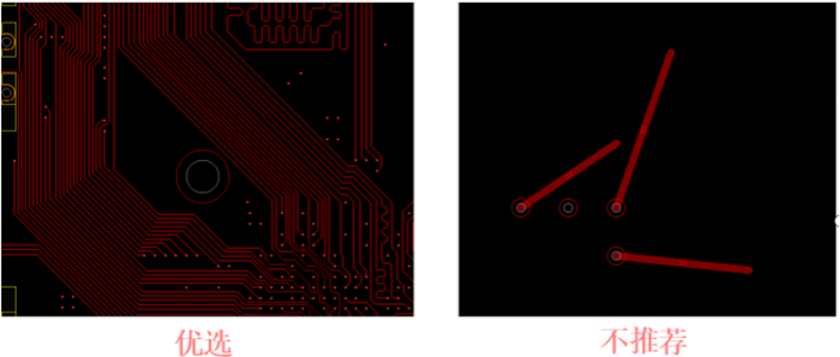

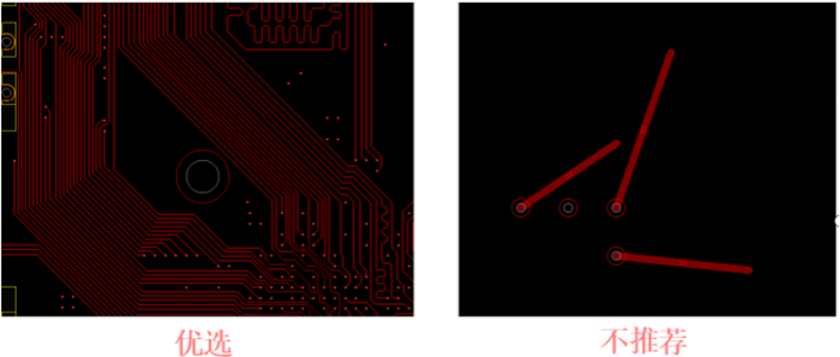

3100 PCB設計時,我們是根據飛線來進行布線,而飛線很細往往容易被網格和絲印層的線條蓋住,使我們看不見飛線而漏掉要布的線。這里有三種檢查方法。

2019-05-08 14:23:29 9571

9571

參加本研討會可了解,PADS 強大的 Layout 和布線功能可如何縮短設計時間,并改進 PCB 的可制造性。我們將討論如何通過合理的布局來減少層數、過孔和走線長度,以及如何大幅縮短布線電路板所花的時間。

2019-05-16 06:20:00 4030

4030

在PCB板設計時,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。

2019-08-15 13:52:00 1121

1121 為了保證線路板設計時的質量問題,在PCB設計的時候,要注意PCB圖布線的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 電路板尺寸和布線層數需要在設計初期確定。布線層的數量以及層疊(STack-up)方式會直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實現期望的設計效果。目前多層板之間的成本差別很小,在開始設計時最好采用較多的電路層并使敷銅均勻分布。

2019-09-18 11:37:38 822

822 有一點需要注意,PCB布線沒有嚴格的規定,也沒有能覆蓋所有PCB布線的專門的規則。大多數PCB布線受限于線路板的大小和覆銅板的層數。一些布線技術可以應用于一種電路,卻不能用于另外一種,這便主要依賴于布線工程師的經驗。然而還是有一些普遍的規則存在,下面將對其進行探討。

2019-09-20 15:19:09 1752

1752

現在有許多PCB不再是單一功能電路(數字或模擬電路),而是由數字電路和模擬電路混合構成的。因此在布線時就需要考慮它們之間互相干擾問題,特別是地線上的噪音干擾。

2020-01-22 17:09:00 952

952

電磁打點計時器使用交流電,工作電壓都比較小,是由小型變壓器將220V交流電降壓作為電源,一般介于5~~11v之間,學生用電磁打點計時器的工作電壓通常是6V。

2020-01-08 10:13:51 28567

28567 本文首先闡述了電火花計時器結構原理,其次介紹了電火花計時器工作原理,最后介紹了電火花計時器工作電壓。

2020-01-08 10:25:03 20142

20142

印刷導線應盡可能短;統一組件的地址線或數據線應盡可能長;當電路為高頻電路或布線密集時,印刷導線的角應為圓形。否則,它會影響電路的電氣特性。

2020-05-28 08:42:01 1499

1499 無疑云數據中心和邊緣數據中心相輔相成將會承擔起這一重要任務,且需求量會更加龐大,而對于各類數據中心的布線系統由于其承載了數據傳輸的任務,須考慮其超前性,預判性,所以在布線系統設計時不僅要考慮當前的設數據傳輸和設備互聯需求,更要考慮其未來更高傳輸性能的要求。

2020-09-02 10:17:09 2673

2673 設置用于 印刷電路板 布線 的規則和約束不應被視為對我們工作的負面影響。這可能會花費一些時間,需要進行研究和手動輸入,但是設置這些約束并按照規則布線可以節省您的設計時間并增加效率。我們將研究

2020-09-12 19:06:10 2166

2166 最初,自動路由的想法聽起來不錯。一臺能為您完美布線的機器?那不是太神奇了嗎?不幸的是,早期的自動布線器遠非完美。 我們發現在計算機輔助設計( CAD )出現之前,設計印刷電路板( PCB )是一項

2020-09-28 19:06:15 2074

2074 盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設計的難度并不小。如何實現PCB高的布通率以及縮短設計時間呢?本文介紹PCB規劃、布局和布線的設計技巧和要點。

2022-02-10 14:35:43 716

716 DN1029-通過動態補償布線和連接器中的電壓降,收緊2A USB設備的電源調節

2021-04-14 21:01:32 5

5 AN-245:儀表放大器解決不尋常的設計問題

2021-05-21 19:08:52 4

4 一、布線注意事項 1、使用電線時,其額定電壓應大于線路的工作電壓;導線的絕緣應符合線路的安裝方式和敷設環境條件。導體的截面積應能滿足供電和機械強度的要求。接線時,盡量避開電線中的連接器。除非接頭

2021-12-02 14:55:22 4559

4559 電路板尺寸和布線層數需要在設計初期確定。布線層的數量以及層疊(stack-up)方式會直接影響到印制線的布線和阻抗。 板的大小有助于確定層疊方式和印制線寬度,實現期望的設計效果。目前多層板之間的成本差別很小,在開始設計時采用較多的電路層并使敷銅均勻分布。

2023-02-09 09:37:58 449

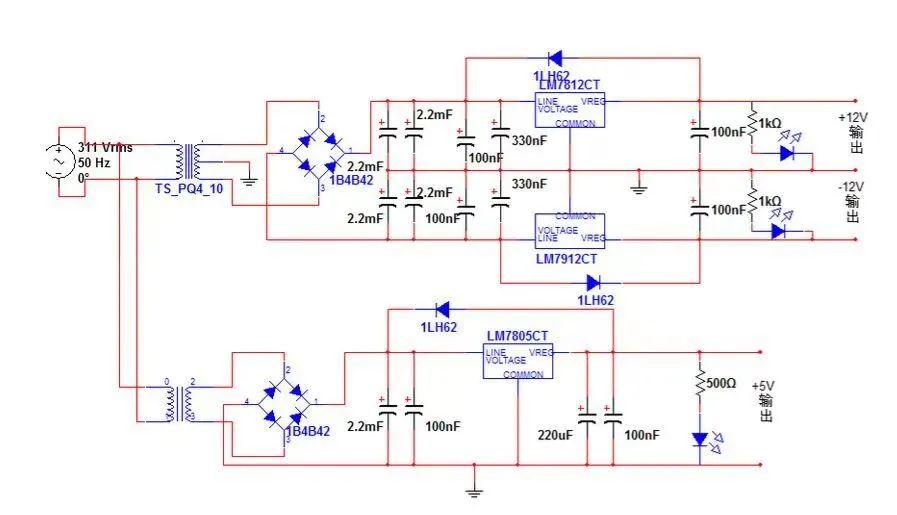

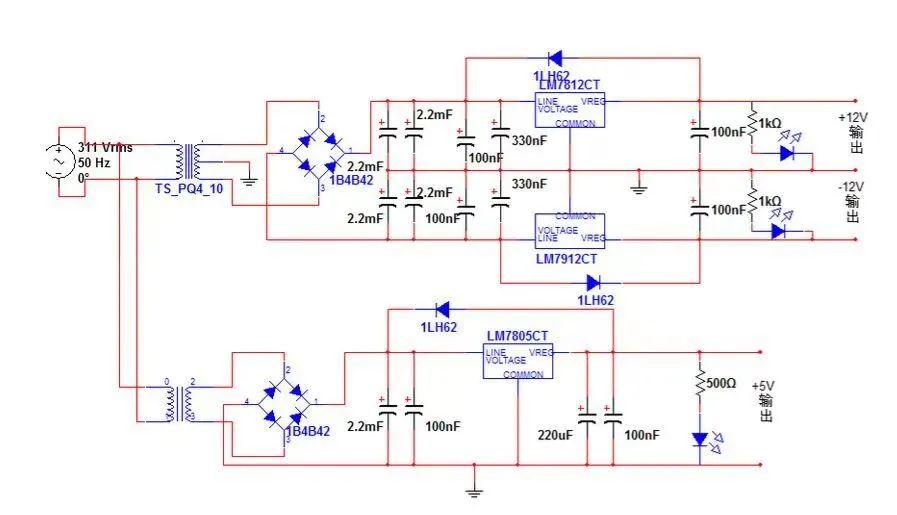

449 在進行電路設計時,電源布局布線是一個非常重要的步驟,一個電子硬件主板,如果本身供電就不穩定,又談何電子主板電路穩定呢?

2023-06-28 15:52:03 422

422

在進行電路設計時,電源布局布線是一個非常重要的步驟,一個電子硬件主板,如果本身供電就不穩定,又談何電子主板電路穩定呢?

2023-06-28 15:52:11 810

810

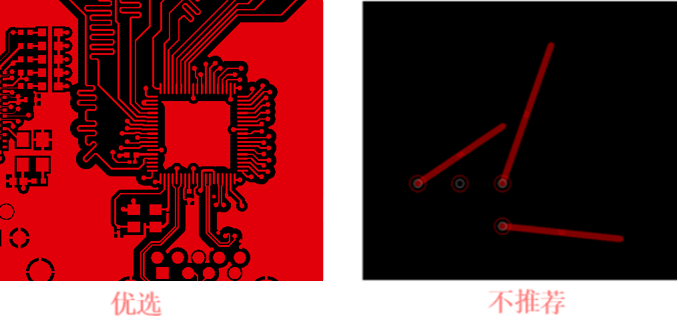

相信大家在做PCB設計時,都會發現 布線這個環節 必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優

2023-07-28 14:25:24 502

502

相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優等。在上

2023-08-03 08:09:13 687

687

如何用555計時器做1S脈沖源?555工作電壓是多少?? 555計時器是一種非常常見的集成電路,廣泛應用于定時、延時、脈沖發生等各種電子電路中。本文將詳細介紹如何使用555計時器做1S脈沖源,并簡單

2023-09-02 16:19:58 5498

5498 自舉電路的自舉電容在布線時,為什么電容的低電壓腳要采用蛇形布線的方式? 自舉電路是一種常用于自激振蕩電路中的一種電路。它能夠通過自激振蕩產生正弦波信號,并將信號輸出到負載電路中。其中的關鍵部分就是

2023-10-25 11:45:17 453

453 隨著PCB 尺寸要求越來越小,器件密度要求越來越高,PCB 設計的難度也越來越大。如何實現PCB 高的布通率以及縮短設計時間,在這筆者談談對PCB 規劃、布局和布線的設計技巧。

2023-11-09 15:24:23 150

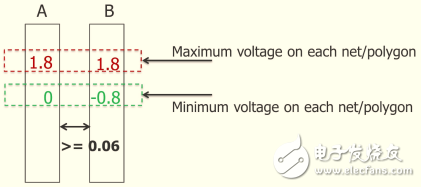

150 在PCB設計中,電壓是其中一個最重要的參數。高電壓可能會導致電弧放電、電暈、電路之間電耦和干擾等問題,而電路之間的布線間距是決定電壓分布的一個重要因素。本文將詳盡地闡述PCB布線間距與電壓之間的關系

2023-12-20 11:24:00 3247

3247 電路板尺寸和布線層數需要在設計初期確定。布線層的數量以及層疊(STack-up)方式會直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實現期望的設計效果。目前多層板之間的成本差別很小,在開始設計時采用較多的電路層并使敷銅均勻分布。

2023-12-28 16:23:22 131

131 相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優等。在上

2023-12-29 08:07:16 350

350

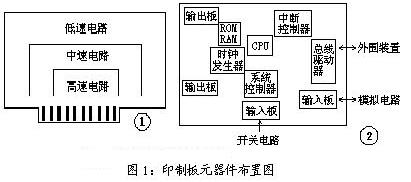

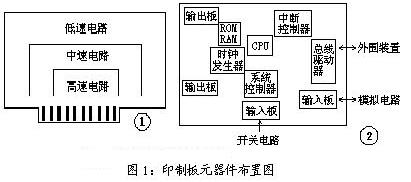

的不良影響。在進行PCB布線設計時,需要遵循一定的規則和原則,下面我們將會介紹PCB設計中的六大布線規則。 PCB設計六大布線規則 一:按照傳輸信號速度分類 在布線時需要按照信號傳輸速度的不同進行分類布線。一般來說,傳輸速度越快的信號需要

2024-01-22 09:23:53 498

498

電子發燒友App

電子發燒友App

評論