PCB電路設計在生產生活中至關重要,本文從電磁兼容這一問題出發,討論PCB電路設計,以及在設計PCB電路過程中存在的電磁干擾等問題。分析單線,多導體線和元器件的設置、路線,從而得出關于PCB電路中布線的一些設計規范和技能。如果將這些原則和規范使用于電路設計的最初環節,那么存在于布線中的電磁干擾問題就會被PCB電路設計師很快的解決。

所謂PCB(Printed Circuit Board),實際上就是印制線路板,它是一種較為重要的電子產品,是電子元器件電氣連接的提供者,在電路元件與電器件之間的銜接上,起重大的作用。是電子元器件的支撐體,對電路元件和器件起支撐作用。抗干擾能力的強弱直接受印制線路板設計的優良影響。因此,線路的設置安排和抗干擾能力是設計師在設計線路時必須同時兼顧的。PCB印制線路板根據電路層數可分為單面板、雙面板和多層板。常見的多層板一般為4層板或6層板,復雜的多層板可達十幾層。

盡管電子工程人員經過很多年的設計與實踐,已經總結出了一些規范和設計經驗,但是截至目前,國家在這一方面并沒有明確的要求和規則。基于此,實踐中我們只能在設計電路過程中充分的運用設計原則和相關規則,進行整體規劃與設計,尤其是進行電路的抗干擾設計。做到以上這些,就能有效避免電路設計實踐中出現嚴重的電磁干擾問題,而且還能有效的降低頻率和節約設計成本費用,對于有效減少電氣電路設計時間具有非常重要的作用。

1 印制電路板中電磁環境的構成

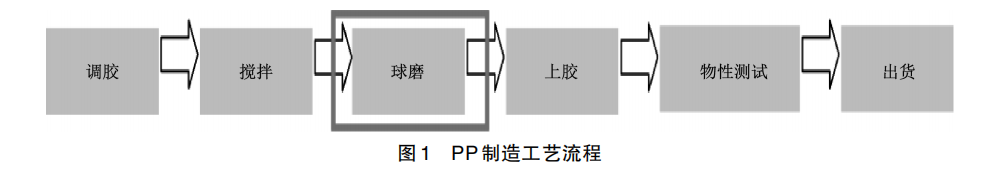

電磁干擾源,耦合途徑和接收器這3個部分組成一個簡單的電磁干擾模型,如圖1所示。

微處理器、微控制器、靜電放電、傳送器以及瞬時功率執行元件都是常見的干擾源,在印制線路板中出現的頻率較高。時鐘電路通常情況下在一個微控制系統里是最大的寬帶噪聲發生器。

傳導耦合和輻射耦合二者共同構成了耦合途徑,在印制線路板中發揮著重要作用。耦合途徑不同,產生的干擾問題也就自然不同。比如:1)互感在導線之中頻頻發生,同時電容處于部分狀態下時,也可能會大幅度上升;2)印制板導線串擾;3)高頻信號經印制導線時所產生的高頻電磁場;4)因時鐘信號而導致的電磁輻射干擾現象;5)反射干擾;6)因一系列操作不當產生的干擾。總之,許多物件都有可能成為敏感元件,包括電子元件和導線。要想整體把握板子的整體布局和元器件的位置就需要在布線上面下功夫,只有合理的布線和達到電磁兼容性標準才是實現這一目的最佳途徑。

2 印制線路板中單根走線

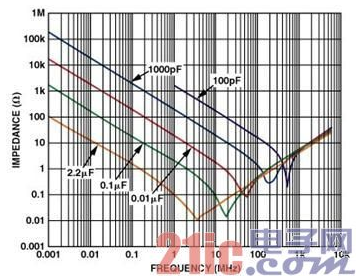

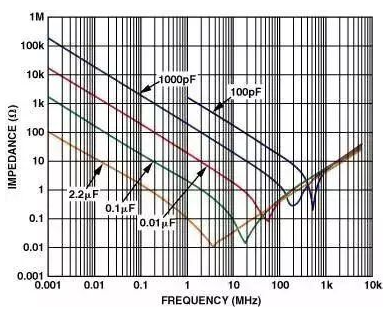

PCB電路設計中,差分走線耦合較小,只占10~20%的耦合度,更多的還是對地的耦合。當地平面發生不連續時。無參考平面區域,差分走線耦合會提供回流通路。

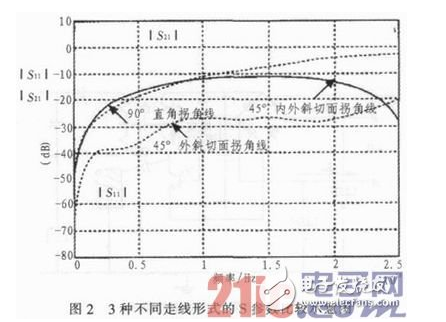

PCB布線中要求避免直角走線的出現。直角走線對信號有著負面影響,因此PCB中的走線一般采用具有45度拐角或圓弧拐角線。直角走線和非直角走線的差異主要有:1)拐角能等效為傳輸線上得容性負載,減少上升的時間;2)拐角也能抵御因不持續而造成的信號反射;3)電磁干擾會因直角尖端產生。

不同的拐角線,角度上具有明顯的差異性。圖2運用了FDTD數值方法進行試驗,通過模擬對反射傳輸特性和反射特性這二者進行對比。在45度外斜切面拐角線反射性與傳輸性能上,優于其他兩種拐角線。這3種走線形式比圓弧的拐角線要差,但是弧度的刻劃成本比較高。這是因為圓弧的刻劃要求精湛的制版技術。精湛的技術必然會引起成本的增加,因此通常在選擇走線時,會將目光停留在45度外斜切面拐角線上。

3 對多導體傳輸線在應用中的串擾探析

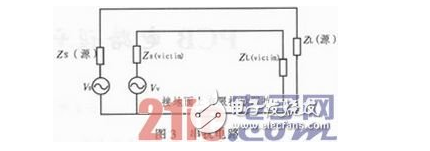

傳送信號和機器的運作頻率在PCB電路設計中要注意適度原則,如果達到兆赫級,那么對線路的干擾就很嚴重。走線間的干擾形成的主要原因是串擾問題。PCB電氣電路設計過程中,應當適當地留意一下串擾問題,盡可能地減少布線串擾問題出現。實踐中可以看到,若發生串擾現象,通常至少會有3個導體和兩個線攜帶信號。如圖3所示,而第3條導線只是作為一種參考而言。

實踐中可以看到,源和受干擾電路之間的作用,通常會產生一種VS,該作用下的zs、zL會產生感應電壓和電流,其zs和源相互聯系,而zL主要與負載端相互聯系。

為減少干擾現象的出現,筆者特提出以下建議和設計規劃:1)以功能作為主要依據的邏輯器件,對總線結構進行控制;2)元件物理距離最小化;3)布線走線長度應嚴格控制;4)元件既要與I/o接口遠離,又要盡可能地避開數據干擾;5)確保阻抗受控走線路徑的準確性,通常頻波能量較大一些的走線應當注意考慮;6)提供一些相交性的走線,以確保走線之間有適當的距離,確保電感耦合最小化;7)緊挨著的布線層應當垂直,這樣可以減小層間電容耦合;8)加強信號與地面之間的間隔和距離控制;9)布線層要單獨隔開,必須以相同軸線布線,確保布線層分置預實心平面結構之中。

4 印制線路板內部元器件的走線分布

通常情況下,功能單元與設備滿足電磁兼容性要求,主要是由電路的基本元件滿足電磁特性的程度決定。

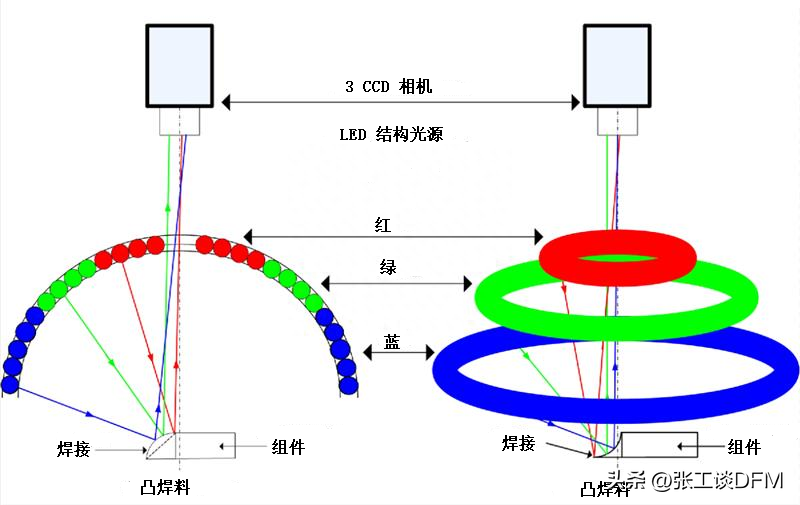

選擇電磁元件時,電磁特性和電路裝配是必須考慮的兩個因素,否則選出的電磁元件是劣質的。這主要是因為遠離基頻的元件響應特性決定了電磁兼容性是否實現。大多情況下,對外響應(比如引線的長度)和元件之間耦合的程度由電路裝配決定。需要注意以下幾點。

PCB大小是首先要考慮到的一個因素。PCB尺寸要適中,過大過小都不合要求。如果太過,則印制時需有很多的線條,以此來增加阻抗、下挫抗噪聲性能,然其成本會隨之增加;如果太小,則缺乏散熱能力,受干擾對象便會擴展至相鄰的線條。基于此,在確定特殊元件的位置之前,應當充分地測量PCB實際規格和尺寸;以電路功能為基礎,對電路中的所有元器件統一的規劃和調整。實際操作過程中,為了能夠最

大限度的降低高頻元器件線路耗損、降低參數分布復雜性,避免電磁干擾,就要想盡辦法隔開,讓輸入和輸出元件之間存在距離。縮小元器件或導線之間的較高的電位差,避免因放電而造成短路問題。電路調試過程中,若元器件帶有高電壓,則應當盡可能置于不容易碰到的位置。

同時還要注意用支架對其進行有效的固定,若焊接159以上的元器件。則體型相對較大、較沉重的發熱元器件就不能適應印制板,應該被淘汰。這種元器件應該被配置在機箱的底板上。在安裝的同時應該將散熱問題考慮在內。熱敏元件不能靠近發熱元件。

整機的結構要求應首先被考慮,特別是在布局可調節的元件時,比如電位器,開關等。如果是機內調節的情況,那么應被安置在便于調節的區域,比如印制板的上面;如果是機外調節,則需考慮調節旋鈕。

印制板定位孔和固定支架需要的區域首先要騰出。對電路的全部元器件進行分布設置時,要依據其功能單元,因此,要做到以下幾點:1)為了使信號更加流通,要考慮電路的流程,每個功能電路單元要被放置在合理的區域內,這樣也能使信號最大限度在統一的方向上;2)在進行布局時,要緊緊圍繞各個功能電路的核心元件這一核心。元器件在排列時,應注意勻稱、不雜亂、緊密這些原則。連接各元器件之間所用的導線要盡量減少;3)電路在高負荷狀態下運行時,需考慮實際分布狀況。最大限度地使元器件平行分布于電路之中。平行分布可以使外表狀況看上去更好看,方便裝焊,對大量的生產也有很大幫助;4)處于電路板邊緣的元器件,其位置與電路板中心距離不可超過2毫米;對于電路板而言,建議設計成矩形。長是寬的1.5倍。或是1.3倍。

5 常用的EMC設計軟件

PCB板與外部的接口處的電磁輻射是分析時需要考慮的因素。此外,還要考慮PCB板中電源層的電磁輻射以及大功率布線網絡的輻射問題。現在,在設計EMC軟件時已經大量的應用了板級與系統級互連仿真,這兩者主要是建立在Cadence公司的技術上的。同時,SI/PUEMI的模擬分析也被應用于其中。

德國的INCASES公司發明了EMC-WORKBENCH,這一軟件在EMC模擬仿真分析有著重要的推動力。因此,INCASES公司成為行業的領軍者,為EMC的進展做出重大貢獻。EMC-WORKBENCH為設計者提供幫助,特別是在電磁兼容這一技術難點上。同時使得設計過程發生改變,減少了工作量,刪去了一些設計程序。由于EMC模擬仿真技術的應用,因此促使PCB設計快步進入到一個嶄新的時代,尤其是電子工程人員利用該技術可實現短期的高質量、高可靠性設計。在實施EMC模擬仿真分析過程中,必然給電路設計、PCB制造行業的發展帶來更大的機會和更為廣泛的發展空間。實踐中可以看到,一塊電路板可能來自于很多個生產廠家,而且他們的功能性存在著較大的差異,設計人員在對EMC進行分析時,需全面了解元器件的自身特點,讓后方可對其進行具體的模擬仿真操作。該項操作若以傳統的視角來看,似乎是一項非常艱巨的工程,然IBIS SPICE的出現,對EMC問題分析而言,起到了非常大的促進作用。

6 結束語

總而言之,在PCB實際設計過程中,一定要嚴格按照相關設計規范進行,要符合抗干擾設計之原則和要求,只有這樣才能使電子電路處于最佳的性能狀態。PCB設計初期階段,需要對布線中的問題進行全面的考慮,這樣才能有效減少設計周期,提高設計質量。

電子發燒友App

電子發燒友App

評論