一、簡介 RapidIO是由Motorola和Mercury等公司率先倡導的一種高性能、 低引腳數、 基于數據包交換的互連體系結構,是為滿足和未來高性能嵌入式系統需求而設計的一種開放式互連技術標準

2020-11-26 10:42:37 3561

3561

`xilinx公司的rapidio接口定義具體的核引腳定義,比如什么用,時序等。接口見附件圖1~圖4.`

2016-10-28 22:01:48

有哪些方法能提高2.4G 單面板的性能, 增強抗干擾能力和傳輸距離等?

2016-11-11 13:51:47

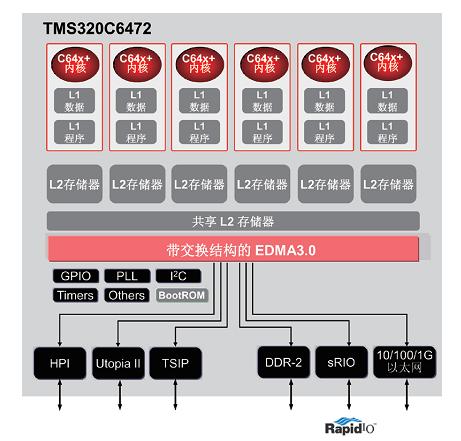

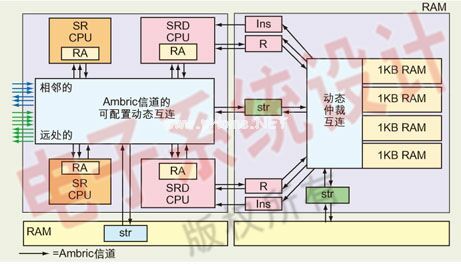

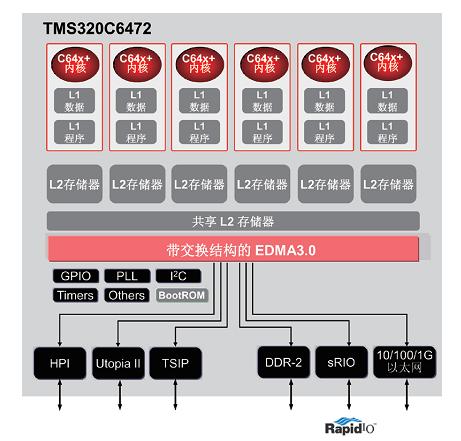

可能隱含BUG)如何充分使用八核的性能?如何對八核進行調試、監控?復雜的系統中,幾十個DSP核如何進行簡單、高效的通信C6678 多核 DSP 軟件 開發難點共享外設:與C64x單核DSP相比,芯片

2018-06-20 01:39:59

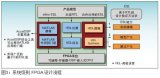

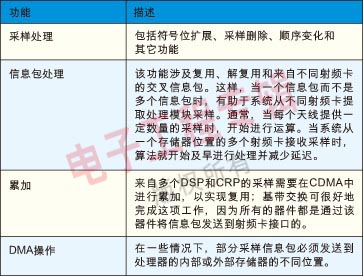

FPGA在高性能數字信號處理領域越來越受關注,如無線基站。在這些應用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統設計師需要一個確切的FPGAs及高端DSP信號處理器性能參數圖。不幸的是,常用的參數圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

為設計提供可編程邏輯解決方案所固有的靈活性特點,以及定制門陣列(如ASIC)解決方案所具有的高性能及集成度。 增強DSP處理能力的傳統方法是采用多個處理器。選擇此類方案的缺點是成本昂貴,需要眾多附加

2011-02-17 11:21:37

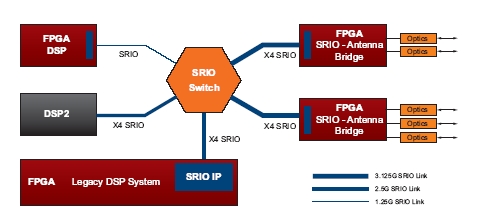

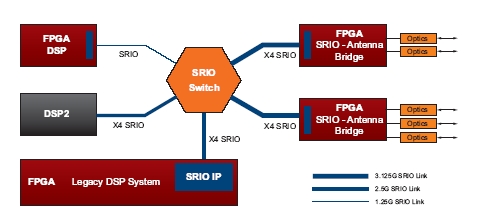

多;主從模式接口,不支持對等傳輸。另外,DSP不能直接進行背板傳輸。使用SRIO(Serial RapidIO)則可有效的解決這些問題,大大提高無線基站的互連性能。圖8顯示了一種無線基站基帶互連框圖

2016-12-09 11:24:30

本人在北京工作7年以上,從事FPGA外圍接口設計,非常熟悉Serial RapidIO協議,設計調試了多個基于Serial RapidIO接口的DSP和PowerPC信號處理卡.本人非常

2014-08-23 13:27:47

性能中傳輸研究和對速度快速提高所致。而且主動減振系統和VoIP也伴隨DSP性能提高而開發出來。DSP架構中性能提高也促進了蜂窩電話和DSL發展。這些發展進一步降低了便攜系統設備功耗,同時也為多信道系統

2011-05-27 10:18:02

`Spartan-3ADSP現場可編程門陣列系列(FPGA)解決了大多數高容量的設計難題,成本敏感的高性能DSP應用。這兩人家庭提供的密度從1.8到3.4百萬系統門,如表1所示。Spartan-3A

2021-04-26 15:07:49

最先進的高性能邏輯架構之外,Virtex-5 FPGA包含許多硬IP系統級塊,包括功能強大的36 Kb塊RAM / FIFO,第二代25 x 18 DSP片,具有內置數字控制阻抗的SelectIO

2021-04-26 15:41:14

(HKMG)工藝技術之上,可實現I / O帶寬2.9 Tb / s,200萬邏輯單元容量和5.3 TMAC / s DSP極大地提高了系統性能,而功耗卻降低了50%7系列FPGA功能摘要?基于可配置為

2021-04-13 14:27:32

fpga+dsp 4路ad采集系統,you嘗,rapidio pcieddr3 各種高速外圍接口 代碼有償。qq2715957785

2018-02-24 08:34:21

定的綁定。由于有兩種 Rapidio 發射器類型(長跑和短跑),我們猜測將發射器配置為長跑可能會提高信號質量,但不幸的是我們沒有找到合適的寄存器,順便說一句,我們使用 MPC8569。我的問題:是否有配置 Rapidio 變送器類型的寄存器?或者是否有一些與硬件設計相關的問題可能會導致我們的問題?

2023-03-16 08:37:11

關于FPGAs的DSP性能分析

2021-05-07 06:12:50

多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到較大幅度的提高。DSP處理器由于其具有較高的數字處理能力,得到較廣泛的應用。多核DSP芯片以目前

2021-02-02 07:53:47

通過陣列天線后產生不同的陣列響應,智能天線接收系統可采取一定的算法(可在射頻、中頻或基帶實現)把不同方向的信號區分開來,從而降低干擾,提高系統性能。因此陣列結構對智能天線系統性能起著重要的影響。[hide][/hide]

2009-07-29 08:54:14

提高48V配電性能的方法有哪些分比式電源架構

2020-11-23 14:29:09

提高 48V 配電性能

2021-03-16 06:36:28

如何提高FATFS SD性能?

2022-02-11 06:28:46

本文基于Viitex-5 LX110驗證平臺的設計,探索了高性能FPGA硬件系統設計的一般性方法及流程,以提高FPGA的系統性能。

2021-04-26 06:43:55

如何提高VMMK器件的性能?

2021-05-21 06:35:39

無論您的系統是用于無線通信、雷達,還是 EMI/EMC 測試,系統的性能水平都是由其中的天線決定的。系統天線的性能決定了系統的整體質量,最終可能會影響整個程序或應用軟件的效率。本文介紹了 5 個旨在幫助您提高天線性能的關鍵要點。

2021-02-24 07:24:14

元器件的合理布局提高敏感器件的抗干擾性能

2021-02-19 07:05:29

自適應電纜均衡器是什么?自適應均衡器設計面臨哪些技術挑戰?如何提高自適應均衡器的性能?

2021-05-18 06:04:25

我正在使用 iMX8mmini 并嘗試提高 GPU 性能。使用下面的命令我發現當前 GPU 以 500 MHz 的頻率運行。根據數據表或設備樹節點,GPU 以 800 MHz 的標稱頻率運行(最大

2023-04-18 07:17:15

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

如何去提高語音引擎設計的質量和性能?

2021-05-31 06:35:46

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-11-01 06:05:21

最大限度提高Σ-Δ ADC驅動器的性能

2021-01-06 07:05:10

我用ise產生了rapidio的核,然后做功能仿真沒有問題,我把自己的邏輯與核結合起來后做功能仿真,卻發現端口不能初始化了,具體情況是port_initialized變成了不定值。求幫忙!!

2019-05-16 09:39:16

怎么使用PlanAhead Design工具提高設計性能?

2021-04-26 06:00:22

您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2019-08-15 07:51:10

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-09-02 07:10:22

本文設計了一套基于DSP的陣列聲波信號采集與處理系統,此系統將作為正在研制的陣列聲波測井儀中的一部分,應用于油田勘探中。

2021-05-31 06:26:35

嗨,我有一個ML605板和一塊使用RapidIO協議的DSP板。該板有兩個FMC連接器(HPC和LPC)和一個PCIe接口,我需要4個萬兆收發器(MGT),PCIe和FMC HPC都有8個(LPC

2019-08-29 10:33:02

之前做ARM軟件開發,現在轉DSP軟件開發,特別對DSP性能,內存利用難以把控,論壇上硬件資料偏多,誰有軟件方面資料,特別關于性能優化的,多謝。

2013-08-17 21:33:47

熱量是如何產生并影響LED的?如何提高LED性能?

2021-06-15 09:02:39

近來,Altera公司推出業界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設計人員的效能和邏輯效率。據悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

實驗。本文提出了一種新型的碳納米管天線陣列研究方法,即采用傳統微帶天線和印刷八木天線分別加載碳納米管束的方法對納米管陣列進行空間饋電并進行了實驗測試,測試結果表明加載碳納米管陣列后微帶天線輻射性能有明顯改變。

2019-05-28 07:58:57

如何提高系統的ADC的性能?

2019-09-06 05:55:37

討論一下編程風格與技巧是怎樣提高設計性能的?

2021-05-07 06:31:21

的時候用的是默認32位地址。我想請問一下,如果要利用srio收發34位地址,DSP端keystone_srio的程序要做什么改進?我看了keystone_srio初始化代碼,它的PE_LL_CTL

2018-12-28 11:08:14

在布板時,如果線密,過孔就可能要多,當然就會影響板子的電氣性能,請問怎樣提高板子的電氣性能?

2019-06-25 04:08:22

在可編程邏輯中實現可配置軟核處理器有哪些好處?怎樣建立起處理器和主機pc之間的通信?怎樣用DSP功能去提高圖像處理?

2021-04-14 06:52:33

請問有什么策略可以提高芯片的性能?

2021-06-23 13:08:50

調試并行RapidIO設計

2019-07-17 09:11:20

路LED的智能控制,提高車用LED的工作效率和可靠性,可以廣泛應用于車用LED控制領域。【關鍵詞】:傳感器陣列;;LED;;智能控制【DOI】:CNKI:SUN:GGYT.0.2010-08-009【正文

2010-05-28 13:39:17

近年來變頻控制因其節能、靜音及低顫動而得到廣泛的關注和應用,基于ARM/DSP 的高性能驅動方案為中大功率三相電機提供了高性能、多控制方式的解決方案,其主要應用于對電機控制的性能、實時性方面要求比較

2019-07-09 08:24:02

有哪些新型可用于基帶處理的高性能DSP?性能參數如何?

2018-06-24 05:20:19

高級處理器特性能否提高編碼效率?

2021-04-26 06:41:08

陣列通道幅相不一致性嚴重影響測向性能。基于輔助源的相關校正理論,研究了通過在天線饋電口輸入輔助信號,再對信號求相關來實現對陣列通道不一致性的校正;并分析了基

2009-03-04 22:23:07 21

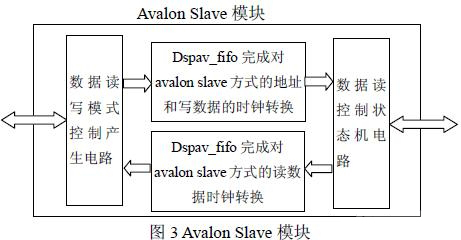

21 針對傳統總線PCI存在的問題,提出異步FIFO存儲轉發模式的串行RapidIO-PCI轉接橋方案,介紹RapidIO高速總線的體系結構及其性能優勢,根據PCI和RapidIO協議,給出轉接橋關鍵部分結構的設

2009-04-01 09:34:02 33

33 基于DSP的多傳感器陣列數據采集與處理試驗平臺

2009-05-08 17:10:52 17

17 賽靈思宣布開始向市場交付針對高性能數字信號處理(DSP)而優化的65 nm Virtex-5 SXT現場可編程門陣列(FPGA)器件的首批產品。SXT平臺創造了DSP性能的行業新紀錄--550MHz下性能達352 GMAC

2009-11-28 14:08:02 23

23 為了在實驗室中獲得短波天線陣列信號,應用DSP芯片和DUC芯片(數字上變頻器)設計了一個實用電路短波陣列信號發生器,模擬實現了短波九元天線陣的多種陣型、不同來波方向及存在

2009-12-03 16:44:08 17

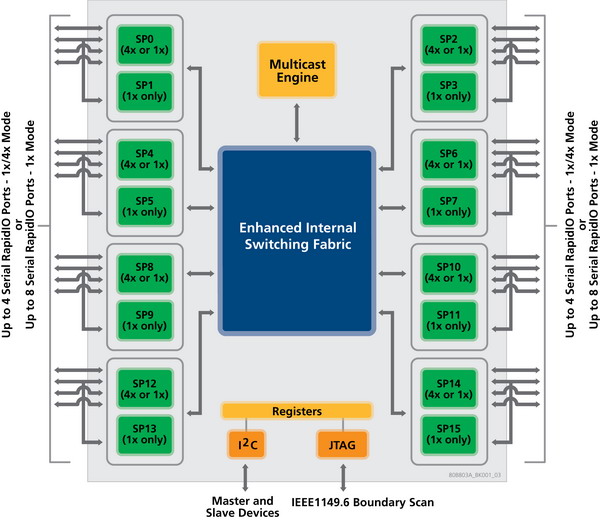

17 RapidIO 互連構架是一個開放的標準,可應用于連接多處理器、存儲器和通用計算平臺。本文簡要介紹了基于Tundra 公司TSI568 芯片的RapidIO 交換模塊的設計原理和實現方法,并對一些

2010-01-06 16:47:48 40

40 本文首先簡單的介紹了總線的發展,從而引出一種新型的串行點對點交換結構RapidIO。DSP 在高性能處理系統中的重要性毋庸置疑,但是目前的很多DSP 并沒有RapidIO接口。本文提出了

2010-01-25 14:25:19 32

32 前言 聲源定位追蹤模組AR-1105是德宇科創采用最新的DSP音頻處理器集成麥克風陣列聲源定位追蹤技術進行研發,模組具有全硬件集成.體積小巧,外圍電路簡潔,無需軟件調試,易上手等優點的情況下同時保持反應靈敏,定位準確等特性. 總結

2023-09-02 09:32:13

分析當前高速互連網絡中同時存在的TCP/IP, GAMMA, InfiniBand, SCI 等技術的實現機制,介紹RapidIO 高性能總線技術。研究RapidIO 協議和MPC8548 處理器的相關技術,提出在RapidIO 高速互連網

2010-09-22 08:35:11 20

20 傳統嵌入式應用設計通常是將程序直接固化到DSP內部的Flash存儲器運行,程序運行效率較低,不能充分發揮DSP的性能。為克服這些缺點,解決嵌入式應用程序在Flash存儲器直接運行所

2010-12-27 15:34:48 25

25 首款串行RapidIO 2.1 IP 解決方案(Altera)

Altera 公司 宣布推出業界首款支持 RapidIO® 2.1 規范的知識產權 (IP) 內核。Altera 的串行 RapidIO IP 內核可支持多達四條通道,每條通

2009-11-18 15:50:59 890

890 光伏陣列的性能測試

1.組裝工藝質1檢查

對于光伏電池板和光伏陣列的組裝工藝檢查主要是檢查其外觀質量

2009-12-19 08:54:58 3711

3711 6核片上DSP陣列提高平臺整體性能

DSP的新走向是業界十分關心的問題。曾經對DSP的需求是強調性能和頻率。目前時鐘頻率已經向1G以上突破,這樣的情況下如何保持產

2010-01-06 14:12:49 570

570

串行 RapidI 高性能嵌入式互連技術

摘要

串行RapidIO針對高性能嵌入式系統芯片間和板間互連而設計,它將是未來十幾年中嵌入式系統互連的最佳選擇。

2010-02-25 16:45:04 1022

1022

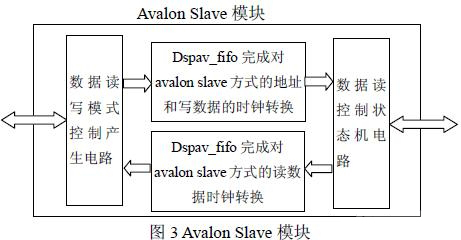

基于FPGA實現DSP與RapidIO網絡互聯

1. 引言

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首

2010-02-25 16:46:46 868

868

全球首屈一指的RapidIO IP解決方案

RapidIO最早是由美國Mercury Computer systems公司(美國水星計算機系統公司www.mc.com)為它的計算密集型信號處理系統自行開發的總

2010-03-01 11:05:21 882

882 串行RapidIO交換器的應用優勢

EMIF6? 是由 Texas Instruments 開發的一款專利接口,在業內應用多年,反響良好。但是,EMIF6? 現正用于從未嘗試的 DSP 至 DSP 連接等應用。本文

2010-03-03 15:54:10 795

795

采用串行RapidIO連接功能增強DSP協處理能力

目前,對高速通信與超快計算的需求正與日俱增。有線和無線通信標準的應用隨處可見,數據處理架構每天都在擴展。較為普

2010-03-03 16:01:25 1134

1134

利用串行RapidIO交換機設計模塊化無線基礎系統

無線服務提供商期望引進的無線基礎系統具有更高的性能以及更低的成本,這將推動對標準的或現成元件不斷提高的

2010-03-09 12:05:10 1033

1033

IDT公司宣布,推出基于其業界領先Serial RapidIO 1.3交換器的全新Serial RapidIO Gen2交換器系列。這些新的交換器支持Serial RapidIO 2.1標準,利用了來自IDT CPS和TSI產品線的一流技術。

2010-06-28 08:33:31 1721

1721 RapidIO總線的出現及其體系結構和應用

傳統總線多采用并線總線的工作方式,這類總線一般分為三

2010-12-06 10:16:37 2069

2069 摘要:從應用角度介紹了ADSP21160 DSP芯片的基本性能,并用ADSP21160實現了基本的陣列信號測向算法-MUSIC算法著重討論了如何利用ADSP 21160的結構和開發環境來提高程序的執行效率,滿足系統設計的要求。 關鍵詞:SHARC DSP;陣列信號處理;MUSIC;測向算法

2011-02-28 23:59:15 33

33 該方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系統,并對其功能進行驗證。詳細分析了RapidIO應用系統及其驗證模型的功能結構和運行原理,為提高嵌入式

2011-12-23 14:47:22 38

38 介紹了RapidIo總線的特點,以及RapidIo總線初始化過程中面臨的系統網絡結構探測和最短路徑路由選擇問題。針對該問題,本文研究了深度優先(DFS)網絡拓撲探測方法在RapidIo總線枚舉過

2013-03-13 16:15:14 74

74 基于串行RapidIO的Buffer層設計_任雪倩

2017-01-07 21:28:58 0

0 威世-用薄膜電阻陣列提高反饋電路和分壓器的精度

2017-01-24 16:00:51 8

8 基于EP2C35的DSP陣列板通信接口設計與實現

2017-10-19 14:12:34 14

14 摘 要:本文分析了傳統的多個DSP 的各種互聯的方法,提出將串行RapidIO 協議,這種基于開關的、點對點的互連方法作為基帶數據處理中的互連方案,可以減少成本,并且提供高帶寬下低延時的雙向通信

2017-10-21 09:29:51 1

1 您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2018-07-17 11:48:00 710

710

高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 3784

3784 運行。這種運行方式在傳統嵌入式應用設計中很有效,但在一些算法比較復雜、系統響應要求快速、通訊任務比較繁重的嵌入式應用中,這種運行方式會導致控制系統響應遲緩、通訊異常、I/O操作緩慢等問題。針對這些情況,提出一種新的解決方案,來提高DSP代碼運行性能。

2019-08-07 08:12:00 2126

2126

srio_example_top_primary,它代表請求方的RapidIO設備;另一個例子設計頂層叫做srio_example_top_mirror,它代表響應方的RapidIO設備。

2022-12-19 10:33:51 1190

1190 RapidIO互連架構,與目前大多數流行的集成通信處理器、主機處理器和網絡數字信號處理器兼容,是一種高性能、包交換的互連技術。它能夠滿足高性能嵌入式工業在系統內部互連中對可靠性、增加帶寬,和更快的總線速度的需求。

2023-01-09 09:25:20 751

751 RapidIO 與傳統嵌入互連方式的比較 ????隨著高性能嵌入式系統的不斷發展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器總線、PCI總線和以太網,都難以

2023-02-02 14:15:05 356

356 Serial RapidIO Development Platform (SRDP2) 原理圖

2023-05-15 19:19:49 0

0 Serial RapidIO Development Platform (SRDP2) 原理圖

2023-07-11 20:31:35 0

0 RapidIO交換芯片是一種基于RapidIO協議的專用交換芯片,它能夠實現高速、低延遲的數據傳輸和交換,廣泛應用于嵌入式系統、數據中心、網絡通信等領域。RapidIO協議本身是一種基于包交換的互連技術,具有高速、高效、可靠等特點,因此RapidIO交換芯片在數據傳輸和交換方面具有很高的性能優勢。

2024-03-16 16:40:09 1532

1532

電子發燒友App

電子發燒友App

評論