本實驗工程將介紹如何利在賽靈思異構多處理器產品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式評估板上實現多個 UIO,同時借助賽靈思的工具完成硬件工程和 linux BSP 的開發,最后通過測試應用程序完成測試。

2018-02-26 09:52:53 7957

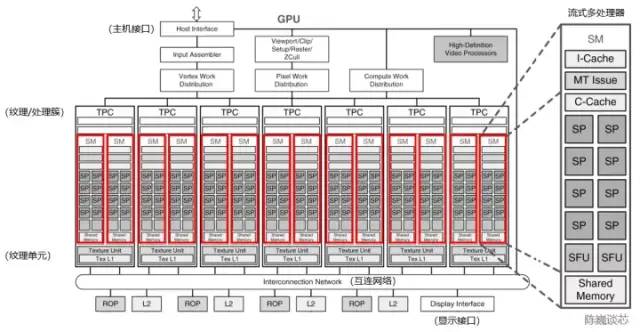

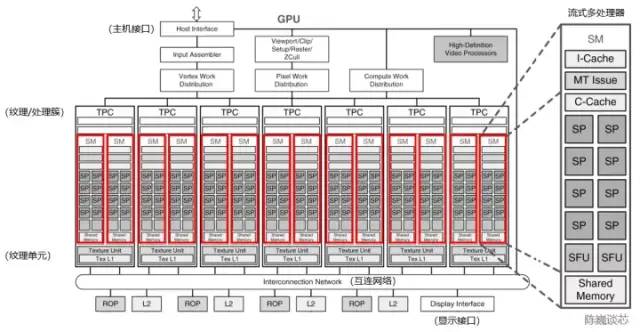

7957 流式多處理器(Stream Multi-processor,SM)是構建整個 GPU的核心模塊(執行整個 Kernel Grid),一個流式多處理器上一般同時運行多個線程塊。每個流式多處理器可以視為具有較小結構的CPU,支持指令并行(多發射)。

2023-03-30 10:14:24 597

597 專注于引入新品并提供海量庫存的電子元器件分銷商貿澤電子 (Mouser Electronics)即日起備貨Xilinx的Zynq? UltraScale+ 多處理器片上系統 (MPSoC)。

2019-11-25 15:28:48 1102

1102 Teledyne e2v為系統設計師提供的定制方案處理器功耗的背景知識三種調整處理器系統功耗的方法

2021-01-01 06:04:09

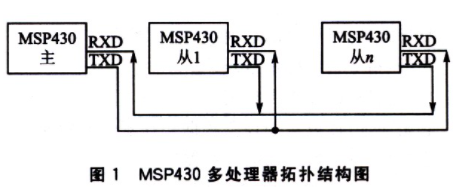

多處理器通信和LIN模式區別是什么?

2021-12-08 07:32:14

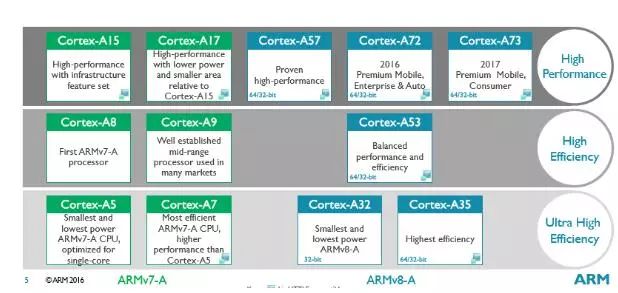

Cortex-A15 MPCore處理器是一款高性能、低功耗的多處理器,采用ARMv7-A架構。

Cortex-A15 MPCore處理器在具有L1和L2緩存子系統的單個多處理器設備或MPCore設備中具有一到四個Cortex-A15處理器。

2023-08-17 07:37:22

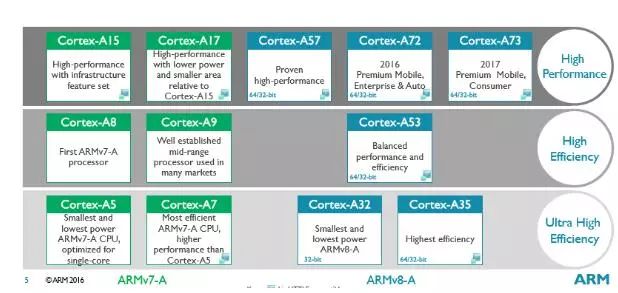

ARM Cortex系列那么多處理器,該怎么區分?

2020-05-29 13:43:08

耳內監聽),以及非常高的、超過 2 600 倍Dhrystone 2.1 標準(測 量處理器的運算能力標準)MIPS(百萬條指令/每秒)性能的多處理器技術。上面對幾個 ARM 處理器內核做了簡單的介紹

2019-09-27 09:28:51

很多處理器通信,即將幾個USART連接在一個網絡里。比如某個USART設備可以是主機,它的TX輸出和其他USART從設備的RX輸入相連接;USART從設備各自的TX輸入輸出與本地,并與主設備的RX輸入

2023-04-28 16:24:14

CM3之STM32如何實現多處理器通信

2015-09-17 10:11:58

本帖最后由 一只耳朵怪 于 2018-5-25 14:55 編輯

DM6446內核有三種頻率,有三種處理速度;這個速度和頻率是對應的嗎?由什么決定?最多可以接多少個TVP5146(單片傳輸速度不夠)?

2018-05-25 06:47:06

在現代操作系統里,同一時間可能有多個內核執行流在執行,因此內核其實象多進程多線程編程一樣也需要一些同步機制來同步各執行單元對共享數據的訪問。尤其是在多處理器系統上,更需要一些同步機制來同步不同處理器上的執行單元對共享的數據的訪問。

2019-08-06 07:08:12

自旋鎖是專為防止多處理器并發而引入的一種鎖,它在內核中大量應用于中斷處理等部分(對于單處理器來說,防止中斷處理中的并發可簡單采用關閉中斷的方式,即在標志寄存器中關閉/打開中斷標志位,不需要自旋鎖)。

2020-03-31 08:06:08

普遍認為開發多處理器系統軟件的難度要大于單處理器系統。但實際情況并非總是如此。我們這個在 TRW 汽車公司下屬的咨詢部 TRW Conekt 工作的設計團隊最近接管了一個項目,展示了如何根據手中的問題發揮硬件的功能,并通過使用許多個處理器開發出高效系統。

2019-10-23 08:00:03

STM32內核處理器好用嗎

2015-09-02 19:38:10

我想運用生成即保證正確(correct-by-construction)規則設計多處理器混合關鍵性系統,請問生成即保證正確(correct-by-construction)規則可用嗎?在什么情況下可用?

2016-02-17 16:18:34

相結合,來實時地完成某一特定任務。隨著信號采集速度和處理速度的要求越來越高,許多領域都需要進行多處理器運算,其中包括醫學、圖像處理、軍事、工業控制、電信等許多領域。多處理器系統可以根據所需實現的功能

2019-06-27 06:48:18

dlpc3439只有紅綠藍三色的顯示接口,很多處理器沒這個接口了。怎么辦?

只能選有這個接口的處理器嗎?

2018-06-23 07:38:45

我使用的開發板是HPM6750MINI,我想讓HPM6750工作在雙核模式。為何我在RT-Thread Settings中打開對稱多處理器會報錯:報錯內容:error: conflicting

2023-02-07 10:39:17

很多處理器的生產成本小于一美元。更大潛在的成本是當從處理器與主處理器不同時所需開發工具的成本。一個好的設計團隊,會選擇一個可以滿足很多多處理器設計需求的從處理器,因此工具的消耗就可以分散在很多設計中

2018-12-06 10:20:18

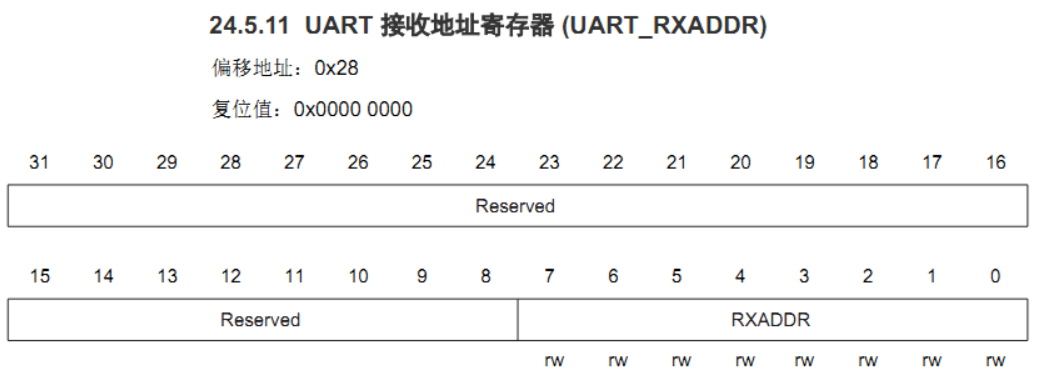

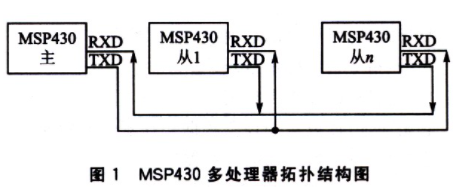

什么是MSP430多處理器?MSP430多處理器有哪些技術要點?

2021-05-27 06:52:20

STM8多處理器通信是什么

2020-11-12 06:27:01

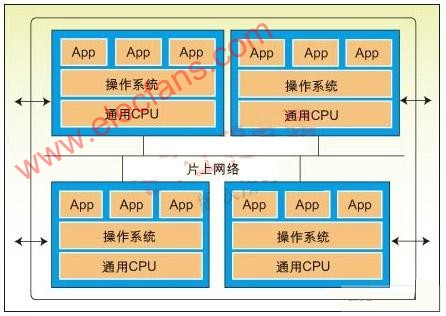

本文將對基于NiosII的SOPC多處理器系統的實現原理、設計流程和方法進行詳細的討論。

2021-04-19 08:51:23

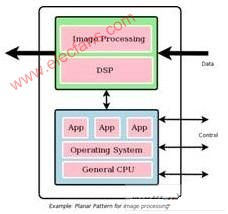

本文提出了一個通用微處理器(ARM)與DSP的接口設計方案,以實現兩者的實時通信。

2021-06-08 06:36:41

本文提出了一種基于TMS320C6701信號處理器的高性能信號處理模塊的設計方案,設計了具有一定通用性的并行信號處理模塊,該模塊具有高速互連接口,可以根據應用系統的需求構成不同的并行系統,完成各種信號處理任務。

2021-04-02 07:30:14

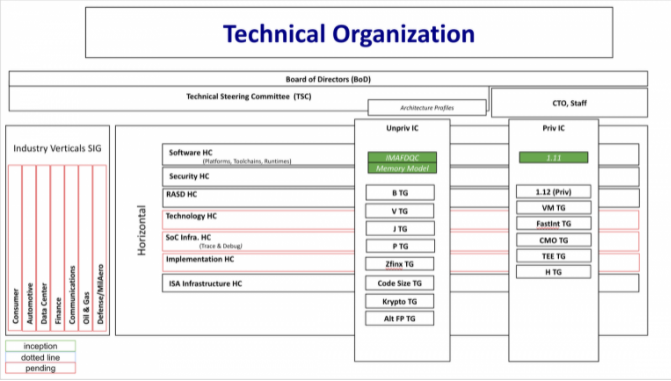

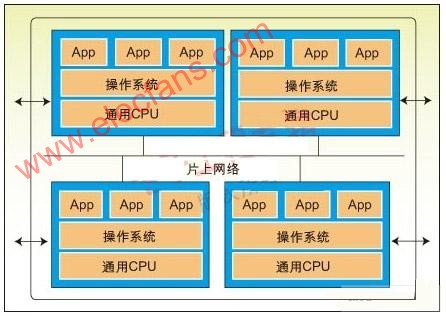

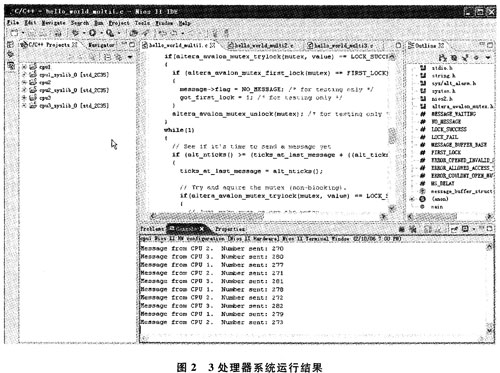

隨著嵌入式處理需求的快速增長,系統架構正朝著多處理器設計的方向發展,以解決單處理器系統復雜度太高和計算能力不足的問題。憑借其高邏輯密度及高性能硬模塊,新一代FPGA已經使功能強大的芯片多處理(CMP

2019-08-01 07:53:43

多核處理器分類方式有很多種,其中一種比較常見的是按照存儲器組織方式分類。第一類就是一致存儲器訪問(Uniform Memory Access,簡稱UMA)多處理器,所謂的“一致”是指所有處理器訪問

2022-06-07 16:46:44

I2C的工作原理是什么?一種基于I2C總線的處理器的聯網設計方案

2021-06-01 06:25:49

我想在多處理器系統中使用 EMIF。 為此,應不時將地址和數據總線設置為高阻抗狀態。 可能嗎? 我找不到圖紙中連接 EMIF 總線的位置? 直接連接到 PIN 或

2024-03-05 06:51:37

藍牙無線組網的優點是什么?常見的三種無線接入方式是什么?藍牙無線組網原理與上網方案分享

2021-05-26 06:33:11

求一種多處理器并行計算機系統的設計方案

2021-04-27 06:58:57

協議用于維護由于多個處理器共享數據引發的多處理器數據一致性問題。論述了一個適用于64位多核處理器的共享緩存設計,包括如何實現多處理器緩存一致性及其全定制后端實現。本文介紹了一種共享高速存儲器模塊

2021-02-23 07:12:38

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

討論了一種基于FPGA的64點FFT處理器的設計方案,輸入數據的實部和虛部均以16位二進制數表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發平臺對處理器各個的模塊進行設計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結果正確。

2021-04-29 06:25:54

求一種基于RK3288 Cortex-A17四核處理器的政務服務一體機硬件設計方案

2022-03-03 12:59:57

求一種基于FPGA芯片的嵌入式PLC處理器的設計方案。

2021-05-06 08:24:19

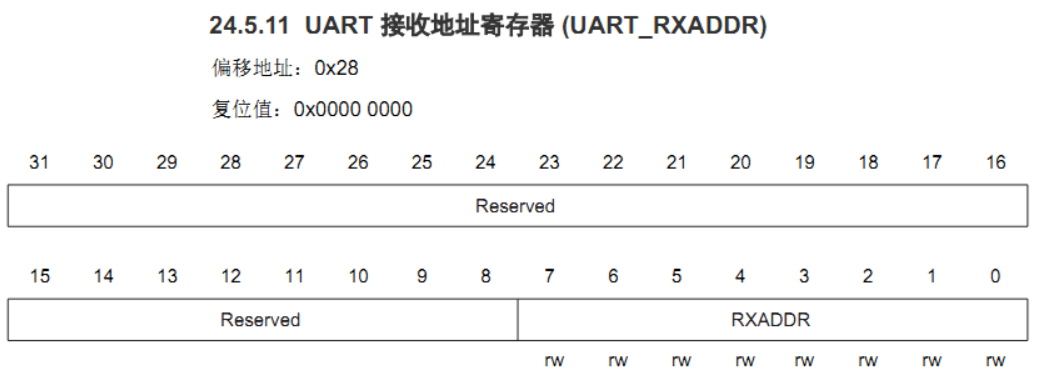

的WAKE位狀態,UART多處理器通信有二種方法進入或退出靜默模式分別是:WAKE 位被設置0:進行空閑總線檢測。WAKE 位被設置1:進行地址標記檢測。空閑總線檢測空閑幀喚醒可以同時喚醒所有從機,在從機

2020-12-04 16:52:53

片上Nios Ⅱ嵌入式軟核多處理器系統具有哪些優勢?如何實現片上嵌入式Nios Ⅱ軟核六處理器系統的設計?

2021-04-19 08:17:09

原子哥,論壇上的大神們,有做過串口的多處理器通信么?如果有,大家是用空總線檢測還是用地址標記的方式啊?

2019-09-05 04:35:13

機群系統已成為高性能計算的主流體系結構,機群模擬環境是學習機群操作的重要工具。該文提出一種基于龍芯2E多處理器硬件平臺的機群模擬方案——虛擬機群系統(VCS)。該系統在

2009-04-23 09:39:26 11

11 本文提出了一種全新的總線可重配置的多處理器架構。該架構結合了多核與可重配置處理器的優勢,具有并行性高、計算能力強、結構復雜度低并且應用領域廣泛靈活的特點。對

2009-06-13 14:11:04 11

11 定義了一種完全基于局部處理器的多處理器系統,討論了系統的實現條件,提出了一種共享總線結構,建立了處理器域之間基于固定地址窗的信息交換機制,實現了無主多處理器

2009-06-15 08:57:52 11

11 分析了Intel-21554 非透明橋的結構特點,建立了利用LookupTable 基地址模式實現多處理器地址窗的映射機制,描述了實現所述地址映射的詳細過程,提供了利用標準非透明橋實現無主多

2009-08-24 10:09:46 16

16 SoC技術的發展使多個異構的處理器集成到一個芯片成為可能,這種結構已成為提高微處理器性能的重要途徑。與傳統的多處理器系統一樣,Cache一致性問題也是片內異構多處理器系統

2009-09-26 15:02:01 11

11 多處理器實時調度理論是目前實時系統的關鍵技術。論文研究了PFair 調度算法在多處理器中的調度理論,在此基礎上,提出了一種基于PFair 調度算法的處理器分組調度算法。該算

2009-12-18 15:38:02 11

11 基于NiosII的SOPC多處理器系統設計方法

兩個或多個微處理器一起工作來完成某個任務的系統稱為“多處理器系統”。傳統基于單片機的多處理器系統

2009-10-17 09:28:42 1069

1069

滿足多媒體需求,便攜電子風行多處理器架構

隨著多媒體應用要求越來越高,在小小的行動裝置內,除了要有即時動態影音呈現,又必須處理大量圖型化

2009-12-15 10:30:02 639

639 多媒體手機在滿足傳統語音通信的同時還必須提供穩定、高質量的多媒體表現,傳統的單處理器方案不能滿足這些并行任務的處理能力要求,采用具有視頻、Java和安全專用硬件加速器的多處理器引擎系統級芯片能有效解決這些多媒體任務要求,并能有效降低系統功耗。

2011-02-25 11:01:21 82

82 嵌入式處理器分類 處理器造型需考慮的因素 多處理器在復雜系統中的應用

2011-02-28 11:57:26 64

64 摘要:提出一種嵌入式異構多處理器系統的結構模型,論述這種系統的通信機制,并闡述在基于這種嵌入式異構多處理器系統模型的實時圖像處理系統中,運算節點采用由TI公司的TMS320C6416 DSP芯片構造的信號處理板時,在運算節點與主控節點之間實現高速數據傳輸的

2011-03-01 01:34:01 47

47 本篇論文采用微核心架構在異質性多處理器上建構核心,經由在不同處理器上執行相同設計之核心以提供上層應用程式統一的介面。上層應用程式可依據其所在處理器的特性執行相對應的報務等待其它應用程式的請求。藉由在不同處理器上執行相同核心以及不同特性的應

2011-03-01 13:40:11 23

23 本文提出了當多處理機系統工作時,為了實現快速有效的通信,采用使多處理器共享存儲器方案。IDT7134雙口RAM是本方案選擇的共享存儲器。針對該方案,本文給出了接口電路的硬件設計

2011-04-27 11:20:38 28

28 人們一般希望用一個處理器來處理整個系統,但有的時候加入一個新的處理器將是一個很好選擇。盡管使用多處理器會帶來一些成本增加,但多處理器把任務劃分開可簡化設計,并加快

2011-05-25 17:29:11 28

28 一個大型復雜系統往往有多個處理器,處理器間要協同工作依必須交換數據。給出基于存儲體共享的處理器交換數據的三種方法,即:基于雙口RAM 的方法、基于單向或雙向FIFO 的方法、

2011-07-18 15:27:21 39

39 怎樣使用Nios II處理器來構建多處理器系統 Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 基于I2C總線的處理器的聯網設計方案

2017-01-26 11:36:55 11

11 。不過,很多裸機應用和更為簡單的操作系統只使用Zynq SoC 處理系統(PS)中兩個ARM 內核中的一個,這種設計方案可能會限制系統性能。

2017-11-17 18:16:37 5950

5950

使用多處理器內核要求軟、硬件團隊之間進行更多的系統級設計合作。基于這種理念,下面是對采用當前開發工具和硬件直接實現多內核系統的三個簡單模型的概述。這些多內核設計模式不是一個為了嚴格定義一個系統的剛性

2018-07-15 11:21:00 3058

3058

智能化賦予了物聯網更深刻的實用價值,但是在計算能力強與功耗低的之間尋求性能最優是目前物聯網設備極難解決的問題.異構多處理器結構與單一或者同構的多處理器相比可以結合不同處理器的優勢,同時滿足高計算能力

2017-12-19 15:06:56 0

0 針對多處理器系統中隨機到達的任務,設計了可靠性約束下的節能調度算法( ESACR)。該算法在滿足任務截止期限的前提下選擇一個預計產生能耗最小的處理器以節能,在單個處理器上運用最早截止期限優先策略進行

2018-01-08 14:20:44 0

0 隨著多處理器實時系統在安全性攸關系統中的廣泛應用,保證這類系統的正確性成為一項重要的工作.可調度性是實時系統正確性的一項關鍵性質.它表示系統必須滿足的一些時間要求.傳統的可調度性分析方法結論保守或者

2018-02-06 16:46:37 0

0 對于一個具有多個CPU的多處理器系統,在單板或系統中的一個或多個設備中,CPU和內核有時可以相互作用或依賴于其他CPU或內核的動作。單個設備上的多個內核甚至共享一個普通的內存塊,其中包含可執行代碼或SysDeDATA。因此,經常需要調試多個CPU或多個內核,同時嘗試調試提供處理器間通信的代碼。

2018-04-25 15:36:51 8

8 利用Visual DSP++4.0多處理器調試器可在硬件平臺上對用戶系統進行全面的程序測試和評估.同時支持I/0處理器間的通信和MMS數據傳輸。TigerSHARC DSP多處理器系統可以配置

2019-02-25 11:08:27 7

7 同步多處理器,英文為Synchronous Multi-Processors,縮寫為SMP。同步多處理器系統在工作的時候,每當一個任務完成后,空閑的處理器會立刻尋找下一個新的任務,對于外部而言,這兩顆處理器是一個整體,共同完成同一個工作。

2020-06-02 09:16:17 903

903 MM32F013x系列MCU支持UART多處理器通信,其工作原理是主從機設備采用復用漏極開路,主從機外部接上拉電阻,在空閑時使從機處于靜默模式,主機要控制從機執行任務時主機發送指令喚醒從機并發送數據控制從機執行相應任務。

2022-02-21 10:05:22 950

950

MM32F013x系列MCU支持UART多處理器通信,其工作原理是主從機設備采用復用漏極開路,主從機外部接上拉電阻,在空閑時使從機處于靜默模式,主機要控制從機執行任務時主機發送指令喚醒從機并發送數據控制從機執行相應任務。

2021-01-22 06:33:51 6

6 ADSP-BF561:Blackfin嵌入式對稱多處理器數據手冊

2021-03-21 06:39:02 9

9 AD14160:Quad-SHARC?DSP多處理器系列過時產品手冊

2021-04-15 19:13:10 4

4 AD14060/AD14060L:Quad-SHARC?多處理器DSP系列產品手冊

2021-04-25 19:23:54 1

1 EE-202:使用多處理器LDFS的專家鏈接器

2021-05-14 09:22:30 2

2 EE-167:使用VisualDSP++?的TigerSHARC?多處理器系統簡介

2021-05-27 18:39:07 11

11 AD14160 Quad-SHARC?DSP多處理器系列過時數據表

2021-06-16 15:31:36 4

4 在單片機系統中,多處理器是指多個相同類型或者不同類型的單片機協作處理同一個系統的不同工作。它們之間必須具備一定的數據交換和協作處理能力,共同完成一個系統化的工作。不同處理器之間可以采用數據交換方式

2021-06-17 15:41:58 1751

1751

在上一次的靈動微課堂中和大家分享過MM32F013x-UART 9bit通信實例,本次微課堂在此實例的基礎上實現UART多處理器通信。MM32F013x系列MCU...

2022-01-25 19:55:23 4

4 riscvOVPsim 的可用升級包括虛擬平臺開發和仿真、多核軟件開發、可擴展平臺套件和多處理器主機 (MPonMP) 加速軟件上的 QuantumLeap 多處理器目標。

2022-06-21 09:40:21 712

712

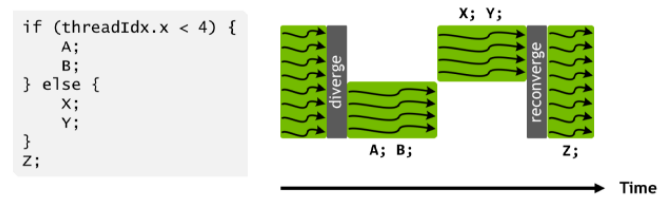

按照軟件級別,SIMT層面,流式多處理器由線程塊組成,每個線程塊由多個線程束組成;SIMD層面,每個線程束內部在同一時間執行相同指令,對應不同數據,由統一的線程束調度器(Warp scheduler)調度。

2023-03-30 10:05:37 1370

1370 流式多處理器(Stream Multi-processor,SM)是構建整個 GPU的核心模塊(執行整個 Kernel Grid),一個流式多處理器上一般同時運行多個線程塊。每個流式多處理器可以視為

2023-04-03 14:28:09 1486

1486

流式多處理器(Stream Multi-processor,SM)是構建整個 GPU的核心模塊(執行整個 Kernel Grid),一個流式多處理器上一般同時運行多個線程塊。每個流式多處理器可以視為

2023-04-03 14:28:13 1343

1343

? ARM Cortex系列那么多處理器,該怎么區分?

2023-10-26 15:45:58 1352

1352

電子發燒友網站提供《基于VPX6—460的多處理器通信設計.pdf》資料免費下載

2023-11-08 14:37:19 0

0 電子發燒友網站提供《基于VPX6-460的多處理器通信設計.pdf》資料免費下載

2023-11-13 10:13:17 0

0

電子發燒友App

電子發燒友App

評論