EUV光刻“好日子”即將到來?

EUV光刻已引起半導體業界的特別重視,有希望在2015年或者2016年相當于在10nm制程時代導入。

EUV光刻技術相對來說還算是幸運的,由于光源功率一再推遲,影響了進程,促使英特爾、臺積電及三星紛紛解囊投資入股ASML,支持它的研發。

ASML于今年6月兼并了一家提供光源的公司Cymer,似乎已再無其他說辭,看來此次EUV光刻設備一定要成功。

解決光源功率和掩膜缺陷

EUV技術原本被寄希望于在65nm技術節點被采用,但是隨著浸液式光刻、雙重圖形等技術的不斷涌現,它嶄露頭角的日子被不斷推遲。甚至有人質疑是否真的需要EUV?時至今日,在14nm甚至10nm制程步步緊逼的時候,是不是意味著EUV的“好日子”即將到來?

目前EUV技術的現狀仍存在兩個大問題,即EUV光源功率不夠以及光刻掩膜的缺陷問題。

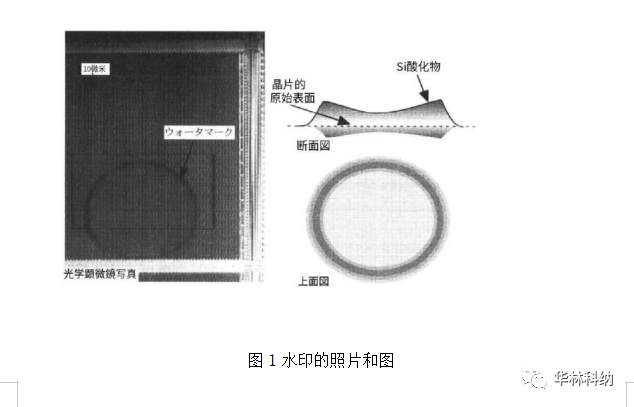

相對于目前的投影式光學系統而言,EUV掩膜板將采用反射技術,而非透射技術。要使EUV順利進入量產,無缺陷的掩膜是必不可少的,如何解決掩膜板表面多層抗反射膜的無缺陷問題成為關鍵。EUV掩膜板的制作一般是采用多層堆疊的Mo/Si薄膜,每一Mo層與Si層都必須足夠平滑,誤差容許范圍為一個原子大小。如果掩膜上存在大顆粒時,通常需要采用掩膜修正技術進行處理。另外,掩膜版還涉及儲存、運輸等難題。

最新的數據要求認為,最終EUV量產時缺陷密度的目標可放松到0.01defects/cm2即可。但如今的EUV掩膜缺陷仍高達1defect/cm2,相差兩個數量級,可見任務還非常艱巨。

EUV光刻反射式掩膜技術的難點在于掩膜白板(blank)的制備,包括缺陷數的控制以及無缺陷多層膜的制備。根據掩膜圖形成型方法的不同,其制備方法主要分為:離子束直接刻蝕法、離子注入法、Liftoff法、吸收層干刻法。吸收層干刻法不僅在工藝上切實可行,而且有利于缺陷的檢測和修補,是最為理想的掩膜制作方法。

另外,制作出無瑕疵的掩膜坯(mask blank)則是另外一個EUV光刻技術走向成熟需要解決的主要問題。有分析說,經過多年研究,業內制作光掩膜襯底的瑕疵水平已經達到每片24個瑕疵,這樣的瑕疵控制水平對于存儲器的制造來說已經可以滿足要求,但是仍無法滿足制作邏輯芯片的要求。

到2013年,6反射鏡設計的EUV光刻系統的數值孔徑NA可從現有的0.25水平增加到0.32(通過增大鏡徑等手段)。如果再進一步發展下去,通過8反射鏡設計并采用中心遮攔技術的EUV光刻系統的NA值則可達到0.7左右。

比如在掩膜板技術方面,業內領先的掩膜坯提供商Hoya公司一直都在研究超低熱脹率的掩膜坯材料,這種掩膜坯并不采用傳統的石英襯底材料制作。

另外,由于所用的照明光能量很容易被材料吸收,因此多年來人們一般認為EUV光刻適用的掩膜板很難通過加裝掩膜板的保護膜的方法來防止顆粒沾染。而目前已經有研究人員在研制硅材質的掩膜板保護膜方面取得了一些進展。對于目前條件下EUV光刻系統用的掩膜板而言,平均使用25次就會沾染上一個污染物顆粒,因此需要通過特殊的清潔處理來保證掩膜板的清潔,而這種清潔處理則不僅增加了成本,而且還會影響到掩膜板的質量。

有望在10nm制程導入

EUV光刻機制造商ASML在2013年展覽會的演講中表示,其第二代NXE 3300B的EUV光刻機已經出貨9臺給芯片制造商。在2014年時NXE 3300B中的光源功率可以達到50W,相當于43WPH水平。而100W光源可能要到2015年或者2016年實現,相當于73WPH水平。至于何時出現250W EUV光源目前無法預測,除非100W光源開發成功,并有出彩的表現。不太相信未來光刻機能達到500W光源,雖然寫進路線圖中是容易的,但是未來能否實現是個大問題。

只要實現73WPH,即可認為EUV已達到量產水平,因為與多次曝光技術相比,其成本已然下降。在10nm節點以下,如果繼續采用DP技術,則需要4倍甚至8倍圖形成像技術。

EUV光刻已引起半導體業界的特別重視,目前在英特爾等大佬的支持下經費也能保證,所以有希望在2015年或者2016年相當于在10nm制程時導入。但是EUV光刻原理與傳統的光學光刻工藝不同,所以一旦導入,將會引起半導體制造業的“騷動”,它的磨合過程需要多久,尚不便預測。但是相信由此新一輪尺寸縮小的序幕將拉開,可能推動半導體業再次高增長。

TSV封裝帶來新游戲規則

各種TSV裝技術的成功量產商用,將會帶來一種新的游戲規則,封裝革命已是一種最好的超越對手的方式。

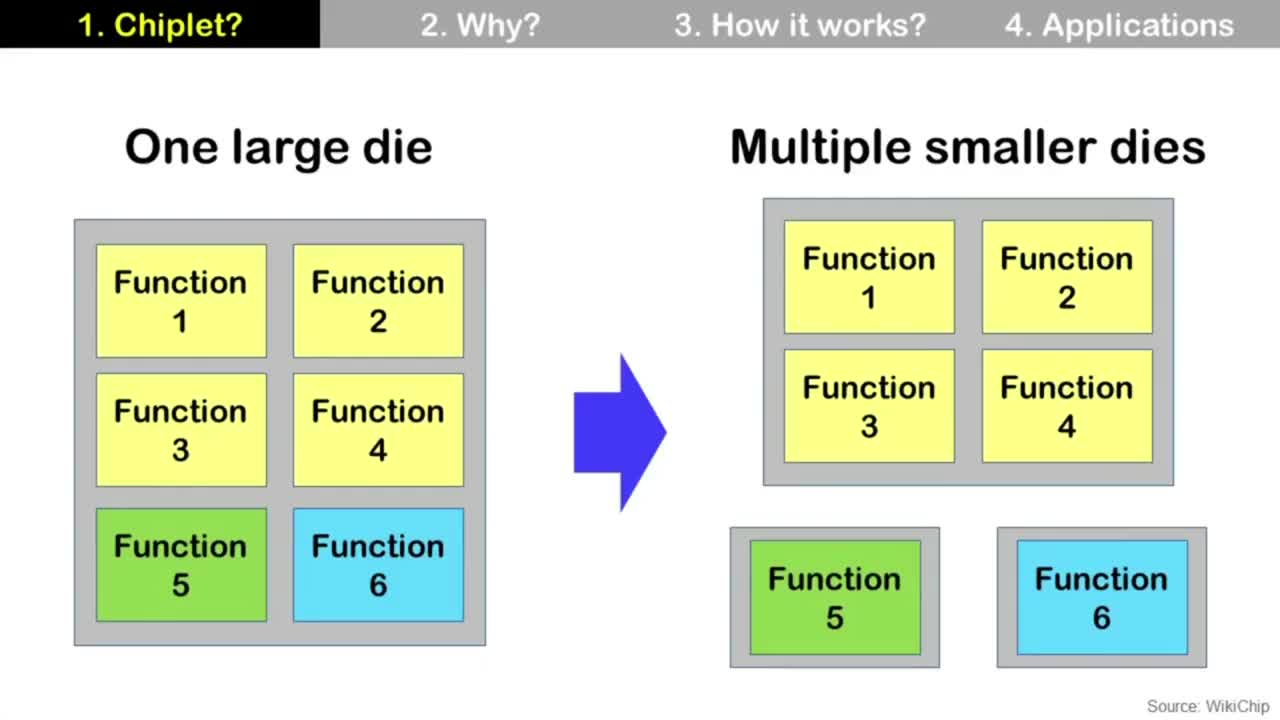

近期半導體業發展中有兩大趨勢即SoC系統級芯片及SiP系統級封裝。按邏輯思維,SoC是通過IC設計方法把多個芯片功能集成在一起,因此對于IC設計、驗證及測試等都提出了新的挑戰,所以SoC比較適用于量大面廣的芯片,否則成本降不下來。SiP是利用封裝技術,實現多個芯片而且是異質架構產品的集成,由此SiP又可延伸為采用TSV的2.5D與3D封裝技術,十分類似于多層印制板電路產品。3D封裝的原理概念早已提出,然而涉及標準、產業分工等問題,產業化過程緩慢。如今業界對于3D封裝寄予厚望,認為將掀起半導體業中超越摩爾定律的又一次革命。

封裝技術掀起革命

所謂2.5D是將多顆主動IC并排放到被動的硅中介層上,因為硅中介層是被動硅片,中間沒有晶體管,不存在TSV應力以及散熱問題。通過多片FPGA的集成,容量可以做到很大,避開了新工藝大容量芯片的良率爬坡期,并因解決了多片FPGA的I/O互連問題而大幅降低了功耗。

3D是指把多層芯片采用微凸塊及硅通孔技術(TSV)堆疊在一起。微凸塊是一種新興技術,面臨非常多的挑戰。一是兩個硅片之間會有應力,舉例來說兩個芯片本身的膨脹系數有可能不一樣,中間連接的微凸塊受到的壓力就很大,一個膨脹快,一個膨脹慢,會產生很大的應力。二是在硅通孔時也會有應力存在,會影響周圍晶體管的性能。三是熱管理的挑戰,如果兩個都是主動IC,散熱就成為很大的問題。所以行業需要解決上述三個重要挑戰,才能實現真正的3D封裝。

一般在晶圓制造CMOS結構或者FEOL步驟之前完成硅通孔,通常稱作Via first。因為TSV的制作在fab的前道工藝即金屬互聯層之前進行,此種方式在微處理器領域研究較多,可作為SoC的替代方案。

而將TSV放在封裝階段,通常稱之為Via last。這種方式的優勢是可以不改變現在的IC制造流程和設計。采用Via last技術即在芯片的周邊進行通孔,然后進行芯片或者晶圓的多層堆疊。此種方式目前在存儲器封裝中盛行。

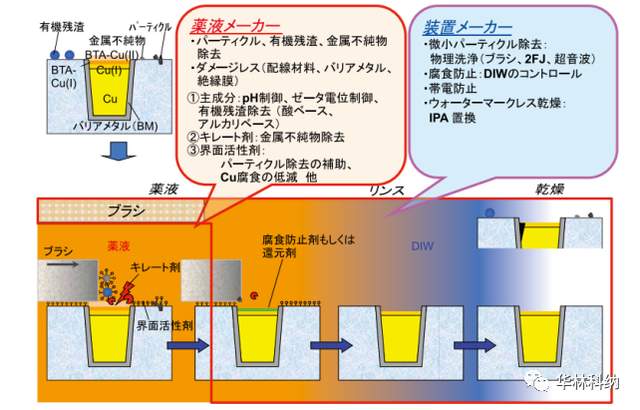

TSV通孔工藝需要幾何尺寸的測量,以及對于刻蝕間距和工藝可能帶來的各種缺陷檢測。通常TSV的孔徑在1~50微米,深度在10~150微米,縱寬比在3~5甚至更高。每個芯片上通孔大約在幾百乃至上千個。

目前能實現3D封裝的只是存儲器芯片,如東芝于2013年2月采用19nm空氣隔離技術生產出64GB與128GB的NAND閃存,并通過減薄至30微米,將16層芯片堆疊于一體,采用引線鍵合方法,作成容量達1024GB的薄型封裝。

三星也于2013年8月宣布開始量產128GB NAND 3D閃存。而意法半導體的MEMS也實現了3D封裝,因為它面臨的發熱等問題小一些。

面臨三大難題

如果我們無法解決價格問題,那么TSV的發展道路將更加漫長。目前TSV在價格與成本之間仍然存在極大的挑戰,加上新技術的不確定性所隱含的風險,以及實際的量產需求,形成了TSV技術所面臨的三大難題。

部分業界人士認為,到2014年,智能手機用的移動應用處理器可能會采用TSV技術,成為率先應用TSV量產的產品。日本JEDEC正在擬訂一個支持TSV的Wide I/O存儲器界面的方案,其目標是成為下一代采用層疊封裝(PoP)的低功耗DDR3連接的繼任技術。

市場調研機構Yole Developpement稍早前發布了一份針對3D IC與硅通孔(TSV)的調查報告指出,2011年所有使用TSV封裝的3D IC或3D-WLCSP平臺(包括CMOS影像感測器、環境光感測器、功率放大器、射頻和慣性MEMS元件)等產品產值約為27億美元,而到了2017年,產值可望增長到400億美元,占總半導體市場的9%。

因此,從目前掌握的情況看,要實現異質架構的、不同IC之間的真正3D封裝,至少還需要3~4年的時間。無論是2.5D還是3D,各種TSV封裝技術的成功量產商用,將會帶來一種新的游戲規則。在摩爾定律越來越難走、新的半導體工藝邁向1xnm越來越昂貴的今天,封裝革命已是一種最好的超越對手的方式。

450mm硅片、EUV光刻及TSV 2.5D與3D封裝三大關鍵技術本來互不相干,但是相互之間會有此消彼長的效果。目前究竟那項技術走在先,尚難說清。因為半導體業是一項規模產業,僅小批量生產也不行,價值要體現在銷售額中。

近時期半導體業的增長已趨緩,可能與尺寸縮小面臨極限等因素有關。相信當三大技術獲得突破之際,將推動產業進入又一輪的高增長。然而這三項技術由于難度都特別大,發展都不會一帆風順,而在此過程中半導體產業將面臨產業結構與發展模式等新一輪的重組與變革。

電子發燒友App

電子發燒友App

評論