現在,芯片制造商在14/16nmFinfet制程的競爭進入了白熱化階段,而下一階段的10nm和7nm的角逐也進入了預熱階段。與此同時,業界也正在推動工藝制程走向5nm。

TSMC表示,他們希望在2020年推出其5nm的工藝,而三星、格羅方德和英特爾也都在這個節點上投入了大量的金錢進行研發。

但我們可以明確知道的是,在5nm的時候,芯片制造商會面臨很多未知的挑戰。最基本的一點,我們連5nm真正到來時間和具體規格都沒能確定。更不用說可能面對的技術和經濟方面的挑戰。退一萬步,就算5nm真的確定下來,按照目前的演進,最終也就是只有幾家公司能夠承擔起5nm制程的高昂費用。

“我目前的想法是5nm是會實現,但是直到2020年前,我們都不會看到大批量的投產”,Gartner的分析師Bob Johnson表示。如果你問我真正的量產時間,我覺得這個時間會是2021或者20222年,Bob補充說。

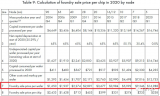

根據Bob的觀點,設計一個可用的5nm SoC的成本會達到5億美元,對比于7nm SoC的2.71億美元,成本基本翻了一番。

和28nm 的平面型器件相比,更是天價,前者的價格是后者的9倍。

對于那些想把制程推進到5nm的企業來說,他們只有兩個選擇,一個是FinFet,另一個是橫向的gate-all-around FET。

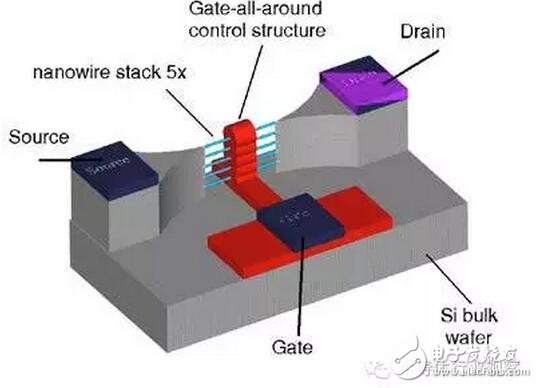

Gate-all-around (GAA),有時候被稱作橫向納米線場效應管。這是一個周邊環繞著gate的FinFet。

實際上,業界也圍繞GAA上做了很多功夫。

按照Intel架構和集成方面的資深Fellow Mark Bohr的觀點,GAA晶體管能夠提供比FinFet更好的靜電特性,這個可滿足某些柵極寬度的需求。

但業界關于GAA的討論還沒有定性,因為還有些廠商考慮在5nm的時候使用FinFET。

除了架構之外,5nm還要面臨的一個挑戰就是市場的容量問題。5nm的投資回報比也是業界顧慮的一個因素。Bobr方面認為, 5nm的世代是會出現,且會覆蓋很多類型的產品。

就目前情況看來,盡管Fab廠面臨的挑戰比較多,但GAA引起的爭議還是比較大的。因為它會給patterns, gates, 納米線和內部連接帶來極大的挑戰。除此之外,制程控制對晶圓廠來說也是一個噩夢。當然,如何平衡GAA Fet的成本也是很關鍵的。

為了幫助業界了解更多關于GAA Fet的細節,我們特意帶大家去了解一下這個基本的制程流程和這個技術將會面臨的挑戰。另外,我們還會帶大家去關注以下未來的設備,例如omplementaryFETs和垂直納米線。

Gate-all-around是什么?

現在的業界在FinFet上的競爭已經進入了白熱化階段,但是他們當中沒有一個能夠取得領先位置。

例如在邏輯器件里面,其甜蜜節點依然是40nm和28nm這兩個平面節點。

很多晶圓廠最近在28nm的營收表現甚至出現了很大幅度的攀升,尤其是在通信那塊。UMC的CEO顏博文表示。在UMC最近的一個電話會議里面,他提到UMC的28nm產線的使用率在2016年第三季度上升到90%,較前一季度的70%有了很大的提升,他補充說。

高端市場持續升溫。

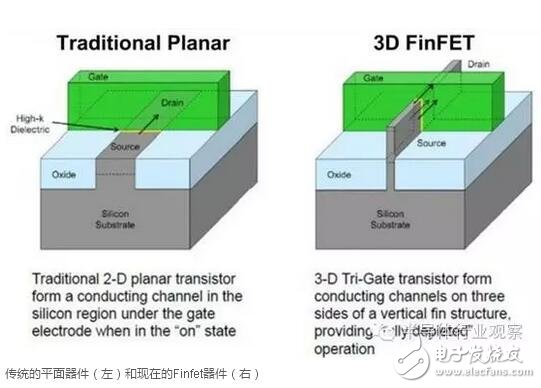

制程從22nm到16nm/14nm演變的過程中,芯片制造商的晶體管從平面型進化到FinFet,其中最大的一個原因就是FinFet可以解決平面型設備的短溝道問題。在FinFet的時候,通過在Fin的三面環繞gate,可以達到很好的控制電流的效果。最后,FinFET終于走進了主流。

三星的晶圓市場高級經理Kelvin Low表示,在7nm前,我們已經看到了挑戰。我們傾向于在縮小CPP的時候提高Vcc(工作電壓),但我們認為我們在7nm的CPP尺寸面臨了很大的挑戰。因此我們認為這需要不一樣的設備結構和不同的技術去滿足這種需求。

此外,內部銅導線在現在的節點變得越來越緊湊,這就提高了芯片的RC延遲,我們希望RC延遲得到很好的蓋上,Low表示。

根據主流的觀點,他們認為FinFet是可以擴展到5nm的,雖然這需要一些新的溝道材料的支持,例如為 pMOS注入SiGe。

應用材料的策略規劃主管Mike Chudzik表示,這樣做可以不但可以讓你獲得想要的性能,還不需要縮小fin的高度。但實際上,這樣做是不允許你去縮小的柵極長度,但改善了移動性。

一旦fin的寬度到了5nm,FinFet就會失去動力。

“你可以縮小你的fin,但你會發現,你會受到量子限制,在你的fin變窄的時候,你的能帶隙會提升,然后你的閾值電壓就會發生漂移”,Chudzik說。

這就是為什么芯片制造商對GAA產生興趣,GAA比我們現在做的所有東西都要復雜,但對于FinFet來說,這是一個自然進化。Lam Research.的CTO和高級VP Dave Hemker表示。

從表面上看,GAA和柵極夾雜在源極和漏極之間的MOSFET很類似。另外,GAA 同樣包含了Finfet,但和目前fin是垂直使用的Finfet不同,GAA的Finfet是在旁邊。

GAA Fet包含了三個或者更多的納米線,形成溝道的納米線懸空且從源極跨到漏極。其尺寸是驚人的。IMEC最近介紹的一個GAA fet的納米線只有8nm直徑。

控制電流流動的HKMG架構能夠填補源極和漏極之間的差距。

于是,問題已經很清晰了,我們為什么需要GAA。

“實際上,我認為在其在靜電學上面的性能是不夠優越的”,應用材料的Chudzid表示。你對GAA抱有期望是因為其可變性以及其可變的性能。

Coventor的CTO DavidFried也認同這個觀點。

他表示,從FinFet向GAA的轉變并不會有很大的優勢,當中你只是獲得了對晶體管靜電性能控制的提升。

Fried也指出,GAA最大的提升在于縮小了柵極寬度。這樣你就可以得到一個全環繞和一點的靜電性能的控制。當然,gate的縮小是必不可少的。

由于每個技術都有優缺點,現在讓你選擇5nm的架構,相信你心里已經有了答案。

芯片制造商也面臨艱難的決定。

“未來將會有兩個、三個甚至更多的Finfet節點,未來是否替換材料也是一個問題,是否選擇水平納米線也是一個關鍵”。Lam的Hemker表示。但晶體管是不變的,但問題的關鍵是你是否能獲得你想要的尺寸而已。

當然,在5nm的時候,你還可以有其他的而選擇,例如2.5D堆棧的die,3D的設備和其他等等。

制造gate-all-around

制造GAA fet的方法有很多種,一個簡單的方法是,芯片商在pFET和 nFET架構的溝道材料商做個選擇。如在pFET 上選硅, Ge或者SiGe,在nFET上選硅、SiGe、Ge或者三五族材料。

Ge和三五族材料的遷移特性比硅高,但這些特殊材料面臨缺陷和可靠性的問題。因此一個簡單的做法是使用Si或者SiGe。硅鍺對比于鍺和三五族半導體,其優勢是很明顯的。IMEC的邏輯設備和集成主管Dan Mocuta表示。

恰當的例子:

IMEC的GAA制程是通過在CMOS襯底上部形成一個超結晶格子結構,IMEC的超結晶格子結構是一個方形的架構,其包含了一個交互堆棧的Si和SiGe層。理想情況下,一個堆棧會包含三層的SiGe和三層的硅。

制造一個FinFET

一旦超晶格堆棧開發完成,FinFet就已經形成了。

在GAA里,Fin是在側邊的。當然,制程步驟和傳統的FinFet是一樣的。從一個離子注入機使用傳統的摻雜技術,就會在超晶格方形堆棧的頂部形成了源極和漏極。源極會在堆棧的一端形成,漏極則會在另一端完成。

在這個步驟之后,頂部的超晶結構則會以字母H的形式pattern。在經過了幾道光刻和刻蝕之后,這個結構就會和字母H很像,而這個H形狀的圖案是平躺的。

類似H圖案的兩個高層結構物分居兩端,分別充當源極和漏極,中段就是fin的一部分。

在這過程中也會面臨一些挑戰。例如在pattern的時候,現在有兩個光刻的選擇,EUV光刻和193nm 沉浸式光刻。EUV和沉浸式光刻在5nm的時候都需要多多層的pattern。

盡管業界希望在7nm和5nm的時候使用EUV,減少pattern的步驟,但是在5nm的時候,芯片制造商是可以選用這兩種方案的。

“沒有EUV,Mask會爆增,但有了EUV,Mask就可以減少了,從而降低成本”,三星的Low表示。

但目前看來,EUV還是沒有量產,因為它在光源、光刻膠和Mask方面都面臨挑戰。

現在,ASML最新版本的EUV光刻機NXE:3350B已經出貨了,這個13.5nm波長工具有一個0.33的數值孔徑和16nm間距的分辨率。

ASML同樣也將其光刻機的功率從80瓦特提升到125瓦。這就會將晶圓的產量從55、65片每小時提升到85片每小時。除此之外,ASML的新一代產品NEX:3400B也準備好了,這個針對5nm的產品擁有13nm的分辨率。

ASML打算在今年或者明年推出一款兩百瓦甚至更高瓦數的設備。但是芯片制造商則希望和以前一樣,能夠拿到250瓦的設備,這樣就可以將其產能提高到最大。那就是125片每小時。

“為了讓EUV滿足我們的需求,我們還有很多的工作要做”,GlobalFoundries的技術研究高級主管和高級fellow表示。

芯片制造商同樣希望EUV抗蝕劑能讓其pattern的間距在30nm以下。

“如果抗蝕劑的靈敏度每平方厘米有20焦耳的話,那么這個花費就和沉浸式的三倍pattern差不多”,Levinson表示。

“基于目前的數據,20焦耳是可以達到的,在7nm的時候,30焦耳也是沒問題的。這并沒有給我們帶來類似于沉浸式三倍pattern的花費。但使用EUV還是有其他優勢的,在7nm的時候選擇EUV是非常正確的”,他補充說。

制造納米線

下一步可能就是GAA面臨的最大挑戰,那就是制造納米線。

在pattern之后,如上文所述,形似H的結構兩端分別代表源極和漏極,我們就得在中段制造納米線。

在這個步驟,IMEC和其他供應商已經開發出一個可替代的金屬柵極工藝。一開始,中間段是一個包含了交替堆棧硅和硅鍺層的超晶格結構。

使用可替代工藝,目標就是把交替層中的SiGe層移除,這樣就會只剩下硅層,且在硅層之間留下了一個空間。基本上來說,每一個硅層就形成了納米線的基礎,每個納米線在SiGe的“壓迫”之下,會提升溝道的移動性。

理想情況下,一個設備會有三層獨立的納米線,每個納米線都在一個水平方向運行。同時每個納米線都是懸空且從源極穿到漏極。

基本上,這三層納米線相互之間是放置在頂部的(頂部、中部和頂部),同時納米線是有分割空間分開的,互相也不會碰到。

在柵極替換過程中,芯片制造商使用一個刻蝕工具去移除材料。但傳統的刻蝕工具在GAA上可能達不到想要的尺寸。

挑戰就是在15挨(1挨等于0.1nm)甚至更小的間隙里移除硅鍺,且在移除硅鍺的過程中,不能干擾到設備的其他部分。

在這個過程中,芯片制造商可能需要用到下一代的刻蝕技術atomic layeretch(ALE),這個可以在原子尺度上有選擇且精確地移除目標材料。理論上,ALE可以移除硅層之間的硅鍺,而不會破壞剩下的部分。

“這個方法是可以有選擇性的去除硅鍺,這樣你就能生成納米線”,應用材料的全球產品經理Matt Cogorno表示。

然而,我們還需要面臨其他挑戰。

在納米線下面,會有一個寄生溝道,你需要找個方法去阻隔寄生溝道的泄露,IMEC的做法是一個叫做地平面摻雜的方式,我們會在沉積超晶格結構之前摻雜這個區域,這樣的話就會阻止泄露且提升亞閾值斜率,IMEC的Mocuta表示。

柵極和內部連接

現在,設備需要一個柵極,使用atomic layerdeposition (ALD),,HKMG材料被放置在源極和漏極的狹小間隙之間。這樣的話,柵極就會被每個納米線包圍。

在這里會面臨很多放置的挑戰,Coventor的Fried表示。

在一個Finfet,你看柵極的溝槽,你可以看到fin,因此你可以把材料放置在任何地方,你只需對fin的側墻有點擔心,但你可以看到你放置的任何地方。

但在GAA,這是一個完全不同的故事。

現在你看向那個溝槽,你只看到那些線,我需要把材料放置在指定的位置,同時我還需要一個高質量的保護涂層,Fried表示。

其他人也認同這個觀點。

ASMI的全球產品市場主管MohithVerghese說,無論你是在線周圍涂層,還是線的下面涂層,你并沒有任何對準線,你只有祈求化學工作能夠完美。

要解決方案?

我們會看到熱ALD的再次出現,這完全依賴于化學,Verghese表示。熱ALD包括了一個帶有兩個反應物的二進制進程,A和B。A反應物被注入ALD里面,晶圓被加工然后化學物被清洗,然后化學物B經歷同樣的操作。

最后,在5nm的時候,內部連接會成為最大的挑戰。

為了解決RC延遲的問題,芯片制造商需要新的突破。這是一個很大的問題,Lam的Hemker說。你需要從各個方面解決這個問題,這是一個有關材料、設備、集成方案和設備布局多方面綜合的解決方案。

接下來呢?

雖然不確定是否會實現,但是芯片制造商在研發過程中會關注3nm和其他更先進的制程。

在3nm的時候,產業或許會探索水平GAA fet和垂直納米線FET。

“我們現在正在和某些大學就垂直納米線的相關研究進行合作,如果能夠成功,這回事一個很大的進步。現在你從密度上解耦晶體管的性能,你需要將其尺寸變得越來越小,這樣每更新一代進程,泄露就會增加。泄露的多少取決于先的長度。同時其堆積密度就是其直徑。現在則更加獨立了,你仍然需要去蝕刻這些東西并制造,與此同時,你還有很多的工作要做”。Hemker說。

除此之外,complementaryFET同樣吸引了業界的關注。

這個設備有點像水平的GAA。每個納米線就是nFET,然后下一個就是Pfet。等等注入類似。

“你在三維孤立這些設備并對戰起來,這可能是一個思考模式的轉移,這是電路密度的一個徹底轉移。這就真的是一個大挑戰了”。Fried表示。

電子發燒友App

電子發燒友App

評論