基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求奇數倍分頻(如3、5等)、小數倍(如2.5、3.5等)分頻、占空比50%的應用場合卻往往不能滿足要求。硬件工程師希望有一種靈活的設計方法,根據需要,在實驗室就能設計分頻器并馬上投入使用,更改頻率時無需改動原器件或電路板,只需重新編程,在數分鐘內即可完成。為此本文基于 CPLD/FPGA用原理圖和VHDL語言混合設計實現了一多功能通用分頻器。

分頻原理

偶數倍(2N)分頻

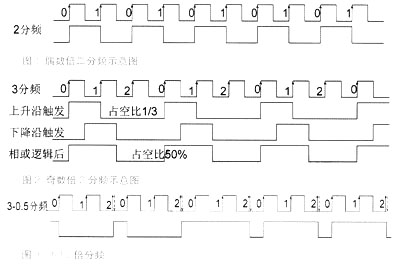

使用一模N計數器模塊即可實現,即每當模N計數器上升沿從0開始計數至N時,輸出時鐘進行翻轉,同時給計數器一復位信號使之從0開始重新計數,以此循環即可。偶數倍分頻原理示意圖見圖1。

奇數倍(2N+1)分頻

(1)占空比為X/(2N+1)或(2N+1-X)/(2N+1)分頻,用模(2N+1)計數器模塊可以實現。取0至2N之間一數值X(0< X<2N),當計數器時鐘上升沿從0開始計數到X值時輸出時鐘翻轉一次,在計數器繼續計數達到2N+1時,輸出時鐘再次翻轉并對計數器置一復位信號,使之從0開始重新計數,即可實現。

(2)占空比為50%的分頻,設計思想如下:基于(1)中占空比為非50%的輸出時鐘在輸入時鐘的上升沿觸發翻轉;若在同一個輸入時鐘周期內,此計數器的兩次輸出時鐘翻轉分別在與(1)中對應的下降沿觸發翻轉,輸出的時鐘與(1)中輸出的時鐘進行邏輯或,即可得到占空比為50%的奇數倍分頻時鐘。當然其輸出端再與偶數倍分頻器串接則可以實現偶數倍分頻。奇數倍分頻原理示意圖見圖2。

N-0.5倍分頻

采用模N計數器可以實現。具體如下:計數器從0開始上升沿計數,計數達到N-1上升沿時,輸出時鐘需翻轉,由于分頻值為N-0.5,所以在時鐘翻轉后經歷 0.5個周期時,計數器輸出時鐘必須進行再次翻轉,即當CLK為下降沿時計數器的輸入端應為上升沿脈沖,使計數器計數達到N而復位為0重新開始計數同時輸出時鐘翻轉。這個過程所要做的就是對CLK進行適當的變換,使之送給計數器的觸發時鐘每經歷N-0.5個周期就翻轉一次。N-0.5倍:取N=3,分頻原理示意圖見圖3。

對于任意的N+A/B倍分頻(N、A、B∈Z,A≦B)

分別設計一個分頻值為N和分頻值N+1的整數分頻器,采用脈沖計數來控制單位時間內兩個分頻器出現的次數,從而獲得所需要的小數分頻值。可以采取如下方法來計算個子出現的頻率:

設N出現的頻率為a,則N×a+(N+1)×(B-a)=N×B+A 求解a=B-A; 所以N+1出現的頻率為A.例如實現7+2/5分頻,取a為3,即7×3+8×2就可以實現。但是由于這種小數分頻輸出的時鐘脈沖抖動很大,現實中很少使用,本次設計未予以設計。

采用VHDL語言可以實現計數器的下降沿觸發翻轉,并且CPLD/FPGA具有可并行執行的特性,可以保證兩種不同的觸發翻轉以及分頻時鐘輸出保持同步,所以上述分頻方法可以基于CPLD/FPGA予以實現。

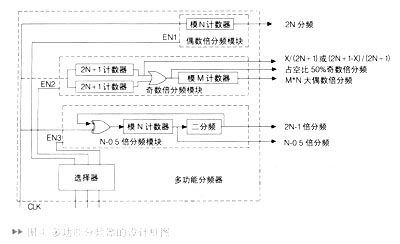

綜合上述分析,實現多功能分頻器功能的設計框圖如圖4所示。

多功能分頻器的設計與實現

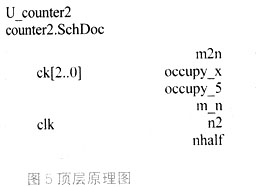

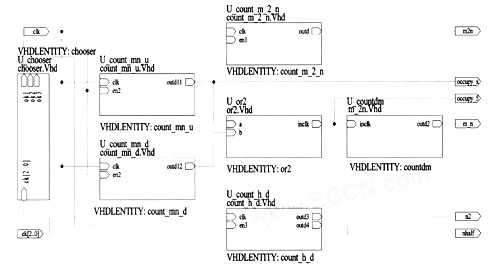

本設計使用第三方EDA開發工具Protel DXP。該開發工具支持層次原理圖及VHDL語言混合設計并能進行編譯、時序和功能仿真,支持Xilinx、Altera、Lattice等公司的系列 CPLD/FPGA器件,并且具有設計直觀、層次性好等優點。在設計中采用兩級原理圖和底層VHDL語言三級結構來實現,使整個的設計以功能模塊化,便于程序修改、功能升級和分頻系數的設定。對于分頻值的設定采取了軟件設定的方法,即只需在VHDL語言程序中按照自己的需求對相應的參數作修改、設定,而且設定值的取值靈活。頂層原理圖、次級原理圖分別如圖5、6。

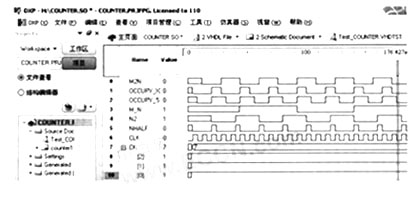

本次設計CK延時3ns后設值為111,即功能模塊全部選中工作;偶數倍分頻模塊中模N計數器N設置為2,實現四分頻;奇數倍分頻模塊中模2N+1計數器 N設置為1實現三分頻,占空比X設置為1即分頻系數為1/3,模M計數器M值設置為2實現2M*(2N+1)=12分頻;N-0.5倍分頻模塊中N設置為 3,實現2.5分頻。從方針波形中可以看出,實現了通用多功能分頻器。若要得到其他值,只需修改相應功能模塊的VHDL語言中的相關的參數,再進行編譯、綜合適配、下載即可。

器件適配及仿真波形

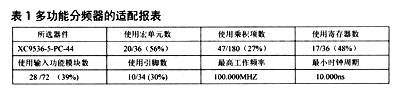

本設計采用Xilinx XC9536-5-PC44 CPLD器件實現,經綜合適配后其報表如表1。

仿真波形如圖7。

結束語

本文介紹了基于CPLD/FPGA的多功能分頻器的設計方法,給出了原理圖并用VHDL語言予以實現。結合ISP技術,基于CPLD/FPGA的分頻器可以變得像軟件那樣靈活且易于修改、升級,能夠在同一個器件內實現多種分頻功能,使之成為一種多功能硬件。在產品設計、制造過程中、甚至在交付用戶使用之后,仍可根據要求對器件進行邏輯重構和功能修改。在數字系統設計中,為用戶提供了一種低成本的解決方案,減少了工作量和成本。

相關閱讀:

- [電子動態] Altera和Apical交付WDR FPGA監控應用解決方 2010-03-25

- [電子動態] FPGA實現與40G QSFP光學模塊的互操作性 2010-04-02

- [電源技術] 基于CPLD的脈沖密度功率調節高頻逆變電源 2009-11-18

- [電源技術] 采用CPLD的光伏逆變器鎖相及保護電路設計 2010-03-03

- [無線通信] 雷達視頻積累算法在FPGA上的實現 2009-11-09

(責任編輯:發燒友)

發表評論:

最新評論

已有0條評論,共317人參與,點擊查看相關下載

- fpga入門教程下載pdf8776

- FPGA-SOPC入門中文教程V2.037305

- Altera FPGA/CPLD設計(高級篇)4848

- Altera FPGA/CPLD設計 (基礎篇)4463

- 可編程邏輯陳列fpga和cpld3362

電子技術文章排行

本類排行

總排行

- 三相異步電機的交流變頻調速實驗系統916

- 安全繼電器及安全PLC在制造行業的應878

- FPGA芯片選擇策略和原則734

- VHDL和Verilog HDL語言對比546

- 編程器分類及功能詳解415

- 基于FPGA和DDS的信號源設計406

- 奧地利微電子新款高集成度電源管理IC406

- PLC在恒壓供水系統中的應用設計368

- 水泵機組全自動變頻調壓PLC控制系統353

- FPGA基礎知識簡介339