�ڵͳɱ�FPGA�Ќ��F�ӑB��λ�{��

��FPGA�У��ӑB��λ�{��(DPA)��Ҫ�nj��FLVDS�ӿڽ��Օr���r犺͔���ͨ������λ�a�������_�����_���յ�Ŀ�ġ�ALTERA�ĸ߶�FPGA����STRATIX(r) ϵ�����Ԏ���DPA�·�����Ͷ˵�FPGA����CYCLONE(r)ϵ�����Ǜ]�еġ�������Ҫ�U������ڵͶ�FPGA�Ќ��F�@��DPA�Ĺ��ܡ�

���F�ܘ�

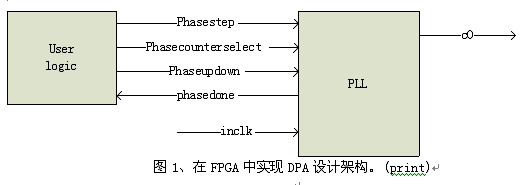

��LVDSݔ����Օr���r犺͔�������λ�����Dz��_���ģ�����҂���Ҫ���r犵���λ�����{����ʹ�Õr��ܷ����IJɼ���ݔ�딵���������ĺ��ľ������i��hPLL����λ�{�����ܣ��a�����ɂ��r犵IJ�ͬ��λ������Щ��λ�ܜʴ_�IJɼ���ݔ�딵����Ȼ��ȡ�������g��һ���r���λ���������������r�IJɘӕr犡�����ͨ�^PLL�a��0��45��90��135��������315��8�����Ƶĕr犣����0��45��90�����Ƶĕr������_�ɘӵ�ݔ�룬��ô����xȡ���g��λ����45�ȵĕr�����ɘӕr犡��@�ӽӿ��Ͼ������ĕr��ԣ�����Ķ����C�·�Ŀɿ��ԡ��D1���@���OӋ�Ļ����Y����ͨ�^PLL�{����λ�Ľӿڣ��a���˕r犵IJ�ͬ��λ���ɼ�����������x��һ������m����λ��

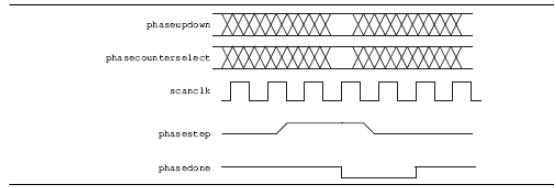

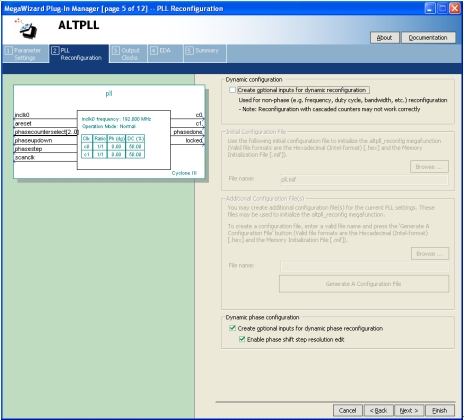

CYCLONEϵ�е�PLL����λ�{���ӿڕr����D2��ʾ�����Ñ�߉����phasestep, phasecounterselect�cphaseupdown��̖�r��PLL��ݔ���r�C0��׃һ����λ����QII����PLL�r���Ñ�����x��create optional inputs for dynamic phase reconfigure����tȱʡ�Dz������@Щ���_�ģ���D3��ʾ����������output clock tab�Ќ���phase shift step resolution��ֵ���@�Ӳ��ܴ_��ÿ����λ�{���IJ��L��

������

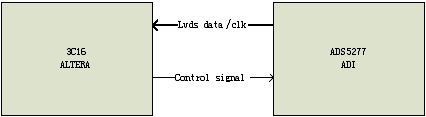

�����еą����OӋ����CYCLONE3�������cADI��˾��ADS5277�ӿڣ��ѽ���Ӳ���Ϝyԇ�^���C������Ч�ġ�ADS5277��һ��8ͨ������ADCоƬ����Ҫ���ڳ��O���Լ��yԇ�O���С��D4��ԓ�����OӋ�·��D��

ADS5277�͵�FPGA����һ��192MHz�ĕr犣�8·LVDS������������384Mbps����늏�λ��ADS5277�l�͵Ĕ����ǡ�0101010101��������FPGA����DPA�·���ʴ_�_���r���λ����ͨ�^������̖��ʹ��ADS5277�l�͡�000000111111�������@�ӵ�PATTERN��FPGA���Դ_���ֵ�߅�磬�@һ���ɹ��Ժ�FPGA�Ϳ���ͨ�^������̖ADS5277�l�����������r�Ĕ�������齛�^�˕r���λ�{���@һ�^�̣��Ժ�Ĕ����ɘ��Ƿdz������ģ������ܵ��ض�늉�׃������Ӱ푡�

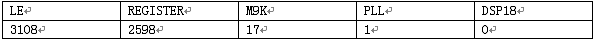

��Ȼ�@���OӋ���Ժ�����LVDS�l��оƬ�ӿڣ�����ֻ����ADS5277���������ԑ�����ALTERA�߶�FPGA�У�����STRATIX4�Ď���DPA�����·�Ĺ��_ֻ�ֲ�������BANK�����õ��@���OӋ��Ԓ������BANK��IOҲ��ʹ�á�DPA�OӋ�����ĵ�߉�YԴ�Ƿdz�С�ģ��x��������3C16F256C8, ���1��ʾ��

�D1����FPGA�Ќ��FDPA�OӋ�ܘ���

�D2��PLL����λ�{���ӿڕr��

�D3��

�D4�������OӋ�·��D��

��1���YԴ����

�ֱ�

�̺���

Altera��˾