可控硅培訓資料(下)-圖解篇

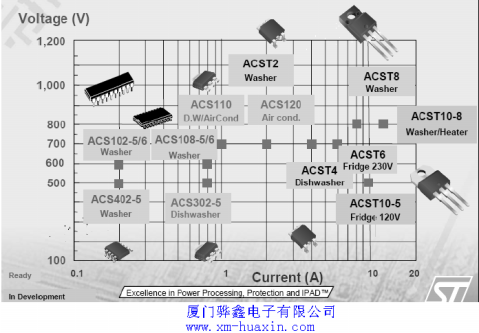

ACS/ACST Triac即是Crowbar Triac方案的一種:

它可提升可控硅的EMC能力,使得產品輕而易舉的通過歐盟的各種EMC測試,它的耐壓將超過2KV或更高.(具體測試

條件可參考產品DATASHEET)下面以ACS108-5為例說明:當它帶一150Ω(相當于40W冷光燈)時,它可通過IEC6100-4-5的浪涌測試.

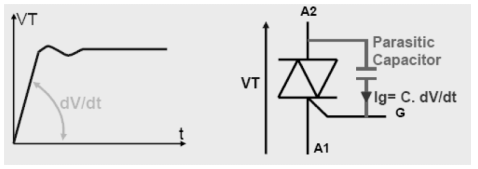

當實際提供的dV/dt 大于產品規格指定的靜態dV/dt時,可控硅將會有誤觸發而導致開通的危險.但此類誤觸發不會對可控硅本身造成損壞.

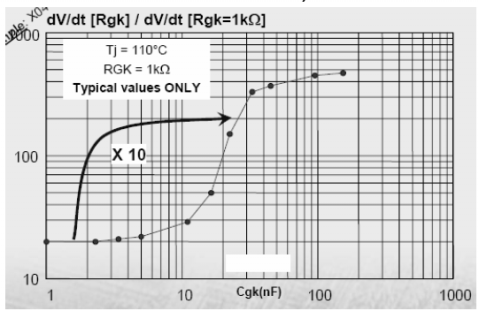

靜態dV/dt也和溫度有直接關系,下圖為一簡單示意圖:以24A;600V Triac為例:溫度越高,dV/dt 越小;

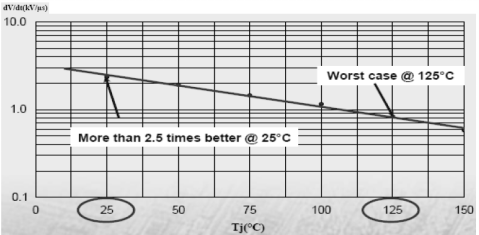

對于單向可控硅(SCR)的電子噪聲抗干擾措施: 減少Rgk,將提高dV/dt.

?

?

減少Rgk后,一部分寄生電容電流將被Rgk旁路,從而達到抗干擾目的.

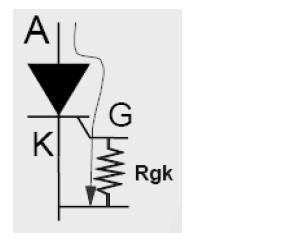

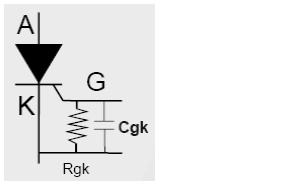

對于單向可控硅(SCR)的電子噪聲抗干擾的另一措施:減少Rgk和增加一電容Cgk,將提高dV/dt.(此措施尤其對大于8A的SCR有效)

?

?

減少Rgk和增加Cgk后,一部分寄生電容電流將被Rgk和Cgk旁路,從而達到抗干擾目的.

?

?

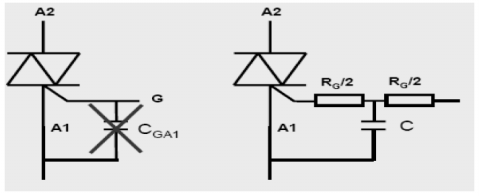

對于雙向可控硅(Triac)的電子噪聲抗干擾的措施:加一Pi型電路.

請注意:CGA1將不再允許直接加在觸發端,因為CGA1將徹底減少第二和第三象限的di/dt能力.(工藝結構的原因)

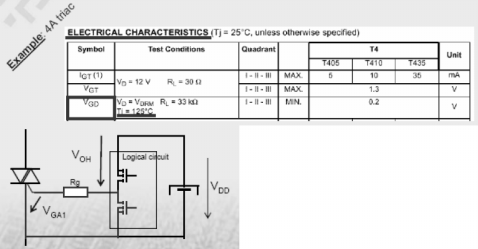

對于雙向可控硅(Triac)的電子噪聲抗干擾的另一措施: 設計好VGD參數電路.

設計門極驅動電壓時,要有足夠高的VGA1電壓(大于VGD),檢查(VDD-VOHMAX.)

?

?

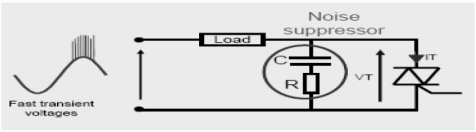

RC噪聲抗干擾參數的設計:

為了改善可控硅在瞬態時的抗干擾能力,它將可能使用一RC電路作為噪聲抑制器.通常來講,C將選擇約1nF左右,R將選擇47~75Ω;(C和R不可選的太大) 而且,為了準確設定RC值,我們最好做一個BURST測試(IEC6100-4-4)

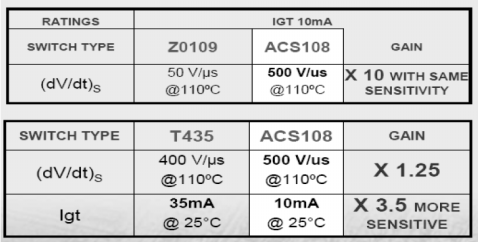

ACS/ACST Triac同普通可控硅的抗干擾能力比較:

改善抗干擾性,而且降低IGT到適中值但不會太小.

?

?

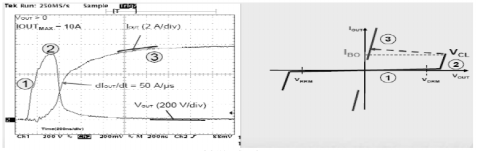

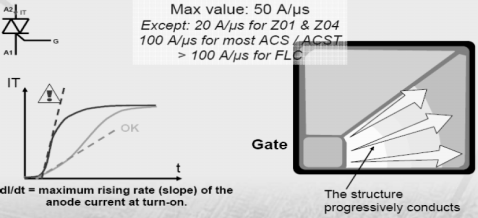

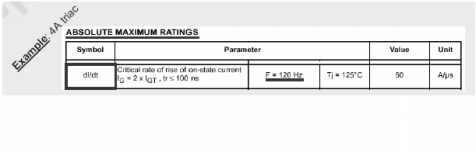

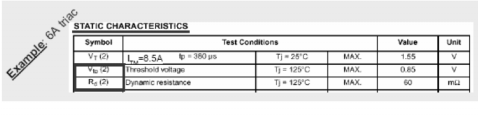

可控硅開啟時的參數:di/dt

請注意檢查在可控硅開啟時,di/dt值不能超過DATASHEET上指定時,否則可控硅將被損壞.

?

?

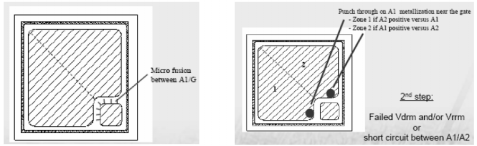

可控硅在使用過高的di/dt后的損壞現象:

????????第一步:IGT超過規格????????????????????????????? 第二步:VDRM 和/或VRRM失效,或者第一陽極和第二陽極直接短路.

用測量的波形舉例說明di/dt

?

?

單向可控硅的硅狀結構極其等效電路

??????????? ?內部結構:?????????????????????????????????????????????????????????????????? ???? 等效電路:

符號:

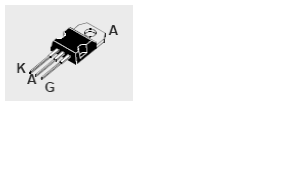

PIN腳指定順序:KAG

注意:單向可控硅總是正極電流驅動

雙向可控硅的硅狀結構

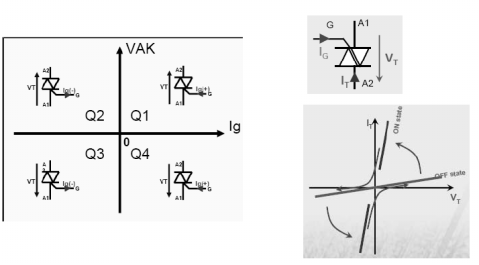

請注意:對于雙向可控硅,它既可正向電流驅動,亦可反向電流驅動,取決于具體的可控硅型號(參考DATAHSEET)

?

?

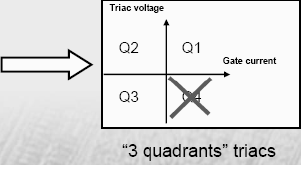

雙向可控硅觸發象限:Q1/Q2/Q3/Q4

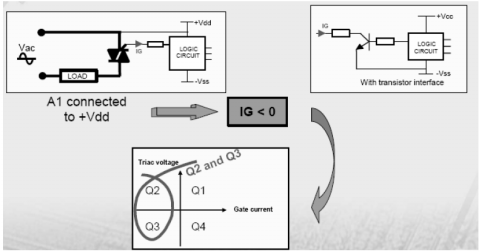

雙向可控硅Q1/Q4驅動的應用:第一陽極(A1)和VSS相連,通常我們不推薦Q4驅動,因為它相比于其它象限di/dt能力稍小些以及要求較高的IGT.

雙向可控硅Q2/Q3驅動的應用:第一陽極和VDD相連.

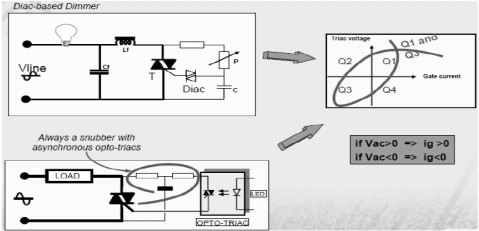

雙向可控硅Q1/Q3驅動的應用:

需在門極加一DIAC,或加帶PI型網絡的隔離光藕.

?

?

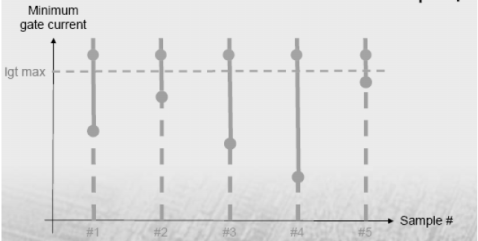

驅動電流參數:IGT? 最小且必要的可控硅門極驅動電流在DATASHEET中,由于參數的離散性,所以一般最大值將被寫入規格書中.

驅動電壓參數:VGT?? 由于最大IGT流過時所產生的門極電壓.

?

?

對于驅動電流參數的選擇:

由于溫度對它影響較大,所以我們選擇時要滿足以下等式: IGT(-10℃)=1.5×IGT(25℃)

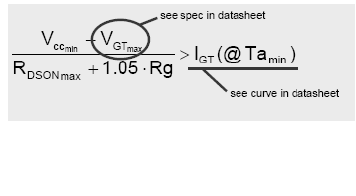

對于門極驅動電阻參數的選擇:

考慮到?Rgmax=1.05Rg(電阻最大:5%)

?最小溫度:取決于使用環境溫度

?最大輸出電壓:取決于邏輯電平

?最小的輸入電壓:VCC

所以我們用下式去計算Rg:

快速設計規則:Rg<2×(VCC/IGT)

?

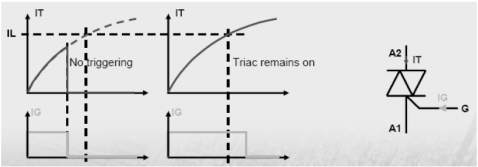

門鎖電流:IL

定義:當移開門極驅動時,陽極最小且必要保持導通的電流幅度.

?

門鎖(保持)電流IL(IH)將與結溫有關:TJ越高,IL(IH)將越小.

?

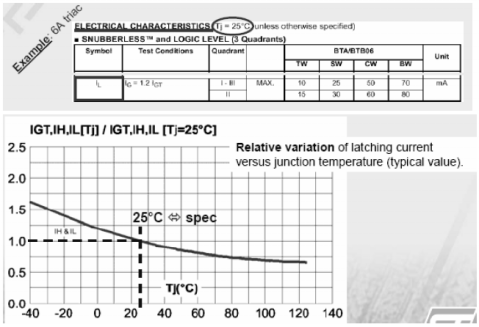

最小門極電流持續時間的設計:

i(t)=Ipeak*sin(wt)

?

?

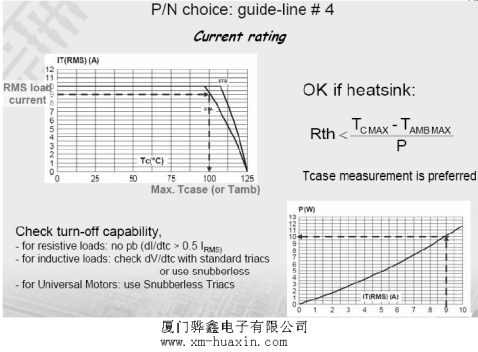

熱設計: 在做熱設計時,首先了解穩定狀態時的電流設計:

ITRMS?在給定的最大表面溫度條件下的最大的RMS電流值.(特別是取決于散熱器的尺寸)

它是一熱限制

?

?

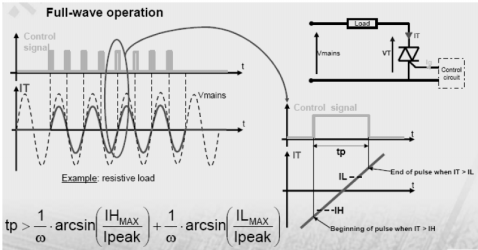

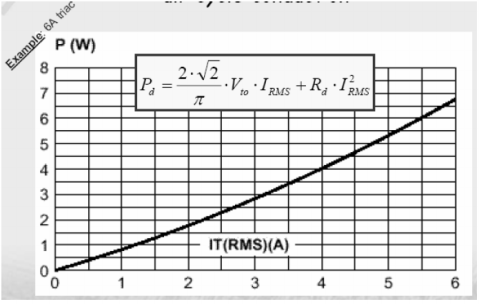

其次要知道功耗設計:

功耗計算方法:

?

?

如果是其它波形時:

?

?

也可以用DATAHSHEET中的圖表和下面等式去近似獲得功耗值:

?

?

實際應用中的TJ的設計:

算出來的TJ必須低于DATAHSHEET上規定的TJMAX.否則散熱器是必要的!!!

?

?

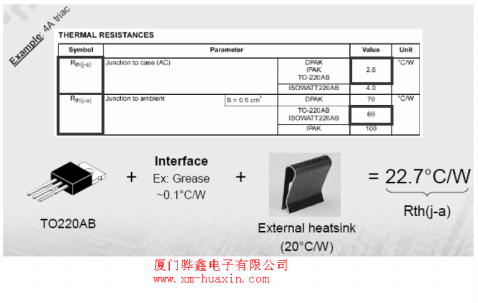

舉例說明熱設計:

?

?

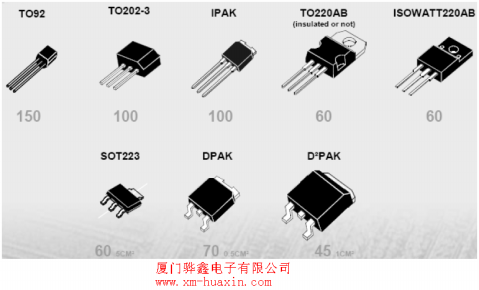

對于不同的封裝,它的結點到周圍環境之間的熱阻是不同的:

影響熱阻因素:針對功率SMD器件的銅散熱片

a)銅箔厚度

b)PCB板厚度

c)銅表面處理

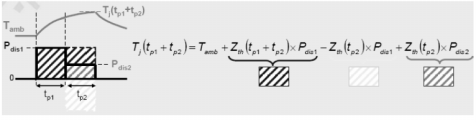

瞬態電流設計注意事項:

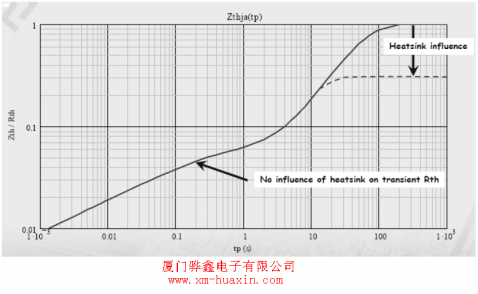

什么是Zth參數?由于消耗功率脈沖帶來的溫度升高!

?

?

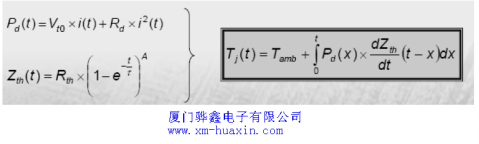

如何計算和使用Zth(t)參數?

疊加原理:

功率積分:

?

?

計算Zth(j-c)或者Zth(j-a)的模型:

在穩定狀態下的散熱器影響:

?

?

外加散熱器的使用:(Rth(j-a)或Rth(j-c)

?

?

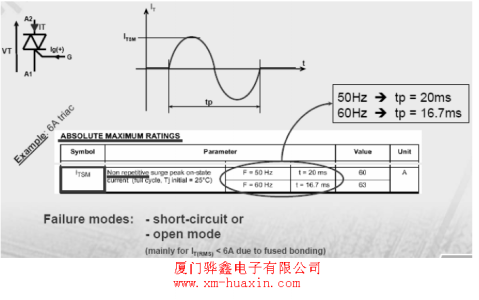

瞬態過流設計:

ITSM定義?不可重復的最大浪涌電流能力 ?

?

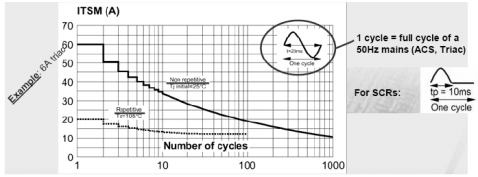

浪涌電流能力:

下圖舉例說明”浪涌峰值通態電流的次數”,它可供脈沖周期大于20MS的場合;

?

?

ITSM參數:定義?最大的浪涌電流(在16.7或明或20ms以內),超過ITSM,可控硅將會短路或開路失效;

I2t參數:定義?保護器件的熔化特性

最大不可重復電流能力的評價:

?

?

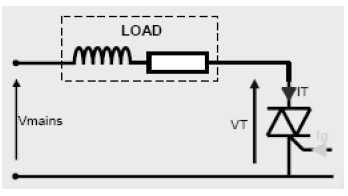

關斷過程中的參數: (di/dt)c & (dv/dt)c

在感性負載應用中,電流和電壓總是不在同一相位,在關斷時,IT=0,但VT≠0

如果設計時超過DATASHEET中的指定的(di/dt)c或者(dv/dt)c,可控硅可能將保持導通.(此時IG=0)

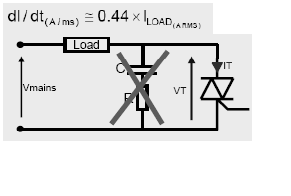

(di/dt)c將取決于負載特性:

?

?

(di/dt)c相對于(dv/dt)c:

?

?

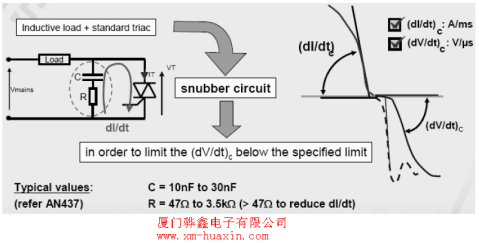

減少(dv/dt)c方法:加一RC網絡

注意:(di/dt)c值僅僅取決于負載,它意味著必須選擇好的AC Switch去維持此值!例如ACS/ACST系列

產品.

?

?

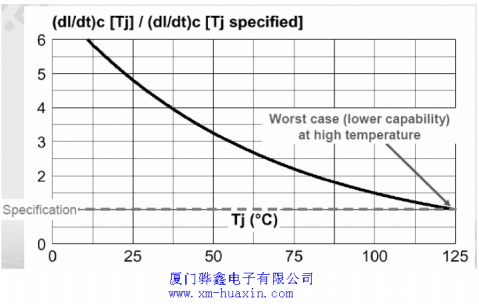

結溫對(di/dt)c的影響:TJ越大,(di/dt)越小

?

?

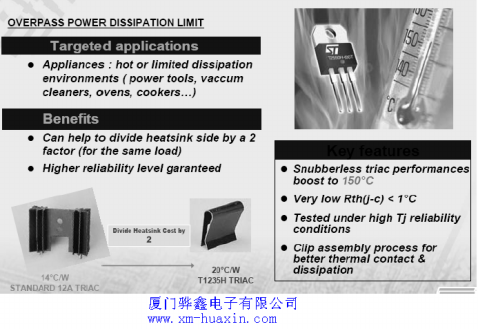

無緩沖網絡的雙向可控硅:

不存在(dv/dt)c的限制!

只要檢查關斷過程中的di/dt(可能由負載造成)

注意:無緩沖網絡的雙向可控硅僅有三象限!

?

?

舉例說明無緩沖網絡的雙向可控硅的優點

?

?

保持電流IH:當IT低于IH時,可控硅將被關斷!

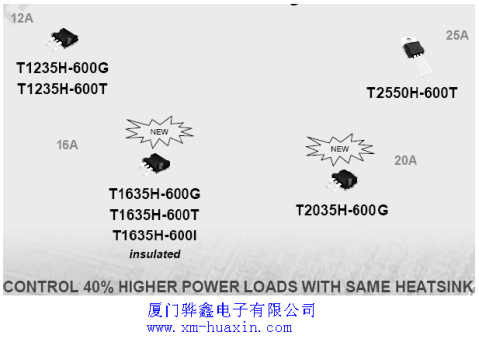

高結溫可控硅:

高結溫可控硅產品范圍:

?

?

ACS/ACST可控硅選用指南:

?

?

非常好我支持^.^

(13) 100%

不好我反對

(0) 0%

相關閱讀:

- [模擬技術] IGBT與MOS管、可控硅的區別 IGBT驅動電路設計 2023-10-18

- [LED驅動] 采用LT3799設計的三端雙向可控硅調光LED驅動器電子電路 2023-10-15

- [模擬技術] 兩顆電容解決可控硅產生的二次放電問題 2023-10-09

- [電子說] 五大電子技術知識詳解(邏輯門電路 可控硅 二三極管) 2023-09-22

- [電子說] 可控硅對觸發電路的要求 2023-09-20

- [電子說] 在RL78/G13芯片上通過可控硅實現風機調速的一種方法 2023-09-28

- [電子說] 晶閘管的特性及工作原理 2023-09-15

- [電子說] 可控硅的用途及結構 2023-09-14

( 發表人:admin )