主板MOSFET的封裝技術(shù)圖解大全

主板MOSFET的封裝技術(shù)圖解大全

?主板的供電一直是廠商和用戶關(guān)注的焦點(diǎn),視線從供電相數(shù)開始向MOSFET器件轉(zhuǎn)移。這是因?yàn)殡S著MOSFET技術(shù)的進(jìn)展,大電流、小封裝、低功耗的單芯片MOSFET以及多芯片DrMOS開始用在主板上,新的功率器件吸引了主板用戶的眼球。本文將對主板采用的MOSFET器件的封裝規(guī)格和封裝技術(shù)作簡要介紹。

??? MOSFET芯片制作完成后,需要封裝才可以使用。所謂封裝就是給MOSFET芯片加一個(gè)外殼,這個(gè)外殼具有支撐、保護(hù)、冷卻的作用,同時(shí)還為芯片提供電氣連接和隔離,以便MOSFET器件與其它元件構(gòu)成完整的電路。

??? 芯片的材料、工藝是MOSFET性能品質(zhì)的決定性因素,MOSFET廠商自然注重芯片內(nèi)核結(jié)構(gòu)、密度以及工藝的改進(jìn),以提高M(jìn)OSFET的性能。這些技術(shù)改進(jìn)將付出很高的成本。

??? 封裝技術(shù)也直接影響到芯片的性能和品質(zhì),對同樣的芯片以不同形式的封裝,也能提高芯片的性能。所以芯片的封裝技術(shù)是非常重要的。

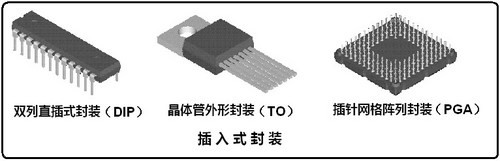

??? 以安裝在PCB的方式區(qū)分,功率MOSFET的封裝形式有插入式(Through Hole)和表面貼裝式(Surface Mount)二大類。插入式就是MOSFET的管腳穿過PCB的安裝孔焊接在PCB上。表面貼裝則是MOSFET的管腳及散熱法蘭焊接在PCB表面的焊盤上。

??? 常見的直插式封裝如雙列直插式封裝(DIP),晶體管外形封裝(TO),插針網(wǎng)格陣列封裝(PGA)等。

?

??? 典型的表面貼裝式如晶體管外形封裝(D-PAK),小外形晶體管封裝(SOT),小外形封裝(SOP),方形扁平封裝(QFP),塑封有引線芯片載體(PLCC)等等。

?

??? 電腦主機(jī)板一般不采用直插式封裝的MOSFET,本文不討論直插式封裝的MOSFET。

??? 一般來說,“芯片封裝”有2層含義,一個(gè)是封裝外形規(guī)格,一個(gè)是封裝技術(shù)。對于封裝外形規(guī)格來說,國際上有芯片封裝標(biāo)準(zhǔn),規(guī)定了統(tǒng)一的封裝形狀和尺寸。封裝技術(shù)是芯片廠商采用的封裝材料和技術(shù)工藝,各芯片廠商都有各自的技術(shù),并為自己的技術(shù)注冊商標(biāo)名稱,所以有些封裝技術(shù)的商標(biāo)名稱不同,但其技術(shù)形式基本相同。我們先從標(biāo)準(zhǔn)的封裝外形規(guī)格說起。

??? 一、標(biāo)準(zhǔn)封裝規(guī)格

??? 1、TO封裝

??? TO(Transistor Out-line)的中文意思是“晶體管外形”。這是早期的封裝規(guī)格,例如TO-92,TO-92L,TO-220,TO-252等等都是插入式封裝設(shè)計(jì)。近年來表面貼裝市場需求量增大,TO封裝也進(jìn)展到表面貼裝式封裝。

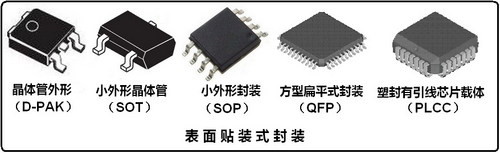

??? TO252和TO263就是表面貼裝封裝。其中TO-252又稱之為D-PAK,TO-263又稱之為D2PAK。

??? D-PAK封裝的MOSFET有3個(gè)電極,柵極(G)、漏極(D)、源極(S)。其中漏極(D)的引腳被剪斷不用,而是使用背面的散熱板作漏極(D),直接焊接在PCB上,一方面用于輸出大電流,一方面通過PCB散熱。所以PCB的D-PAK焊盤有三處,漏極(D)焊盤較大。

?

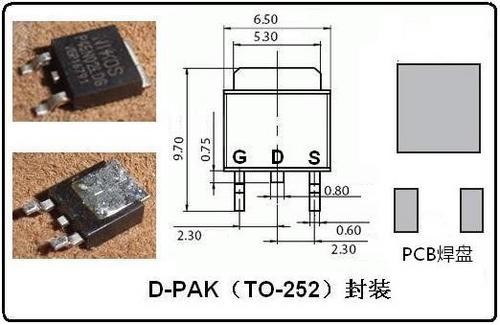

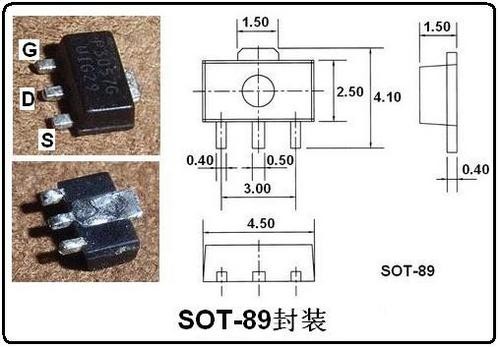

??? 2、SOT封裝

??? SOT(Small Out-Line Transistor)小外形晶體管封裝。這種封裝就是貼片型小功率晶體管封裝,比TO封裝體積小,一般用于小功率MOSFET。常見的規(guī)格有:

?

??? 主板上常用四端引腳的SOT-89 MOSFET。

?

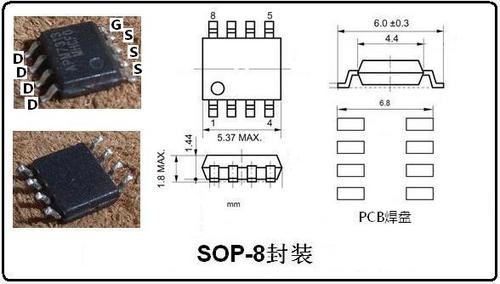

??? 3、SOP封裝

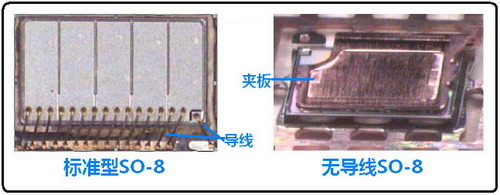

??? SOP(Small Out-Line Package)的中文意思是“小外形封裝”。SOP是表面貼裝型封裝之一,引腳從封裝兩側(cè)引出呈海鷗翼狀(L 字形)。材料有塑料和陶瓷兩種。SOP也叫SOL 和DFP。SOP封裝標(biāo)準(zhǔn)有SOP-8、SOP-16、SOP-20、SOP-28等等,SOP后面的數(shù)字表示引腳數(shù)。MOSFET的SOP封裝多數(shù)采用SOP-8規(guī)格,業(yè)界往往把“P”省略,叫SO(Small Out-Line )。

??? SO-8采用塑料封裝,沒有散熱底板,散熱不良,一般用于小功率MOSFET。

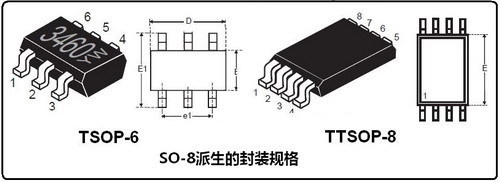

??? SO-8是PHILIP公司首先開發(fā)的,以后逐漸派生出TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、 SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)等標(biāo)準(zhǔn)規(guī)格。

??? 這些派生的幾種封裝規(guī)格中,TSOP和TSSOP常用于MOSFET封裝。

?

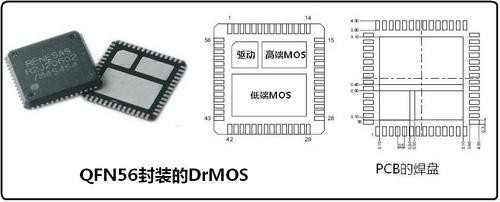

??? 5、QFN-56封裝

??? QFN(Quad Flat Non-leaded package)是表面貼裝型封裝之一,中文叫做四邊無引線扁平封裝,是一種焊盤尺寸小、體積小、以塑料作為密封材料的新興表面貼裝芯片封裝技術(shù)。現(xiàn)在多稱為LCC。QFN是日本電子機(jī)械工業(yè)會(huì)規(guī)定的名稱。封裝四邊配置有電極接點(diǎn),由于無引線,貼裝占有面積比QFP小,高度比QFP低。這種封裝也稱為LCC、PCLC、P-LCC等。QFN本來用于集成電路的封裝,MOSFET不會(huì)采用的。Intel提出的整合驅(qū)動(dòng)與MOSFET的DrMOS采用QFN-56封裝,56是指在芯片背面有56個(gè)連接Pin。

?

??? 二、最新封裝形式

??? 由于CPU的低電壓、大電流的發(fā)展趨勢,對MOSFET提出輸出電流大,導(dǎo)通電阻低,發(fā)熱量低散熱快,體積小的要求。MOSFET廠商除了改進(jìn)芯片生產(chǎn)技術(shù)和工藝外,也不斷改進(jìn)封裝技術(shù),在與標(biāo)準(zhǔn)外形規(guī)格兼容的基礎(chǔ)上,提出新的封裝外形,并為自己研發(fā)的新封裝注冊商標(biāo)名稱。

??? 下面分別介紹主要MOSFET廠商最新的封裝形式。

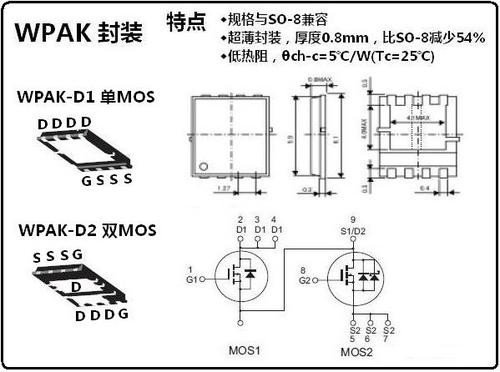

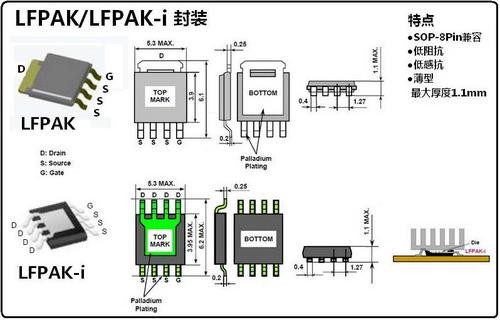

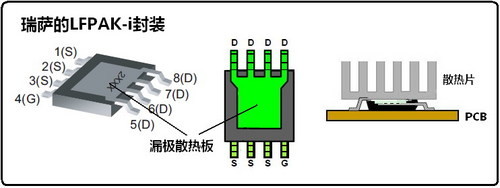

??? 1、瑞薩(RENESAS)的WPAK、LFPAK和LFPAK-I 封裝

??? WPAK是瑞薩開發(fā)的一種高熱輻射封裝,通過仿D-PAK封裝那樣把芯片散熱板焊接在主板上,通過主板散熱,使小形封裝的WPAK也可以達(dá)到D-PAK的輸出電流。WPAK-D2封裝了高/低2顆MOSFET,減小布線電感。

?

??? LFPAK和LFPAK-I是瑞薩開發(fā)的另外2種與SO-8兼容的小形封裝。LFPAK類似D-PAK比D-PAK體積小。LFPAK-i是將散熱板向上,通過散熱片散熱。

?

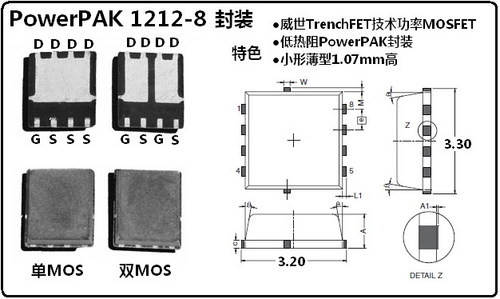

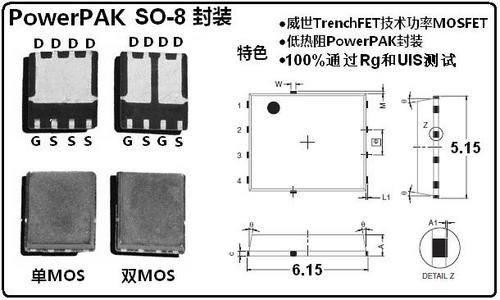

??? 2、威世(Vishay)的Power-PAK和Polar-PAK封裝

??? Power-PAK是威世公司注冊的MOSFET封裝名稱。Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8兩種規(guī)格。Polar PAK是雙面散熱的小形封裝。

?

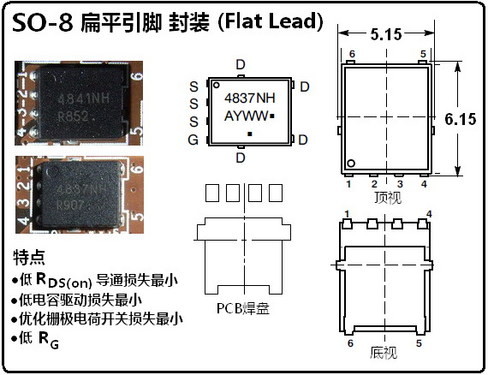

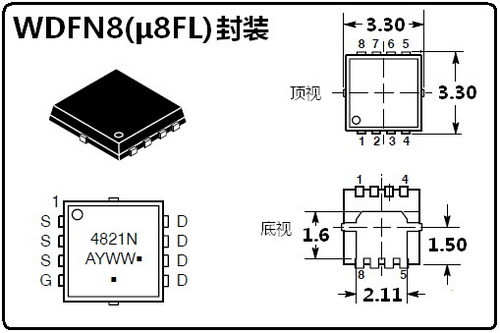

??? 3、安森美(Onsemi)的SO-8和WDFN8扁平引腳( Flat Lead)封裝

??? 安美森半導(dǎo)體開發(fā)了2種扁平引腳的MOSFET,其中SO-8兼容的扁平引腳被很多主板采用。

?

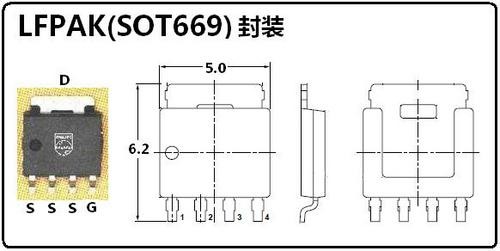

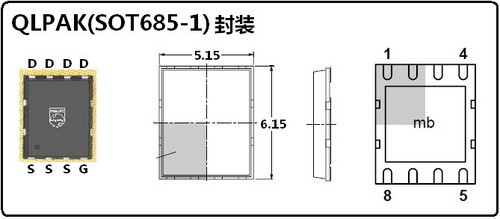

??? 4、菲利普(Philps)的LFPAK和QLPAK封裝

??? 首先開發(fā)SO-8的菲利普也有改進(jìn)SO-8的新封裝技術(shù),就是LFPAK和QLPAK。

?

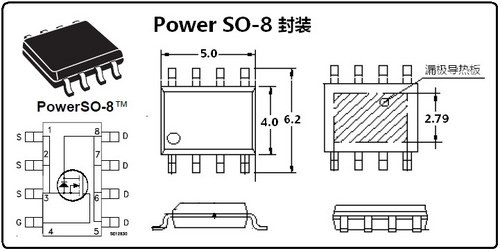

??? 5、意法(ST)半導(dǎo)體的PowerSO-8封裝

??? 法意半導(dǎo)體的SO-8改進(jìn)技術(shù)叫做Power SO-8。

?

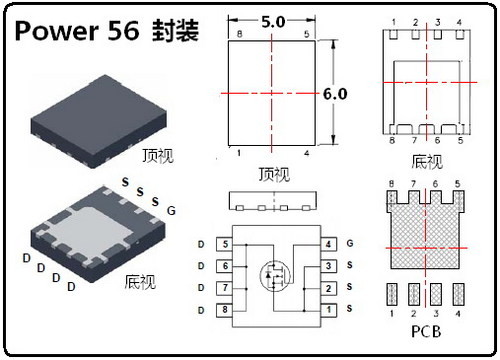

??? 6、飛兆(Fairchild)半導(dǎo)體的Power 56封裝

??? 飛兆半導(dǎo)體的SO-8改進(jìn)技術(shù)叫做Power 56。

?

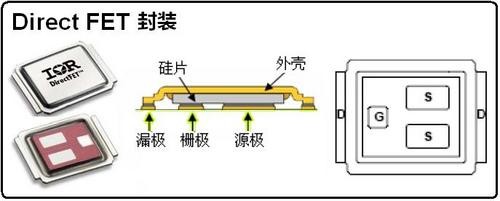

??? 6、國際整流器(IR)的Direct FET封裝

??? Direct FET封裝屬于反裝型的,漏極(D)的散熱板朝上,并覆蓋金屬外殼,通過金屬外殼散熱。

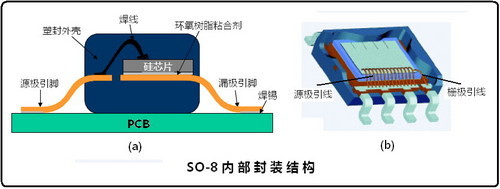

??? 三、內(nèi)部封裝技術(shù)

??? 前面介紹的最新封裝形式都是MOSFET的外部封裝。這些最新封裝還包括內(nèi)部封裝技術(shù)的改進(jìn),盡管這些新封裝技術(shù)的商標(biāo)名稱多種多樣,其內(nèi)部封裝技術(shù)改進(jìn)主要有三方面:一是改進(jìn)封裝內(nèi)部的互連技術(shù),二是增加漏極散熱板,三是改變散熱的熱傳導(dǎo)方向。

??? 1、封裝內(nèi)部的互連技術(shù)

??? 早期的標(biāo)準(zhǔn)封裝,包括TO,D-PAK、SOT、SOP,多采用焊線式的內(nèi)部互連,在CPU核心電壓較高,電流較小時(shí)期,這種封裝可以滿足需求。當(dāng)CPU供電進(jìn)展到低電壓、大電流時(shí)代,焊線式封裝就難以滿足了。以標(biāo)準(zhǔn)焊線式SO-8為例,作為小功率MOSFET封裝,發(fā)熱量很小,對芯片的散熱設(shè)計(jì)沒有特別要求。主板的局部小功率供電(風(fēng)扇調(diào)速)多采用這種SO-8的MOSFET。但用于現(xiàn)代的CPU供電就不能勝任了。這是由于焊線式SO-8的性能受到封裝電阻、封裝電感、PN結(jié)到PCB和外殼的熱阻等四個(gè)因素的限制。

?

??? 封裝電阻

??? MOSFET在導(dǎo)通時(shí)存在電阻(RDS(on)),這個(gè)電阻包括芯片內(nèi)PN結(jié)電阻和焊線電阻,其中焊線電阻占50%。RDS(on)是影響MOSFET性能的重要因素。

??? 封裝電感

??? 內(nèi)部焊線的引線框封裝的柵極、源極和漏極連接處會(huì)引入寄生電感。源極電感在電路中將會(huì)以共源電感形式出現(xiàn),對MOSFET的開關(guān)速度有著重大影響。

??? 芯片PN結(jié)到PCB的熱阻

??? 芯片的漏極粘合在引線框上,引線框被塑封殼包圍,塑料是熱的不良導(dǎo)體。漏極的熱傳導(dǎo)路徑是芯片→引線框→引腳→PCB,這么長的路徑必然是高熱阻。至于源極的熱傳導(dǎo)還要經(jīng)過焊線到PCB,熱阻更高。

??? 芯片PN結(jié)到外殼(封裝頂部)的熱阻

??? 由于標(biāo)準(zhǔn)的SO-8采用塑料包封,芯片到封裝頂部的傳熱路徑很差。

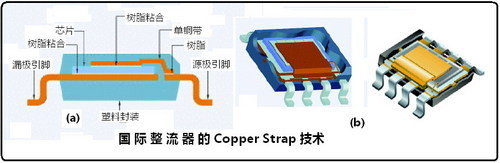

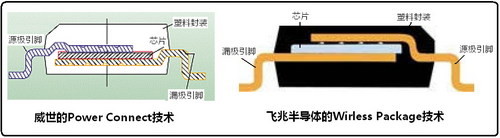

??? 上述四種限制對其電學(xué)和熱學(xué)性能有著極大的影響。隨著電流密度要求的提高,MOSFET廠商采用SO-8的尺寸規(guī)格,同時(shí)對焊線互連形式進(jìn)行改進(jìn),用金屬帶、或金屬夾板代替焊線,降低封裝電阻、電感和熱阻。

?

??? 國際整流器(IR)稱之為Copper Strap技術(shù),威世(Vishay)稱之為Power Connect 技術(shù),還有稱之為Wireless Package。

?

??? 據(jù)國際半導(dǎo)體報(bào)道,用銅帶取代焊線后,熱阻降低了10-20%,源極至封裝的電阻降低了61%。特別一提的是用銅帶替換14根2-mil金線,芯片源極電阻從1.1 m??降到 0.11 m?。

?

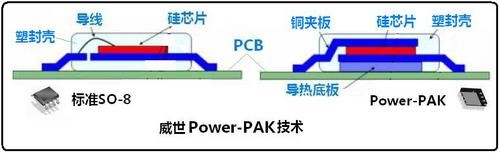

??? 2、漏極散熱板

??? 標(biāo)準(zhǔn)SO-8封裝采用塑料把芯片全部包圍,低熱阻的熱傳導(dǎo)通路只是芯片到PCB的引腳。底部緊貼PCB的是塑料外殼。塑料是熱的不良導(dǎo)體,影響漏極的散熱。封裝的散熱改進(jìn)自然是除去引線框下方的塑封混合物,讓引線框金屬結(jié)構(gòu)直接(或者加一層金屬板)與PCB接觸,并焊接到PCB焊盤上。它提供了大得多的接觸面積,把熱量從芯片上導(dǎo)走。這種結(jié)構(gòu)還有一個(gè)附帶的好處,即可以制成更薄的器件,因?yàn)樗芊獠牧系南档土似浜穸取?/P>

??? 威世的Power-PAK,法意半導(dǎo)體的Power SO-8,安美森半導(dǎo)體的SO-8 Flat Lead,瑞薩的WPAK、LFPAK,飛兆半導(dǎo)體的Power 56和Bottomless Package都采用這種散熱技術(shù)。

?

??? 3、改變散熱的熱傳導(dǎo)方向

??? Power-PAK封裝顯著減小了芯片到PCB的熱阻,實(shí)現(xiàn)芯片到PCB的高效率傳熱。不過,當(dāng)電流的需求繼續(xù)增大時(shí),PCB也將出現(xiàn)熱飽和,因此散熱技術(shù)的進(jìn)一步改進(jìn)是改變散熱方向,讓芯片的熱量傳導(dǎo)到散熱器而不是PCB。

??? 瑞薩的LFPAK-I 封裝,國際整流器的Direct FET封裝就是這種散熱技術(shù)。

?

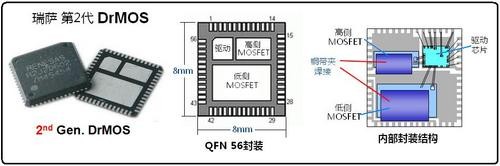

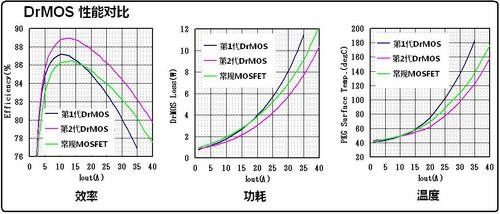

??? 四、整合驅(qū)動(dòng)IC的DrMOS

??? 傳統(tǒng)的主板供電電路采用分立式的DC/DC降壓開關(guān)電源,分立式方案無法滿足對更高功率密度的要求,也不能解決較高開關(guān)頻率下的寄生參數(shù)影響問題。隨著封裝、硅技術(shù)和集成技術(shù)的進(jìn)步,把驅(qū)動(dòng)器和MOSFET整合在一起,構(gòu)建多芯片模塊(MCM)已經(jīng)成為現(xiàn)實(shí)。。與分立式方案相比,多芯片模塊可以節(jié)省相當(dāng)可觀的空間并提高功率密度,通過對驅(qū)動(dòng)器和MOSFET的優(yōu)化提高電能轉(zhuǎn)換效率以及優(yōu)質(zhì)的DC電流。這就是稱之為DrMOS的新一代供電器件。

??? DrMOS的主要特點(diǎn)是:

??? - 采用QFN56無腳封裝,熱阻抗很低。

??? - 采用內(nèi)部引線鍵合以及銅夾帶設(shè)計(jì),盡量減少外部PCB布線,從而降低電感和電阻。

??? - 采用先進(jìn)的深溝道硅(trench silicon)MOSFET工藝,顯著降低傳導(dǎo)、開關(guān)和柵極電荷損耗。

??? - 兼容多種控制器,可實(shí)現(xiàn)不同的工作模式,支持APS(Auto Phase Switching)。

??? - 針對目標(biāo)應(yīng)用進(jìn)行設(shè)計(jì)的高度優(yōu)化。

????

??? 五、MOSFET發(fā)展趨勢

??? 伴隨計(jì)算機(jī)技術(shù)發(fā)展對MOSFET的要求,MOSFET封裝技術(shù)的發(fā)展趨勢是性能方面高輸出、高密度、高頻率、高效率,體積方面是更趨向小形化。

??? 下圖是瑞薩提供的低壓MOSFET封裝發(fā)展趨勢圖。

非常好我支持^.^

(67) 100%

不好我反對

(0) 0%

相關(guān)閱讀:

- [電子說] 國星光電SiC-MOSFET器件獲得AEC-Q101車規(guī)級認(rèn)證 2023-10-24

- [電子說] IGBT/FRD/MOSFET功率器件模塊材料介紹 2023-10-24

- [電子說] 不同功率的充電樁設(shè)計(jì)方案總結(jié) 2023-10-24

- [電子說] 攻克汽車熱管理挑戰(zhàn),安森美Top Cool MOSFET榮獲“金輯獎(jiǎng)2023中國汽車新供應(yīng)鏈百 2023-10-24

- [模擬技術(shù)] 龍騰半導(dǎo)體MOSFET在便攜儲(chǔ)能上的應(yīng)用 2023-10-23

- [電子說] 飛騰D2000國產(chǎn)核心板:引領(lǐng)傳統(tǒng)產(chǎn)業(yè)數(shù)字化改造,激發(fā)無限潛能 2023-10-23

- [電子說] 安森德超結(jié)(SJ)MOSFET在LED光源中的應(yīng)用 2023-10-23

- [電子說] MOSFET柵極電路電壓對電流的影響?MOSFET柵極電路電阻的作用? 2023-10-22

( 發(fā)表人:admin )