什么是MIS

什么是MIS

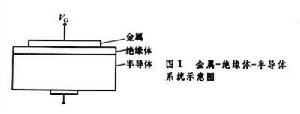

金屬-絕緣體-半導體(簡寫為 MIS)系統的三層結構如圖1所示。如絕緣層采用氧化物,則稱為金屬-氧化物-半導體(簡寫為MOS)系統。硅片上生長一層薄氧化膜后再覆蓋一層鋁,就是 最常見的MOS結構。60年代以來MIS系統無論在技術應用方面還是在物理研究方面都有著十分特殊的作用。

金屬-絕緣體-半導體系統

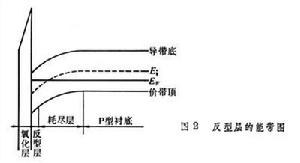

當半導體襯底接地,金屬層(通常稱為柵極)上施加電壓時,半導體表面形成電荷層。以P型半導體襯底為例,當柵壓為負,它會吸引空穴到半導體表面,使表面 形成帶正電荷的空穴積累層;當柵壓為正,它既有把多數載流子空穴從P型半導體表面排斥走的作用,又有吸引少數載流子電子到半導體表面的作用。當正柵壓較小 時,主要是空穴被排斥走,形成帶負電荷的耗盡層,負電荷來源于電離的受主,這時雖然也有電子被吸引到表面,但為數尚少。當正柵壓增大到超過一定的閾值電 壓,吸引到表面的電子濃度迅速增大,在表面形成電子導電層,因為其載流子和體內導電類型相反,因而稱為反型層。反型層與襯底之間被耗盡層隔開,如同PN結 一樣,稱為場感應結。圖2中給出了與反型層情況相應的能帶圖。

如果如圖3所示,在P型襯底的MOS系統中增加兩個N型區,分別稱為源(用 S表示)區和漏(用D表示)區,這就是N溝道的MOS晶體管。當柵壓低于閾值電壓時,由于源區和漏區被P型區隔開,源和漏間相當于兩個背靠的PN結,因 此,當源、漏間加一定電壓后,沒有明顯的電流,只有微量的PN結反向電流。但當柵極正電壓超過閾值電壓后,P型Si表面出現的反型層(N型層)把源區和漏 區溝通,形成導電溝通。這時再在源、漏之間加一定的電壓,就會有明顯的電流流過。也就是說,通過控制柵壓的極性和數值,可以使MOS晶體管分別處于導通或 截止的狀態,利用這一性質做成的MOS集成電路,可以實現各種邏輯功能。由于MOS集成電路具有工藝較簡單、結構尺寸較小、連線數目較少等優點,使之較易 實現大規模集成,因而是當前大規模集成電路中最重要的類型之一。

金屬-絕緣體-半導體系統

MIS系統實際上構成一個電容器,金屬層和半導體襯底是它的兩個極板。它與一般電容器的區別在于電容值并不是恒定的,因而可以引入微分電容C(V),它是偏壓V的函數,這個函數關系稱為MIS電容器的C-V特性。根據絕緣層的厚度、半導體襯底的摻雜濃度,從理論上很容易計算出C-V曲線,而實際測量得到的C-V曲線總是偏離理想的情況。這是因為在實際的 MIS電容的絕緣層中往往存在有各種電荷和在絕緣體和半導體的界面附近存在有界面態。正因為如此,可以通過對實際C-V曲線的分析,研究絕緣層中電荷和界面態的性質。金屬-SiO2-Si系統是研究最多的MIS結構,其中主要的電荷形式有:可動離子電荷(例如Na+,K+)、Si-SiO2界面固定正電荷、輻射電離的陷阱和界面態。基于掩蔽作用和鈍化作用發展起來的硅平面技術,是目前最重要的半導體工藝技術,在這里Si-SiO2系統成為半導體器件的基本組成部分。SiO2中的電荷以及Si-SiO2界面態,會影響器件的參數,特別是影響到器件長期使用的可靠性和穩定性。正是由于對金屬-SiO2-Si系統做了廣泛的研究,找到了減少以致消除各種電荷狀態不良影響的手段,才使得Si晶體管以及大規模集成電路得以有如此迅速的發展。

MOS系統的表面反型層厚度為幾埃至幾十埃,因而可以把反型層中的電子看成是二維的電子氣。近年來其中豐富的物理現象引起了很多物理學家的興趣。特別是 因為可以通過改變柵壓在同一樣品上使反型層中的電子濃度變化若干個數量級,為研究多電子效應隨濃度的變化提供了實驗數據。

參考書目

A. S.格羅夫著,齊建譯:《半導體器件物理與工藝》,科學出版社,北京,1976。(A.S.Grove,Physics and Technology of Semicondotor Device,John Wiley & Sons,New York,1967.)

以SiO2為柵介質時,叫MOS器件,這是最常使用的器件形式。歷史上也出現過以Al2O3為柵介質的MAS器件和以Si3N4為柵介質的MNS器件,以及以SiO2+Si3N4為柵介質的MNOS器件,統稱為金屬-絕緣柵-半導體器件--MIS器件。

以Al為柵電極時,稱鋁柵器件。以重摻雜多晶硅(Poly-Si)為柵電極時,稱硅柵器件。它是當前MOS器件的主流器件。硅柵工藝是利用重摻雜的多晶硅 來代替鋁做為MOS管的柵電極,使MOS電路特性得到很大改善,它使VTP下降1.1V,也容易獲得合適的VTN值并能提高開關速度和集成度。

硅柵工藝具有自對準作用,這是由于硅具有耐高溫的性質。柵電極,更確切的說是在柵電極下面的介質層,是限定源、漏擴散區邊界的擴散掩膜,使柵區與源、漏交 迭的密勒電容大大減小,也使其它寄生電容減小,使器件的頻率特性得到提高。另外,在源、漏擴散之前進行柵氧化,也意味著可得到淺結。 selfalignedpoly-siliconprocess自對準多晶硅工藝

鋁柵工藝為了保證柵金屬與漏極鋁引線之間有一定的間隔,要求漏擴散區面積要大些。而在硅柵工藝中覆蓋源漏極的鋁引線可重迭到柵區,這是因為有一絕緣層將柵區與源漏電極引線隔開,從而可使結面積減少30%~40%。

硅柵工藝還可提高集成度,這不僅是因為擴散自對準作用可使單元面積大為縮小,而且因為硅柵工藝可以使用“二層半布線”即一層鋁布線,一層重摻雜多晶硅布 線,一層重摻雜的擴散層布線。由于在制作擴散層時,多晶硅要起掩膜作用,所以擴散層不能與多晶硅層交叉,故稱為兩層半布線.鋁柵工藝只有兩層布線:一層鋁 布線,一層擴散層布線。硅柵工藝由于有兩層半布線,既可使芯片面積比鋁柵縮小50%又可增加布線靈活性。

當然,硅柵工藝較之鋁柵工藝復雜得多,需增加多晶硅淀積、等離子刻蝕工序,而且由于表面層次多,臺階比較高,表面斷鋁,增加了光刻的困難,所以又發展了以 Si3N4作掩膜的局部氧化LOCOS--Localoxidationonsilicon (又稱為MOSIC的局部氧化隔離工藝LocalOxidationIsolationforMOSIC),或稱等平面硅柵工藝。

擴散條連線由于其電容較大,漏電流也較大,所以盡量少用,一般是將相應管子的源或漏區加以延伸而成。擴散條也用于短連線,注意擴散條不能跨越多晶硅層,有 時把這層連線稱為“半層布線”。因硼擴散薄層電阻為30~120Ω/□,比磷擴散的R□大得多,所以硼擴散連線引入的分布電阻更為可觀,擴散連線的寄生電 阻將影響輸出電平是否合乎規范值,同時也因加大了充放電的串聯電阻而使工作速度下降。因此,在CMOS電路中,當使用硼擴散條做連線用時要考慮到這一點。

當 在NMOS的柵上施加相對于源的正電壓VGS時,柵上的正電荷在P型襯底上感應出等量的負電荷,隨著VGS的增加,襯底中接近硅-二氧化硅界面的表面處的 負電荷也越多。其變化過程如下:當VGS比較小時,柵上的正電荷還不能使硅-二氧化硅界面處積累可運動的電子電荷,這是因為襯底是P型的半導體材料,其中 的多數載流子是正電荷空穴,柵上的正電荷首先是驅趕表面的空穴,使表面正電荷耗盡,形成帶固定負電荷的耗盡層。

這時,雖然有VDS的存在,但因為沒有可運動的電子,所以,并沒有明顯的源漏電流出現。增加VGS,耗盡層向襯底下部延伸,并有少量的電子被吸引到表面, 形成可運動的電子電荷,隨著VGS的增加,表面積累的可運動電子數量越來越多。這時的襯底負電荷由兩部分組成:表面的電子電荷與耗盡層中的固定負電荷。如 果不考慮二氧化硅層中的電荷影響,這兩部分負電荷的數量之和等于柵上的正電荷的數量。當電子積累達到一定水平時,表面處的半導體中的多數載流子變成了電 子,即相對于原來的P型半導體,具有了N型半導體的導電性質,這種情況稱為表面反型。

根據晶體管理論,當NMOS晶體管表面達到強反型時所對應的VGS值,稱為NMOS晶體管的閾值電壓VTN(ThresholdvoltageforN- channeltransistor)。這時,器件的結構發生了變化,自左向右,從原先的n+-p-n+結構,變成了n+-n-n+結構,表面反型的區域 被稱為溝道區。在VDS的作用下,N型源區的電子經過溝道區到達漏區,形成由漏流向源的漏源電流。顯然,VGS的數值越大,表面處的電子密度越大,相對的 溝道電阻越小,在同樣的VDS的作用下,漏源電流越大。

當VGS大于VTN,且一定時,隨著VDS的增加,NMOS的溝道區的形狀將逐漸的發生變化。在VDS較小時,溝道區基本上是一個平行于表面的矩形,當 VDS增大后,相對于源端的電壓VGS和VDS在漏端的差值VGD逐漸減小,并且因此導致漏端的溝道區變薄,當達到VDS=VGS-VTN時,在漏端形成 了VGD=VGS-VDS=VTN的臨界狀態,這一點被稱為溝道夾斷點,器件的溝道區變成了楔形,最薄的點位于漏端,而源端仍維持原先的溝道厚度。器件處 于VDS=VGS-VTN的工作點被稱為臨界飽和點。

在逐漸接近臨界狀態時,隨著VDS的增加,電流的變化偏離線性,NMOS晶體管的電流-電壓特性發生彎曲。在臨界飽和點之前的工作區域稱為非飽和區,顯 然,線性區是非飽和區中VDS很小時的一段。繼續在一定的VGS條件下增加VDS(VDS>VGS-VTN),在漏端的導電溝道消失,只留下耗盡 層,溝道夾斷點向源端趨近。由于耗盡層電阻遠大于溝道電阻,所以這種向源端的趨近實際上位移值?L很小,漏源電壓中大于VGS-VTN的部分落在很小的一 段由耗盡層構成的區域上,有效溝道區內的電阻基本上維持臨界時的數值。因此,再增加源漏電壓VDS,電流幾乎不增加,而是趨于飽和。

這時的工作區稱為飽和區,左圖顯示了器件處于這種狀態時的溝道情況,右圖是完整的NMOS晶體管電流—電壓特性曲線。圖中的虛線是非飽和區和飽和區的分界線,VGS

雙極性晶體管的輸出特性曲線形狀與MOS器件的輸出特性曲線相似,但線性區與飽和區恰好相反。MOS器件的輸出特性曲線的參變量是VGS,雙極性晶體管的輸出特性曲線的參變量是基極電流IB。

衡量溝道長度調制的大小可以用厄萊(Early)電壓VA表示,它反映了飽和區輸出電流曲線上翹的程度。

非常好我支持^.^

(14) 93.3%

不好我反對

(1) 6.7%

相關閱讀:

- [電子說] 邁威通信MISCOM8220GX三層交換機強勢登場 2023-10-19

- [電子說] 您需要了解的有關下一個MISRA?標準的信息:MISRA C++ 2023?簡介 2023-08-25

- [光電顯示] QSFP-DD中CMIS協議和DDM功能解析 2023-08-22

- [電子說] QSFP-DD模塊CMIS協議和DDM知識解析 2023-08-17

- [電子說] QSFP-DD模塊的CMIS協議和DDM功能應用 2023-08-16

- [電子說] QSFP-DD模塊的CMIS協議和DDM功能詳細解析 2023-08-16

- [電子說] 什么是SPI?SPI通信的4種工作模式 2023-08-11

- [電子說] 靜態代碼分析器工具Helix QAC 2023.2: 提供 100% 的 MISRA C:2012 和 MISRA C:2023 規則 2023-07-31

( 發表人:admin )