什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

計(jì)數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時(shí)鐘脈沖的個(gè)數(shù),還可以實(shí)現(xiàn)分頻、定時(shí)、產(chǎn)生節(jié)拍脈沖和脈沖序列等。例如,計(jì)算機(jī)中的時(shí)序發(fā)生器、分頻器、指令計(jì)數(shù)器等都要使用計(jì)數(shù)器。

計(jì)數(shù)器的種類很多。按時(shí)鐘脈沖輸入方式的不同,可分為同步計(jì)數(shù)器和異步計(jì)數(shù)器;按進(jìn)位體制的不同,可分為二進(jìn)制計(jì)數(shù)器和非二進(jìn)制計(jì)數(shù)器;按計(jì)數(shù)過程中數(shù)字增減趨勢(shì)的不同,可分為加計(jì)數(shù)器、減計(jì)數(shù)器和可逆計(jì)數(shù)器。

二進(jìn)制異步計(jì)數(shù)器:

1.二進(jìn)制異步加計(jì)數(shù)器

電路結(jié)構(gòu)

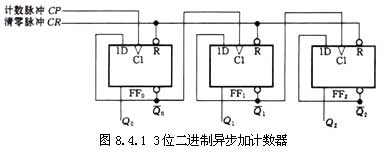

以三位二進(jìn)制異步加法計(jì)數(shù)器為例,如圖8.4.1所示。該電路由3個(gè)上升沿觸發(fā)的D觸發(fā)器組成,具有以下特點(diǎn):每個(gè)D觸發(fā)器輸入端接該觸發(fā)器Q 端信號(hào),因而Q n+1=Q n,即各D觸發(fā)器均處于計(jì)數(shù)狀態(tài);計(jì)數(shù)脈沖加到最低位觸發(fā)器的C端,每個(gè)觸發(fā)器的Q 端信號(hào)接到相鄰高位的C端。

(2)原理分析:

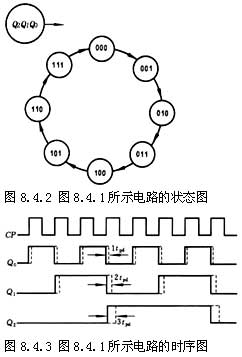

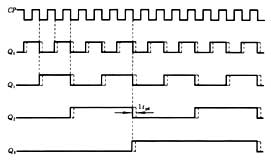

假設(shè)各觸發(fā)器均處于0態(tài),根據(jù)電路結(jié)構(gòu)特點(diǎn)以及D觸發(fā)器工作特性,不難得到其狀態(tài)圖和時(shí)序圖,它們分別如圖8.4.2和圖8.4.3所示。其中虛線是考慮觸發(fā)器的傳輸延遲時(shí)間tpd后的波形。

由狀態(tài)圖可以清楚地看到,從初始狀態(tài)000(由清零脈沖所置)開始,每輸入一個(gè)計(jì)數(shù)脈沖,計(jì)數(shù)器的狀態(tài)按二進(jìn)制遞增(加1),輸入第8個(gè)計(jì)數(shù)脈沖后,計(jì)數(shù)器又回到000狀態(tài)。因此它是23進(jìn)制加計(jì)數(shù)器,也稱模八(M=8)加計(jì)數(shù)器。

從時(shí)序圖可以清楚地看到Q0,Q1,Q2的周期分別是計(jì)數(shù)脈沖(CP)周期的2倍,4倍、8倍,也就是說Q0,Q1,Q2,分別對(duì)CP波形進(jìn)行了二分頻,四分頻,八分頻,因而計(jì)數(shù)器也可作為分頻器。

需要說明的是,由圖8.4.3中的虛線波形可知,在考慮各觸發(fā)器的傳輸延遲時(shí)間tpd時(shí),對(duì)于一個(gè)n 位的二進(jìn)制異步計(jì)數(shù)器來說,從一個(gè)計(jì)數(shù)脈沖(設(shè)為上升沿起作用)到來,到n 個(gè)觸發(fā)器都翻轉(zhuǎn)穩(wěn)定,需要經(jīng)歷的最長時(shí)間是ntpd ,為保證計(jì)數(shù)器的狀態(tài)能正確反應(yīng)計(jì)數(shù)脈沖的個(gè)數(shù),下一個(gè)計(jì)數(shù)脈沖(上升沿)必須在ntpd 后到來,因此計(jì)數(shù)脈沖的最小周期Tmin=ntpd 。

2.二進(jìn)制異步減計(jì)數(shù)器:

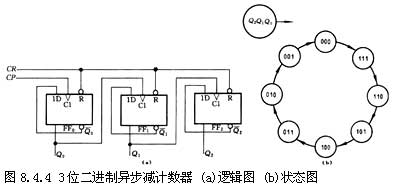

圖8.4.4是3位二進(jìn)制異步減計(jì)數(shù)器的邏輯圖和狀態(tài)圖。從初態(tài)000開始,在第一個(gè)計(jì)數(shù)脈沖作用后,觸發(fā)器FF0由0翻轉(zhuǎn)為1(Q0的借位信號(hào)),此上升沿使FF1也由0翻轉(zhuǎn)為1(Q1的借位信號(hào)),這個(gè)上升沿又使FF2 由0翻轉(zhuǎn)為1,即計(jì)數(shù)器由000變成了111狀態(tài)。在這一過程中,Q0向Q1進(jìn)行了借位,Q1向Q2進(jìn)行了借位。此后,每輸入1個(gè)計(jì)數(shù)脈沖,計(jì)數(shù)器的狀態(tài)按二進(jìn)制遞減(減1)。輸入第8個(gè)計(jì)數(shù)脈沖后,計(jì)數(shù)器又回到000狀態(tài),完成一次循環(huán)。因此,該計(jì)數(shù)器是23進(jìn)制(模8)異步減計(jì)數(shù)器,它同樣具有分頻作用。

綜上所述,可對(duì)二進(jìn)制異步計(jì)數(shù)器歸納出以下兩點(diǎn):

(1)n位二進(jìn)制異步計(jì)數(shù)器由n個(gè)處于計(jì)數(shù)工作狀態(tài)(對(duì)于D 觸發(fā)器,使Di=Qin;對(duì)于JK 觸發(fā)器,使Ji=Ki=1) 的觸發(fā)器組成。各觸發(fā)器之間的連接方式由加、減計(jì)數(shù)方式及觸發(fā)器的觸發(fā)方式?jīng)Q定。對(duì)于加計(jì)數(shù)器,若用上升沿觸發(fā)的觸發(fā)器組成,則應(yīng)將低位觸發(fā)器的Q 端與相鄰高一位觸發(fā)器的時(shí)鐘脈沖輸入端相連(即進(jìn)位信號(hào)應(yīng)從觸發(fā)器的Q 端引出);若用下降沿觸發(fā)的觸發(fā)器組成,則應(yīng)將低位觸發(fā)器的Q 端與相鄰高一位觸發(fā)器的時(shí)鐘脈沖輸入端連接。對(duì)于減計(jì)數(shù)器,各觸發(fā)器的連接方式則相反。

(2)在二進(jìn)制異步計(jì)數(shù)器中,高位觸發(fā)器的狀態(tài)翻轉(zhuǎn)必須在低一位觸發(fā)器產(chǎn)生進(jìn)位信號(hào)(加計(jì)數(shù))或借位信號(hào)(減計(jì)數(shù))之后才能實(shí)現(xiàn)。故又稱這種類型的計(jì)數(shù)器為串行計(jì)數(shù)器。也正因?yàn)槿绱耍惒接?jì)數(shù)器的工作速度較低。

8.4.2 二進(jìn)制同步計(jì)數(shù)器

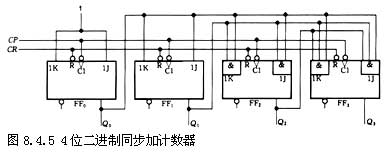

為了提高計(jì)數(shù)速度,可采用同步計(jì)數(shù)器,其特點(diǎn)是,計(jì)數(shù)脈沖同時(shí)接于各位觸發(fā)器的時(shí)鐘脈沖輸入端,當(dāng)計(jì)數(shù)脈沖到來時(shí),各觸發(fā)器同時(shí)被觸發(fā),應(yīng)該翻轉(zhuǎn)的觸發(fā)器是同時(shí)翻轉(zhuǎn)的,沒有各級(jí)延遲時(shí)間的積累問題。同步計(jì)數(shù)器也可稱為并行計(jì)數(shù)器。

1.二進(jìn)制同步加計(jì)數(shù)器

圖8.4.5是用JK觸發(fā)器(但已令J=K)組成的4位二進(jìn)制(M=16)同步加計(jì)數(shù)器。

由圖可見,各位觸發(fā)器的時(shí)鐘脈沖輸入端接同一計(jì)數(shù)脈沖CP ,各觸發(fā)器的驅(qū)動(dòng)方程分別為J0=K0=1,J1=K1=Q0、J2=K2=Q0Q1、 J3=K3=Q0Q1Q2 。

根據(jù)同步時(shí)序電路的分析方法,可得到該電路的狀態(tài)表,如表8.4.1所示。設(shè)從初態(tài)0000開始,因?yàn)镴0=K0=1,所以每輸入一個(gè)計(jì)數(shù)脈沖CP,最低位觸發(fā)器FF0就翻轉(zhuǎn)一次,其他位的觸發(fā)器FFi僅在 Ji=Ki=Qi-1Qi-2……Q0=1的條件下,在CP 下降沿到來時(shí)才翻轉(zhuǎn)。

圖8.4.6是圖8.4.5電路的時(shí)序圖,其中虛線是考慮觸發(fā)器的傳輸延遲時(shí)間tpd 后的波形。由此圖可知,在同步計(jì)數(shù)器中,由于計(jì)數(shù)脈沖CP 同時(shí)作用于各個(gè)觸發(fā)器,所有觸發(fā)器的翻轉(zhuǎn)是同時(shí)進(jìn)行的,都比計(jì)數(shù)脈沖CP 的作用時(shí)間滯后一個(gè)tpd ,因此其工作速度一般要比異步計(jì)數(shù)器高。

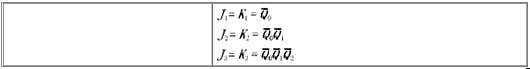

應(yīng)當(dāng)指出的是,同步計(jì)數(shù)器的電路結(jié)構(gòu)較異步計(jì)數(shù)器復(fù)雜,需要增加一些輸入控制電路,因而其工作速度也要受這些控制電路的傳輸延遲時(shí)間的限制。如果將圖8.4.5電路中觸發(fā)器FF1、FF2和FF3的驅(qū)動(dòng)信號(hào)分別改為

即可構(gòu)成4位二進(jìn)制同步減計(jì)數(shù)器.

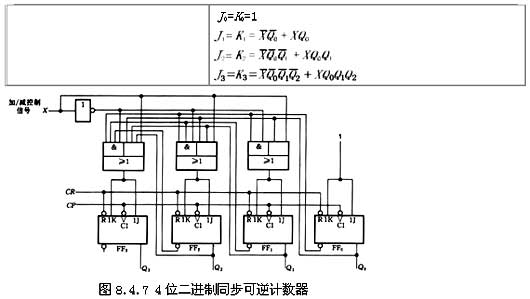

2.二進(jìn)制同步可逆計(jì)數(shù)器:

實(shí)際應(yīng)用中,有時(shí)要求一個(gè)計(jì)數(shù)器即能作加計(jì)數(shù)又能作減計(jì)數(shù)。同時(shí)兼有加和減兩種計(jì)數(shù)功能的計(jì)數(shù)器稱為可逆計(jì)數(shù)器。

4位二進(jìn)制同步可逆計(jì)數(shù)器如圖8.4.7所示,它是在前面介紹的4位二進(jìn)制同步加和減計(jì)數(shù)器的基礎(chǔ)上,增加一控制電路構(gòu)成的。由圖可知,各觸發(fā)器的驅(qū)動(dòng)方程分別為

當(dāng)加/減控制信號(hào)X=1時(shí),F(xiàn)F1-FF3中的各J、K 端分別與低位各觸發(fā)器的Q 端接通,進(jìn)行加計(jì)數(shù);當(dāng)X=0時(shí),各J、K 端分別與低位各觸發(fā)器的Q 端接通,進(jìn)行減計(jì)數(shù),實(shí)現(xiàn)了可逆計(jì)數(shù)器的功能

由于雙穩(wěn)態(tài)觸發(fā)器有“1“和”0“兩個(gè)狀態(tài),所以一個(gè)觸發(fā)器可以表示移位二進(jìn)制數(shù)。如果要表示n位二進(jìn)制數(shù),就得用n個(gè)觸發(fā)器。

??? 下表是四位二進(jìn)制加法計(jì)數(shù)器得狀態(tài)表,用四個(gè)雙穩(wěn)態(tài)觸發(fā)器,它們具有計(jì)數(shù)功能:

??? 1.異步二進(jìn)制加法計(jì)數(shù)器

| 計(jì)數(shù)脈沖數(shù) | 二進(jìn)制數(shù) | 十進(jìn)制數(shù) | |||

| Q3 | Q2 | Q1 | Q0 | ||

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 |

| 4 | 0 | 1 | 0 | 0 | 4 |

| 5 | 0 | 1 | 0 | 1 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 |

| 11 | 1 | 0 | 1 | 1 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 |

| 16 | 0 | 0 | 0 | 0 | 0 |

??? 由上表可見,每來一個(gè)計(jì)數(shù)脈沖,最低位觸發(fā)器翻轉(zhuǎn)一次;而高位觸發(fā)器是在相鄰得低位觸發(fā)器從“1“變位”0“進(jìn)位時(shí)翻轉(zhuǎn)。因此,可用四個(gè)主從型JK觸發(fā)器來組成四位異步二進(jìn)制加法計(jì)數(shù)器,如圖22.3.所示。每個(gè)觸發(fā)器的J,K端懸空,相當(dāng)于”1“,故具有計(jì)數(shù)功能。觸發(fā)器的進(jìn)位脈沖從Q端輸出送到相鄰高位觸發(fā)器的C端,這符合主從型觸發(fā)器在輸入正脈沖的下降沿觸發(fā)的特點(diǎn)。圖22.3.2是它的工作波形圖。由于計(jì)數(shù)脈沖不是同時(shí)加到各位觸發(fā)器的C端,而只加到最低位觸發(fā)器,其他各位觸發(fā)器則由相鄰低位觸發(fā)器輸出的進(jìn)位脈沖來觸發(fā),因此它們狀態(tài)的變化有先有后,是異步的,稱為異步加法計(jì)數(shù)器。

??? 2.同步二進(jìn)制加法計(jì)數(shù)器

???? 如果計(jì)數(shù)器還是用四個(gè)主從型JK觸發(fā)器組成,根據(jù)上表可得出各位觸發(fā)器的J,K端的邏輯關(guān)系式:

???? ![]()

???? ![]()

???? ![]()

???? ![]()

??? 由上述邏輯關(guān)系式可得出上圖所示的四位同步二進(jìn)制加法計(jì)數(shù)器的邏輯圖。由于計(jì)數(shù)脈沖同時(shí)加到各位觸發(fā)器的C端,它們的狀態(tài)變換和計(jì)數(shù)脈沖同步。

非常好我支持^.^

(102) 21.3%

不好我反對(duì)

(378) 78.7%

相關(guān)閱讀:

- [電子說] STM32基礎(chǔ)知識(shí):定時(shí)器的定時(shí)計(jì)數(shù)功能 2023-10-24

- [電子說] 脈沖定時(shí)器時(shí)間未到而在此觸發(fā)IN端則會(huì)重新計(jì)時(shí)是否正確?為什么? 2023-10-24

- [電子說] 請(qǐng)問異步FIFO的溢出操作時(shí)怎么樣判斷的? 2023-10-18

- [電子說] 嵌入式狀態(tài)機(jī)編程-QP狀態(tài)機(jī)框架基本知識(shí)介紹 2023-10-18

- [電子說] 什么是奇校驗(yàn)和偶校驗(yàn)?常見的奇偶校驗(yàn)方式有哪些? 2023-10-17

- [電子說] IPv6地址如何劃分?這篇文章看完必懂! 2023-10-17

- [電子說] 數(shù)字電路中的計(jì)數(shù)器詳解 2023-10-17

- [電子說] 開放二進(jìn)制翻譯聯(lián)盟,推動(dòng)RISC-V實(shí)現(xiàn)跨架構(gòu)應(yīng)用運(yùn)行 2023-10-17

( 發(fā)表人:admin )