定點(diǎn)運(yùn)算器的基本結(jié)構(gòu)(圖解篇)

定點(diǎn)運(yùn)算器的基本結(jié)構(gòu)(圖解篇)

運(yùn)算器包括ALU\陣列乘除器\寄存器\多路開關(guān)\三態(tài)緩沖器\數(shù)據(jù)總線等邏輯部件。

運(yùn)算器的設(shè)計(jì),主要是圍繞ALU和寄存器同數(shù)據(jù)總線之間如何傳送操作數(shù)和運(yùn)算結(jié)果進(jìn)行的。

在決定方案時,需要考慮數(shù)據(jù)傳送的方便性和操作速度,在微型機(jī)和單片機(jī)中還要考慮在硅片上制作總線的工藝。 計(jì)算機(jī)的運(yùn)算器大體有如下三種結(jié)構(gòu)形式:

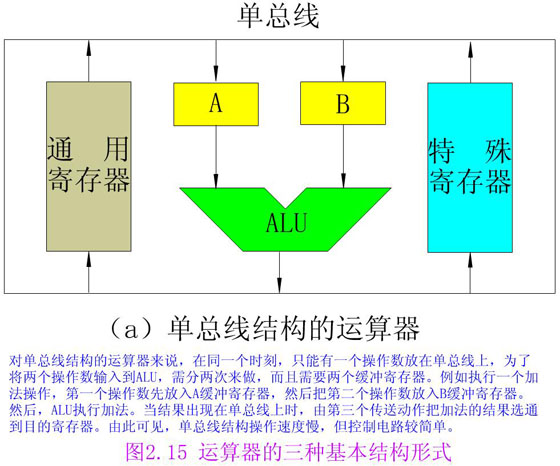

1.單總線結(jié)構(gòu)的運(yùn)算器

單總線結(jié)構(gòu)的運(yùn)算器如(a)所示。由于所有部件都接到同一總線上,所以數(shù)據(jù)可以在任何兩個寄存器之間,或者在任一個寄存器和ALU之間傳送。如果具有陣列乘法器或除法器,那么它們所處的位置應(yīng)與ALU相當(dāng)。對這種結(jié)構(gòu)的運(yùn)算器來說,在同一時間內(nèi),只能有一個操作數(shù)放在單總線上。為了把兩個操作數(shù)輸入到ALU,需要分兩次來做,而且還需要A,B兩個緩沖寄存器。這種結(jié)構(gòu)的主要缺點(diǎn)是操作速度較慢。雖然在這種結(jié)構(gòu)中輸入數(shù)據(jù)和操作結(jié)果需要三次串行的選通操作,但它并不會對每種指令都增加很多執(zhí)行時間。只有在對全都是CPU寄存器中的兩個操作數(shù)進(jìn)行操作時,單總線結(jié)構(gòu)的運(yùn)算器才會造成一定的時間損失。但是由于它只控制一條總線,故控制電路比較簡單。

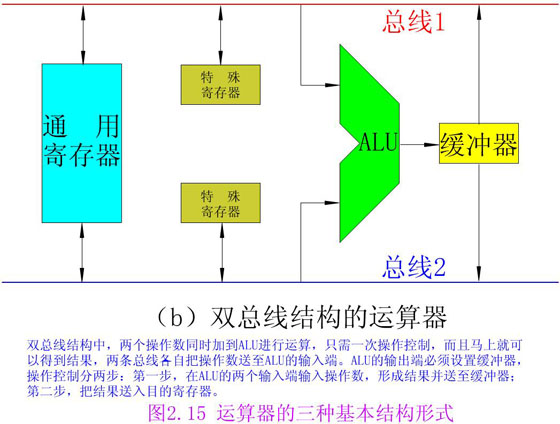

2.雙總線結(jié)構(gòu)的運(yùn)算器

雙總線結(jié)構(gòu)的運(yùn)算器如(b)所示。在這種結(jié)構(gòu)中,兩個操作數(shù)同時加到ALU進(jìn)行運(yùn)算,只需一次操作控制,而且馬上就可以得到運(yùn)算結(jié)果。圖中,兩條總線各自把其數(shù)據(jù)送至ALU的輸入端。特殊寄存器分為兩組,它們分別與一條總線交換數(shù)據(jù)。這樣,通用寄存器中的數(shù)就可進(jìn)入到任一組特殊寄存器中去,從而使數(shù)據(jù)傳送更為靈活。ALU的輸出不能直接加到總線上去。這是因?yàn)椋?dāng)形成操作結(jié)果的輸出時,兩條總線都被輸入數(shù)占據(jù),因而必須在ALU輸出端設(shè)置緩沖寄存器。為此,操作的控制要分兩步完成:

(1)在ALU的兩個輸入端輸入操作數(shù),形成結(jié)果并送入緩沖寄存器;

(2)把結(jié)果送入目的寄存器。假如在總線1,2和ALU輸入端之間再各加一個輸入緩沖寄存器,并把兩個輸入數(shù)先放至這兩個緩沖寄存器,那么,ALU輸出端就可以直接把操作結(jié)果送至總線1或總線2上去。

3.三總線結(jié)構(gòu)的運(yùn)算器

三總線結(jié)構(gòu)的運(yùn)算器如演示(C)所示。在三總線結(jié)構(gòu)中,ALU的兩個輸入端分別由兩條總線供給,而ALU的輸出則與第三條總線相連。這樣,算術(shù)邏輯操作就可以在一步的控制之內(nèi)完成。由于ALU本身有時間延遲,所以打入輸出結(jié)果的選通脈沖必須考慮到包括這個延遲。另外,設(shè)置了一個總線旁路器。如果一個操作數(shù)不需要修改,而直接從總線2傳送到總線3,那么可以通過控制總線旁路器把數(shù)據(jù)傳出;如果一個操作數(shù)傳送時需要修改,那么就借助于ALU。很顯然,三總線結(jié)構(gòu)的運(yùn)算器的特點(diǎn)是操作時間快。

?

非常好我支持^.^

(213) 30%

不好我反對

(496) 70%

相關(guān)閱讀:

- [電子說] 計(jì)算機(jī)系統(tǒng)的硬件組成和主要部件 2024-09-10

- [電子說] 微分器在濾波器設(shè)計(jì)中的作用 2024-07-19

- [電子說] 運(yùn)算器與控制器主要作用是什么 2024-06-30

- [電子說] cpu的運(yùn)算器和控制器的作用是什么 2024-06-30

- [電子說] cpu控制器和運(yùn)算器組成的部件有哪些 2024-06-30

- [電子說] 優(yōu)秀的Verilog/FPGA開源項(xiàng)目-浮點(diǎn)運(yùn)算器(FPU)介紹 2024-04-26

- [處理器/DSP] 一文詳解CPU概念及運(yùn)作原理 2024-01-16

- [處理器/DSP] cpu處理器的基本結(jié)構(gòu)有哪些 2023-10-30

( 發(fā)表人:admin )