核心算法 - 跳頻通信中的抗干擾同步算法研究

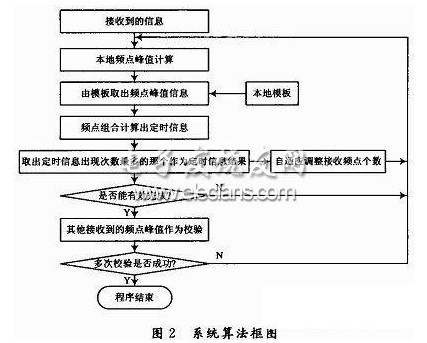

本文算法主要分為以下幾個部分,系統框圖如圖2所示。

3.1 接收端峰值的計算

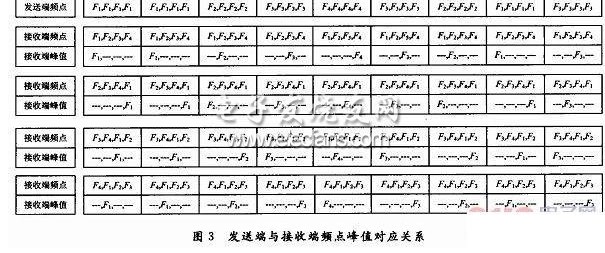

接收端以4倍發端速度在F1,F2,F3,F4四個頻點上進行循環,并且對接收到的信號進行下變頻,求出其能量,同時記下峰值出現的時刻值,由發送端同步頻點序列的設計可知,同一頻點連續的峰值個數不會超過兩個,此一點是去除單頻干擾的信息的簡單方法。如圖3所示。

3.2 接收端峰值信息模板

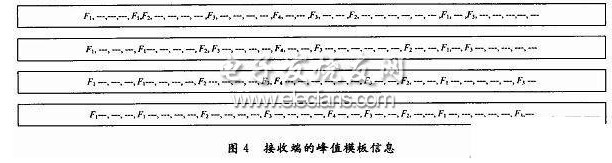

根據發端頻點序列,設計接收端4個模板序列,分別代表本地接收頻點與發端頻點的四種對齊方式,如圖4所示。其中F1~F4代表4個頻點的峰值,一代表沒有峰值出現的情況。這4個模板代表了接收端4種可能的與發送端頻點對齊產生峰值信息的組合形式。用本地實際收到的頻點峰值信息組合與4個模板的比較,可以迅速地確定收到的頻點峰值信息在序列中的位置,同時給出同步跳轉隨機跳的時間信息。

3.3 接收端頻點峰值信息組合

由設計的發送端序列的性質可知,接收端頻點峰值的任意組合均可正確地給出同步跳轉隨機跳的時間信息,所以為了充分利用得到的頻點信息,提高抗干擾能力,故對收到的頻點峰值信息進行組合。每收到一個新的頻點峰值信息以一定的概率與之前收到的頻點峰值信息進行組合,保證最先收到的頻點峰值信息有最大的權重。

3.4 利用頻點信息的不同組合計算時間信息

由3.3節得到的各種頻點峰值信息的組合分別和本地產生的4個模板進行滑動相關,得到組合序列在模板中的位置,從而得到同步跳轉隨機跳時所需要的時間信息。由于正確的頻點峰值信息的任意組合,他們在序列中所指示的位置是確定的,干擾頻點的峰值信息他們的組合在序列中所指示的位置是不確定的,是發散的。所以當接收到一定數量的頻點峰值信息后,將這些峰值信息進行全組合,然后在序列中搜索他們所指示的跳轉位置,取這一步中指示跳轉位置最多的那個作為同步跳轉隨機跳的跳轉位置。

在這步中,由于全組合的數量隨著峰值信息的增多快速增長,計算量也隨著顯著增長。為了減小計算量,在保證抗干擾性能的前提下,采用一種參與計算的頻點峰值信息數量自適應的方法,即以現有頻點峰值信息的全組合所指示的跳轉位置是否收斂為依據,若不能夠明顯收斂(此處以指示收斂位置是其他位置數量的3倍以上為明顯收斂),則再接收一個頻點峰值信息參與組合和計算,直到滿足明顯收斂要求為止。

3.5 剩余的頻點信息作為校驗

由3.4節得到了所需要的同步跳轉隨機跳的時間信息,在這之后收到的頻點峰值信息可以作為上一步得到的時間信息正確性的校驗。

- 第 1 頁:跳頻通信中的抗干擾同步算法研究

- 第 2 頁:核心算法

- 第 3 頁:性能分析及仿真結果

本文導航

非常好我支持^.^

(1) 50%

不好我反對

(1) 50%

相關閱讀:

- [PCB設計] PCB設計原則和抗干擾措施 2023-10-18

- [電子說] PLC控制器的主要抗干擾措施 2023-10-18

- [PCB設計] ?電源PCB設計抗干擾、EMC部分指南 2023-10-17

- [電子說] 如何解決PLC控制系統抗干擾問題 2023-10-17

- [電子說] 智能門鎖產品中應用的抗干擾低功耗觸摸感應芯片 2023-10-17

- [電子說] ESD抗干擾測試是什么?防止ESD的常見方法有哪些 2023-10-08

- [電子說] 紅外光學系統抗干擾的主要方法 2023-09-26

- [電子說] X2安規電容在電源中的三大作用,除了抗干擾它還能做什么? 2023-09-22

( 發表人:彭菁 )