8086cpu由哪兩部分組成_8086CPU內部結構圖分享 - 全文

8086概述

Intel8086是一個由Intel于1978年所設計的16位微處理器芯片,是x86架構的鼻祖。不久之后,Intel就推出了Intel8088(一個擁有8根外部數據總線的微處理器)。它是以8080和8085的設計為基礎,擁有類似的寄存器組,但是數據總線擴充為16位。總線界面單元(BusInterfaceUnit)透過6字節預存(prefecth)的隊列(queue)位指令給執行單元(ExecutionUnit),所以取指令和執行是同步的,8086CPU有20條地址線,可直接尋址1MB的存儲空間,每一個存儲單元可以存放一個字節(8位)二進制信息。

8086微處理器的性能特點

16位的內部結構,16位雙向數據信號線;

20位地址信號線,可尋址1M字節存儲單元;

較強的指令系統;

利用第16位的地址總線來進行I/O端口尋址,可尋址64K個I/O端口;

中斷功能強,可處理內部軟件中斷和外部中斷,中斷源可達256個;

8086cpu由哪兩部分組成

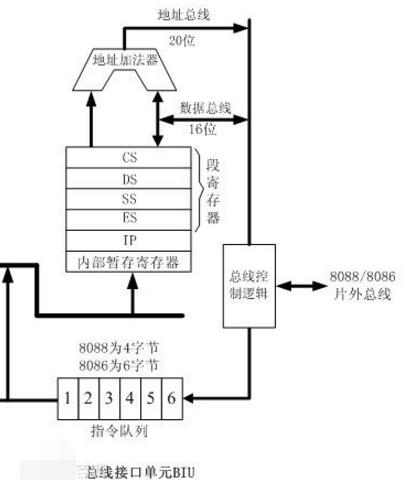

1、總線接口單元

總線接口部件由下列各部分組成

⑴4個段地址寄存器:

CS(codesegment)——16位的代碼段寄存器;

DS(datasegment)——16位的數據段寄存器;

ES(extrasegment)——16位的擴展段寄存器;

SS(stacksegment)——16位的堆棧段寄存器;

⑵16位的指令指針寄存器IP;

⑶20位的地址加法器;

⑷6字節的指令隊列緩沖器。

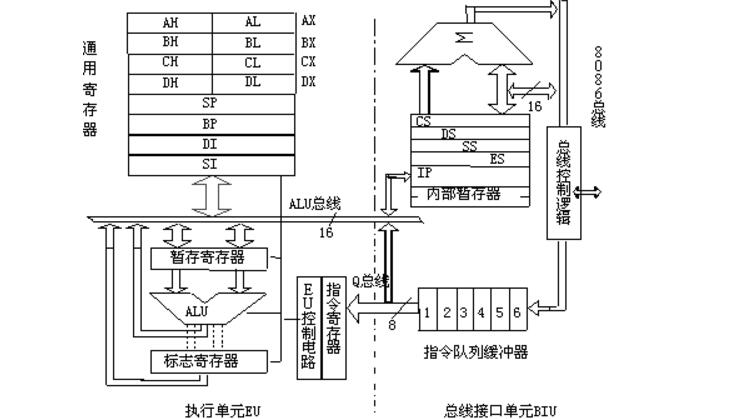

2、執行單元

執行部件由下列幾個部分組成:

⑴8個通用寄存器:即AX、BX、CX、DX,BP,SP,SI,DI;

其中,4個數據寄存器:AX、BX、CX、DX;

2個地址指針寄存器:BP(basepointer),SP(stackpointer);

2個變址寄存器:SI(sourceindex),DI(destinationindex);

⑵標志寄存器FR(flagsregister);

⑶算術邏輯單元ALU(arithmeticlogicunit)。

EU負責全部指令的執行,同時向BIU輸出數據(操作結果),并對寄存器和標志寄存器進行管理。在ALU中進行16位運算,數據傳送和處理均在EU控制下執行。

8086cpu結構圖

8086CPU內部結構圖分享

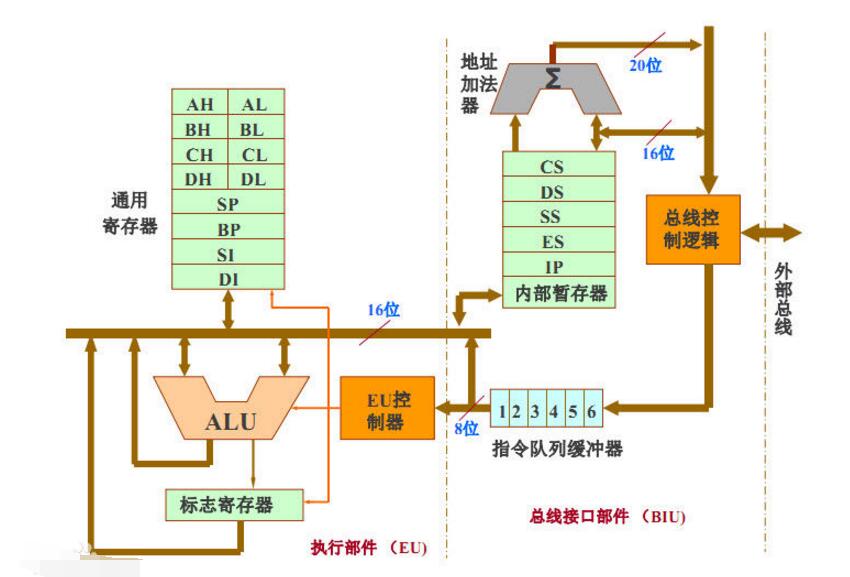

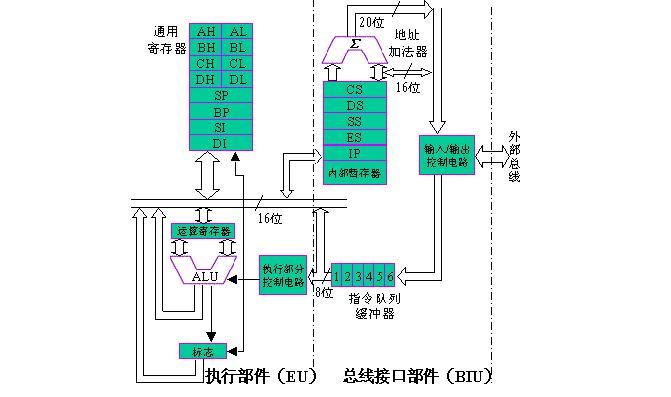

如圖,8086CPU從功能上劃分成兩部分:總線接口單元BIU(BusInterfaceUnit)和執行單元EU(ExecutionUnit)。

EU的組成部分:16位通用寄存器組(AX,BX,CX,DX,SP,BP,SI,DI)、算術邏輯單元(ALU)、標志寄存器(FLAG)、操作控制器電路。

BIU的組成部分:段寄存器組(CS,DS,SS,ES)、指令指針(IP)、地址加法器、指令隊列緩沖器、總線接口控制邏輯。

執行單元的功能:

指令譯碼

指令執行————————-在ALU中完成

暫存中間運算結果—————-通用寄存器

保存運算結果特征—————-標志寄存器flags

總線接口單元的功能:

從內存中取指令到指令預取隊列

負責與內存或輸入/輸出接口之間的數據傳送

在執行轉移程序時,BIU使指令預取隊列復位,從指定的新地址取指令,并立即傳給執行單元執行。

8086工作原理圖

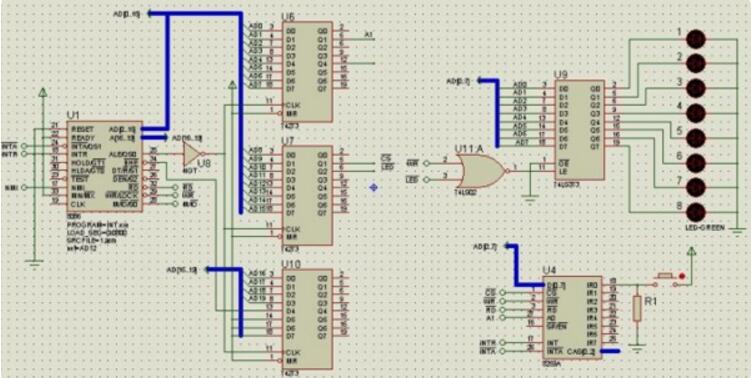

8086CPU的兩種工作模式

為了適應各種使用場合,在設計8086CPU芯片時,就考慮了其應能夠使它工作在兩種模式下,即最小模式與最大模式。

所謂最小模式,就是系統中只有一個8086微處理器,在這種情況下,所有的總線控制信號,都是直接由8086CPU產生的,系統中的總線控制邏輯電路被減到最少,該模式適用于規模較小的微機應用系統。

最大模式是相對于最小模式而言的,最大模式用在中、大規模的微機應用系統中,在

最大模式下,系統中至少包含兩個微處理器,其中一個為主處理器,即8086/8086CPU,其它的微處理器稱之為協處理器,它們是協助主處理器工作的。

與8086CPU配合工作的協處理器有兩類,一類是數值協處理器8087另一類是輸入/輸出協處理器8089。

8087是一種專用于數值運算的協處理器,它能實現多種類型的數值運算,如高精度的整型和浮點型數值運算,超越函數(三角函數、對數函數)的計算等,這些運算若用軟件的方法來實現,將耗費大量的機器時間。換句話說,引入了8087協處理器,就是把軟件功能硬件化,可以大大提高主處理器的運行速度。

8089協處理器,在原理上有點象帶有兩個DMA通道的處理器,它有一套專門用于輸入/輸出操作的指令系統,但是8089又和DMA控制器不同,它可以直接為輸入/輸出設備服務,使主處理器不再承擔這類工作。所以,在系統中增加8089協處理器之后,會明顯提高主處理器的效率,尤其是在輸入/輸出操作比較頻繁的系統中。

8086的存儲器組織

1.存儲容量

8086有20根地址總線,因此,它可以直接尋址的存儲器單元數為220=1Mbyte

2.物理地址

8086可直接尋址1Mbyte的存儲空間,其地址區域為00000H—FFFFFH,與存儲單元一一對應的20位地址,我們稱之為存儲單元的物理地址。

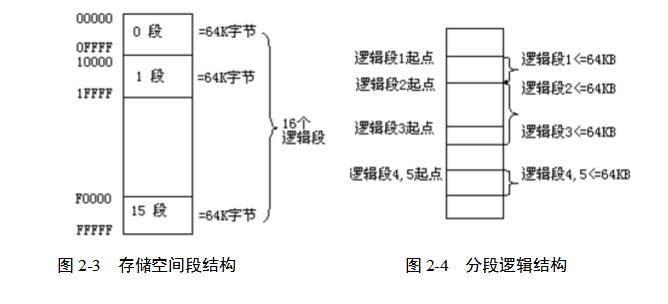

3.存儲器的分段及段地址

由于CPU內部的寄存器都是16位的,為了能夠提供20位的物理地址,系統中采用了存儲器分段的方法。規定存儲器的一個段為64KB,由段寄存器來確定存儲單元的段地址,由指令提供該單元相對于相應段起始地址的16位偏移量。

這樣,系統的整個存儲空間可分為16個互不重疊的邏輯段,如圖2-3所示。存儲器的每個段的容量為64KB,并允許在整個存儲空間內浮動,即段與段之間可以部分重疊、完全重疊、連續排列,非常靈活,如圖2-4所示。

4.偏移地址

偏移地址是某存儲單元相對其所在段起始位臵的偏移字節數,或簡稱偏移量。它是一個16位的地址,根據指令的不同,它可以來自于CPU中不同的16位寄存器(IP、SP、BP、SI、DI、BX等)。

5.物理地址的形成

物理地址是由段地址與偏移地址共同決定的,段地址來自于段寄存器(CS、DS、ES、SS),是十六位地址,由段地址及偏移地址計算物理地址的表達式如下:

物理地址=段地址×16+偏移地址

例如:系統啟動后,指令的物理地址由CS的內容與IP的內容共同決定,由于系統啟動的CS=0FFFFH,IP=0000H,所以初始指令的物理地址為0FFFF0H,我們可以在0FFFF0H單元開始的幾個單元中,固化一條無條件轉移指令的代碼,即轉移到系統初始化程序部分。

6.存儲器分段組織帶來存儲器管理的新特點

首先,在程序代碼量、數據量不是太大的情況下,可使它們處于同一段內,即使它們在64Kbyte的范圍內,這樣可以減少指令的長度,提高指令運行的速度;

其次,內存分段為程序的浮動分配創造了條件;

第三,物理地址與形式地址并不是一一對應的,舉例:6832H:1280H,物理地址為695A0H。

第四,各個分段之間可以重疊

7.特殊的內存區域

8088/8086系統中,有些內存區域的作用是固定的,用戶不能隨便使用,如:中斷矢量區:00000H—003FFH共1K字節,用以存放256種中斷類型的中斷矢量,每個中斷矢量占用4個字節,共256×4=1024=1K

顯示緩沖區:B0000H—B0F9FH約4000(25×80×2)字節,是單色顯示器的顯示緩沖區,存放文本方式下,所顯示字符的ASCII碼及屬性碼;B8000H—BBF3FH約16K字節,是彩色顯示器的顯示緩沖區,存放圖形方式下,屏幕顯示象素的代碼。

啟動區:FFFF0H—FFFFFH共16個單元,用以存放一條無條件轉移指令的代碼,轉移到系統的初始化部分。

- 第 1 頁:8086cpu由哪兩部分組成_8086CPU內部結構圖分享

- 第 2 頁:8086CPU內部結構圖分享

- 第 3 頁:8086的存儲器組織

本文導航

非常好我支持^.^

(22) 44.9%

不好我反對

(27) 55.1%

相關閱讀:

- [電子說] 單片機的IO口不夠用了怎么辦?如何擴展單片機的IO口? 2023-10-24

- [工業控制] 三菱和西門子PLC區別及優勢分析 2023-10-23

- [電子說] 如果FPGA/微處理器上只剩下一個GPIO,該如何進行模擬測量? 2023-10-21

- [存儲技術] 全面解析存儲芯片技術知識 2023-10-19

- [處理器/DSP] ARM微處理器對異常中斷的響應過程 2023-10-18

- [電子說] C語言中位、字節和字的定義 整數類型與浮點數類型的比較 2023-10-18

- [電子說] 氮化鎵晶體管簡化大電流電機驅動逆變器設計 2023-10-18

- [PCB設計] SMT技術之CSP及無鉛技術 2023-10-17

( 發表人:姚遠香 )