7nm 工藝制程介紹 哪些處理器用到了7nm 工藝?

7nm 工藝制程

7納米制程節點將是半導體廠推進摩爾定律(Moore’s?Law)的下一重要關卡。半導體進入7納米節點后,前段與后段制程皆將面臨更嚴峻的挑戰,半導體廠已加緊研發新的元件設計架構,以及金屬導線等材料,期兼顧尺寸、功耗及運算效能表現。?

臺積電預告2017年第二季10納米芯片將會量產,7納米制程的量產時間點則將落在2018年上半。反觀英特爾(Intel),其10納米制程量產時間確定將延后到2017下半年。但英特爾高層強調,7納米制程才是決勝關鍵,因為7納米的制程技術與材料將會有重大改變。

比較雙方未來的制程藍圖時間表,臺積電幾乎確認將于10納米制程節點時超越英特爾。但英特爾財務長Stacy?Smith在2016年Morgan?Stanley技術會議上強調,7納米制程才是彼此決勝的關鍵點,并強調7納米的制程技術與材料與過去相比,將會有重大突破。?

過去,在90納米制程開發時,就有不少聲音傳出半導體制程發展將碰觸到物理極限,難以繼續發展下去,如今也已順利地走到10納米,更甚至到7或是5納米制程節點,以過去的我們而言的確是難以想像。?

英特爾在技術會議上的這一番談話,引起我們對未來科技無限想像的空間,到底英特爾將會引進什么樣的革新技術?以及未來在制程發展上可能會遭遇到什么樣的挑戰?本文將會試著從半導體制程的前段(元件部分)、后段(金屬導線)以及市場規模等因素來探討先進制程未來可能面臨的挑戰,以及對應的解決辦法。

閘極設計走向全包覆結構?

半導體前段制程的挑戰,不外乎是不斷微縮閘極線寬,在固定的單位面積之下增加晶體管數目。不過,隨著閘極線寬縮小,氧化層厚度跟著縮減,導致絕緣效果降低,使得漏電流成為令業界困擾不已的副作用。半導體制造業者在28納米制程節點導入的高介電常數金屬閘極(High-k?Metal?Gate,HKMG),即是利用高介電常數材料來增加電容值,以達到降低漏電流的目的。其關系函式如下:

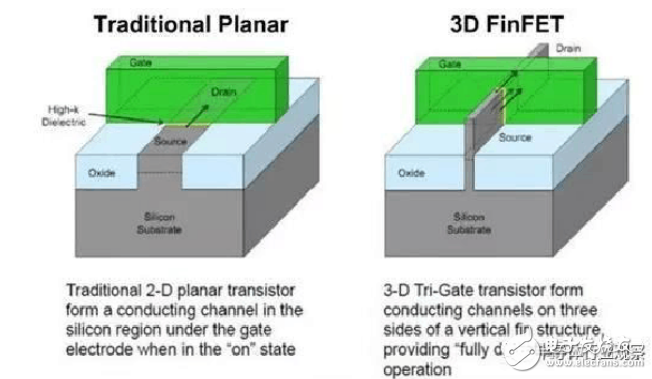

根據這樣的理論,增加絕緣層的表面積亦是一種改善漏電流現象的方法。鰭式場效晶體管(Fin?Field?Effect?Transistor,FinFET)即是藉由增加絕緣層的表面積來增加電容值,降低漏電流以達到降低功耗的目的,如圖1所示。

圖1傳統平面式(左)與鰭式場效晶體管(右)圖片來源:IDF,Intel?Development?Forum(2011)?

鰭式場效晶體管為三面控制,在5或是3納米制程中,為了再增加絕緣層面積,全包復式閘極(Gate?All?Around,GAA)將亦是發展的選項之一。但結構體越復雜,將會增加蝕刻、化學機械研磨與原子層沉積等制程的難度,缺陷檢測(Defect?Inspection)亦會面臨到挑戰,能否符合量產的條件與利益將會是未來發展的目標。

圖2未來晶體管科技發展藍圖與挑戰圖片來源:Applied?Materials(2013)?

III-V族、硅鍺材料呼聲高然物理挑戰艱鉅?

改變信道材料亦是增加IC運算性能與降低功耗的選項之一,晶體管的工作原理為在閘極施予一固定電壓,使信道形成,電流即可通過。在數位電路中,藉由電流通過與否,便可代表邏輯的1或0。?

過去信道的材料主要為硅,然而硅的電子遷移率(Electron?Mobility)已不符需求,為了進一步提升運算速度,尋找新的信道材料已刻不容緩。一般認為,從10納米以后,III-V族或是硅鍺(SiGe)等高電子(電洞)遷移率的材料將開始陸續登上先進制程的舞臺。

圖2清楚指出10納米與7納米將會使用SiGe作為信道材料。鍺的電子遷移率為硅的2~4倍,電洞遷移率(Hole?Mobility)則為6倍,這是鍺受到青睞的主要原因,IBM(現已并入Global?Foundries)在硅鍺制程上的著墨與研究甚多。?

III-V族的電子遷移率則更勝鍺一籌,約為硅的10~30倍,但美中不足的是III-V族的電洞遷移率相當的低。從圖2可看出,n型信道將會選擇III-V族作為使用材料,并結合鍺作為p型信道,以提高運算速度。?

但要將SiGe或是III-V族應用在現行的CMOS制程仍有相當多的挑戰,例如非硅信道材料要如何在不同的熱膨脹系數、晶格常數與晶型等情況下,完美地在大面積硅基板上均勻植入,即是一個不小的挑戰。此外,III-V族與鍺材料的能隙(Bandgap)較窄,于較高電場時容易有穿隧效應出現,在越小型元件的閘極中,更容易有漏電流的產生,亦是另一個待解的課題。

后段制程面臨微影、材料雙重挑戰?

0.13微米之前是使用鋁作為導線的材料,但IBM在此技術節點時,導入了劃時代的銅制程技術,金屬導線的電阻率因此大大地下降(表1),信號傳輸的速度與功耗將因此有長足的進步。?

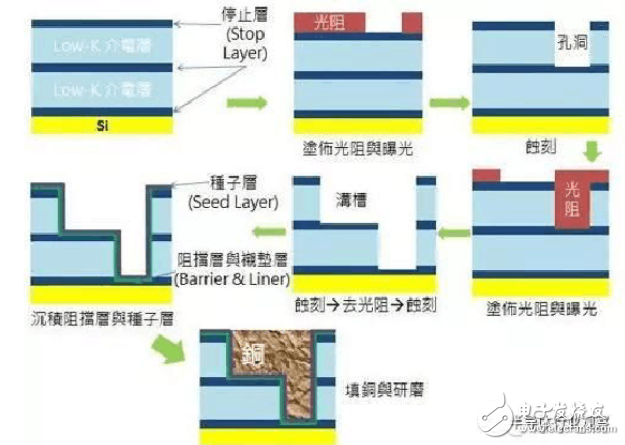

為何不在一開始就選擇銅作為導線的材料?原因是銅離子的擴散系數高,容易鑽入介電或是硅材料中,導致IC的電性飄移以及制程腔體遭到污染,難以控制。IBM研發出雙鑲崁法(Dual?Damascene),先蝕刻出金屬導線所需之溝槽與洞(Trench?&?Via),并沉積一層薄的阻擋層(Barrier)與襯墊層(Liner),之后再將銅回填,防止銅離子擴散。與過去的直接對鋁金屬進行蝕刻是完全相反的流程。雙鑲崁法如圖3所示。

雙鑲崁法制程示意圖?

隨著線寬的微縮,對于黃光微影與蝕刻的挑戰當然不在話下,曝光顯影的線寬一致性(Uniformity),光阻材料(Photo?Resist,PR)的選擇,都將會影響到后續蝕刻的結果。蝕刻后導線的線邊緣粗糙度(Line?Edge?Roughness,LER),與導線蝕刻的臨界尺寸(Critical?Dimension,CD)與其整片晶圓一致性等最基本的要求,都是不小的挑戰。?

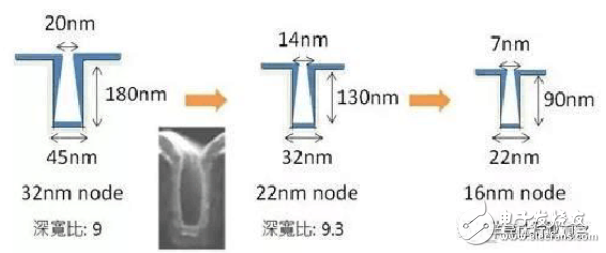

后段制程另外一個主要的挑戰則是前文所提到銅離子擴散。目前阻擋層的主要材料是氮化鉭(TaN),并在阻擋層之上再沉積襯墊層,作為銅與阻擋層之間的黏著層(Adhesion?Layer),一般來說是使用鉭(Ta)。然而,鉭沉積的覆蓋均勻性不佳,容易造成導線溝槽的堵塞,20納米節點以前因導線的深寬比(Aspect?Ratio,AR)較低而尚可接受,但隨著制程的演進,導線線寬縮小導致深寬比越來越高,鉭沉積的不均勻所造成的縮口將會被嚴重突顯出來,后端導致銅電鍍出現困難,容易產生孔洞(Void)現象,在可靠度測試(Reliability?Test)時容易失敗。另外,鉭的不均勻性容易造成溝槽填充材料大部份是鉭而不是銅,由于鉭金屬導線的阻值將會大幅上升,抵銷原先銅導線所帶來的好處,其示意如圖4所示。

圖4?金屬導線制程發展藍圖?

前文提到襯墊層必需具有低電阻率、良好的覆蓋均勻性、是銅的良好黏著層等重要特性,鉭在20納米節點以下已無法符合制程的需求,找出新的材料已經刻不容緩。鈷(Cobalt,Co)與釕(Ruthenium,Ru)是目前最被看好的候選材料。鈷是相當不錯的襯墊層,具有比鉭更低的電阻率,對銅而言是亦是不錯的黏著層,且在電鍍銅時具有連續性,不容易造成孔洞現象出現。但鈷襯墊層也有其不理想之處,主要是因為銅的腐蝕電位高于鈷,因此在銅、鈷的接觸面上,容易造成鈷的腐蝕,此現象稱為電流腐蝕(Galvanic?Corrosion),亦稱為伽凡尼腐蝕。解決電流腐蝕的問題必須從化學機械研磨(Chemical?Mechanical?Polish,CMP)的與后清洗(Post?CMP?Clean)著手,使用特殊的化學原料改變銅與鈷之間的腐蝕電位,以降低或消除腐蝕現象。目前預估鈷襯墊層將可延伸到10納米制程節點。接著在7納米,阻擋層與襯墊層的候選材料將有可能是釕,銅可以直接在釕上電鍍,并有效阻擋銅離子對介電層的擴散,如圖5所示。

然而,釕和鈷在暴露于銅時具有相同的電流腐蝕問題。只有釕恰好是鈷的反面。釕的腐蝕電位高于銅的腐蝕電位,因此銅金屬會受到腐蝕。釕的硬度較高,化學性能穩定。與其它化學成分反應不容易。只有強氧化劑如高碘酸鉀(KIO4),它被用作氧化劑,可以用來氧化它以提高研磨速率(約100 150 A/min)。釕的物理化學性質對化學機械拋光工藝提出了巨大的挑戰。目前,該行業仍在尋找合適的解決方案。它

需求的規模是不夠的。先進的工藝正面臨著經濟因素的考驗。

TVL是全球晶圓生產的領導者。其發展趨勢對半導體工業的發展有著重要的影響。每季財務刊物的聲明是半導體工業發展的風向。因此,對其收入趨勢的分析可以用來窺探和預測未來全球IC產業的發展。指向季度營收趨勢。

過去智慧型手機與平板電腦帶動半導體先進制程的發展與高成長,但現在行動通信裝置的熱潮已明顯消退,IC產業鏈相關廠商亦希望找出下一個殺手級應用,繼續帶動半導體產業發展。?

目前業界一致認為,物聯網(Internet?of?Things,IoT)為最佳候選人之一。物聯網主要構架是將會使用大量微控制器(Micro?Controller?Unit,MCU)與微機電感測器(MEMS?Sensor),以及微型Wi-Fi芯片作為數十億計的「物」的控制與連接元件,這些「物」的信號將會傳送到背后數以千萬計,具有高運算能力的服務器進行大數據(Big?Data)分析,以提供使用者及時且有用的信息。?

由此可知,與「物」相關的芯片數量應該會相當驚人,但其所需的半導體制程技術應是成熟型甚至是28納米制程即可應付;而最需要先進制程技術的服務器中央處理器芯片,相較于「物」的數量應會低上不少,對相關IC制造廠商的貢獻營收是否仍可繼續支撐制程開發與設備的投資,仍是未知數。市場給予IC制造廠商的壓力與挑戰,并不亞于前文所提到的制程挑戰。

技術挑戰時時存在產業生態轉變才是真考驗?

隨著制程技術的演進,遇到的挑戰與困難只會多不會少,并且制程節點已進入到10納米以下,快要接觸到物理極限,所以除了線寬微縮外,改變元件結構或是使用新的材料等選項,已是一條不可不走的路。?

像前段制程的元件部份,除了線寬微縮的挑戰之外,其他如功耗的將低或是運算能力的增進,亦是等待解決的課題之一。FinFET將過去的平面式結構轉為立體式結構,增加對閘極的控制能力,未來更有可能轉為全包復式的閘極以降低漏電流。?

另外,改變信道材料,由過去的硅改為SiGe或是III-V族等信道材料,為的都是增加電子或是電洞的遷移率。但晶圓制造業者要如何把異質材料整合至硅基板上,又兼顧可靠度,將是避無可避的挑戰。

氮化鉭已漸漸地不符合制程的要求。鈷已在20納米制程部份取代了鉭,作為襯墊層的主要材料,未來釕更會在7納米制程繼續接棒。但因鈷、釕與銅電化學與材料的特性,增加了化學機械研磨與后清洗的挑戰。?

回顧過去的歷史,技術上的難關總有辦法克服,但接下來半導體產業還要面臨經濟上的考驗。未來的制程節點發展難度將會越來越高,相對的,制程開發與設備的投資金額也將會越來越龐大,最終必定將會反應到晶圓的銷售價格上。?

上一波行動裝置如智慧型手機與平板裝置的熱賣,帶起了28納米制程營收的高峰,但未來先進制程可能不會有類似的機遇。在行動通信裝置的退燒,以及物聯網應用的普及帶動下,成熟型制程如微機電與28納米將仍可持續發光發熱,但高成本的先進制程未來在市場的接受度上,仍有不少的質疑聲浪與挑戰,未來的發展有待持續觀察。

哪些處理器用到了7nm 工藝?

因為智能手機處理器的線寬越來越小,就意味著處理器性能越來越強大,耗電越來越低,但是芯片制造成本卻也因此而節節攀升。根據外國媒體報導,就是因為受到成本因素限制,2018 年可能只有三星電子和蘋果兩家采用 7 納米工藝的處理器,其他處理器制造商可能繼續沿用成本比較低的現有工藝技術。

根據國外媒體報導指出,芯片中的線寬越小,就可以在單位面積的芯片上整合更多的晶體管,也使得系統芯片可以整合更多芯片,讓功能更加強大。不過,之前所公布的高通驍龍 845 處理器,就有消息指出,高通已經決定該產品將不會采用新一代的 7 納米工藝制造,而將繼續使用三星半導體的 10 納米工藝生產。至于,全球第 2 大手機芯片廠商聯發科,也決定在其 Helio P 處理器中,采用臺積電的 12 或 16 納米工藝,生產時間將是 2018 年上半年。

非常好我支持^.^

(0) 0%

不好我反對

(2) 100%

相關閱讀:

- [處理器/DSP] Codasip發布適用于定制計算的新一代RISC-V處理器系列產品 2023-10-24

- [電子說] Andes旗下高性能多核矢量處理器IP的AX45MPV正式上市 2023-10-24

- [電子說] 首批高通驍龍8 Gen3旗艦入網 2023-10-24

- [控制/MCU] 單片機的三大功能 2023-10-24

- [電子說] 思爾芯原型驗證助力香山RISC-V處理器迭代加速 2023-10-24

- [電子說] STM32基礎知識:中斷系統 2023-10-24

- [電子說] 講一講Apple Macintosh處理器過渡的故事 2023-10-24

- [電子說] GD32的中斷-外部中斷的實現 2023-10-24

( 發表人:金巧 )