半導體C-V測量基礎

通用測試

電容-電壓(C-V)測試廣泛用于測量半導體參數,尤其是MOSCAP和MOSFET結構。此外,利用C-V測量還可以對其他類型的半導體器件和工藝進行特征分析,包括雙極結型晶體管(BJT)、JFET、III-V族化合物器件、光伏電池、MEMS器件、有機TFT顯示器、光電二極管、碳納米管(CNT)和多種其他半導體器件。

這類測量的基本特征非常適用于各種應用和培訓。大學的研究實驗室和半導體廠商利用這類測量評測新材料、新工藝、新器件和新電路。C-V測量對于產品和良率增強工程師也是極其重要的,他們負責提高工藝和器件的性能。可靠性工程師利用這類測量評估材料供貨,監測工藝參數,分析失效機制。

采用一定的方法、儀器和軟件,可以得到多種半導體器件和材料的參數。從評測外延生長的多晶開始,這些信息在整個生產鏈中都會用到,包括諸如平均摻雜濃度、摻雜分布和載流子壽命等參數。在圓片工藝中,C-V測量可用于分析柵氧厚度、柵氧電荷、游離子(雜質)和界面阱密度。在后續的工藝步驟中也會用到這類測量,例如光刻、刻蝕、清洗、電介質和多晶硅沉積、金屬化等。當在圓片上完全制造出器件之后,在可靠性和基本器件測試過程中可以利用C-V測量對閾值電壓和其他一些參數進行特征分析,對器件性能進行建模。

半導體電容的物理特性

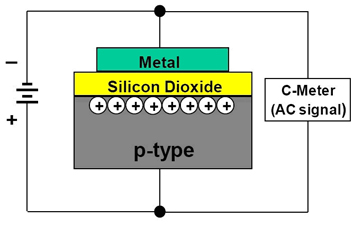

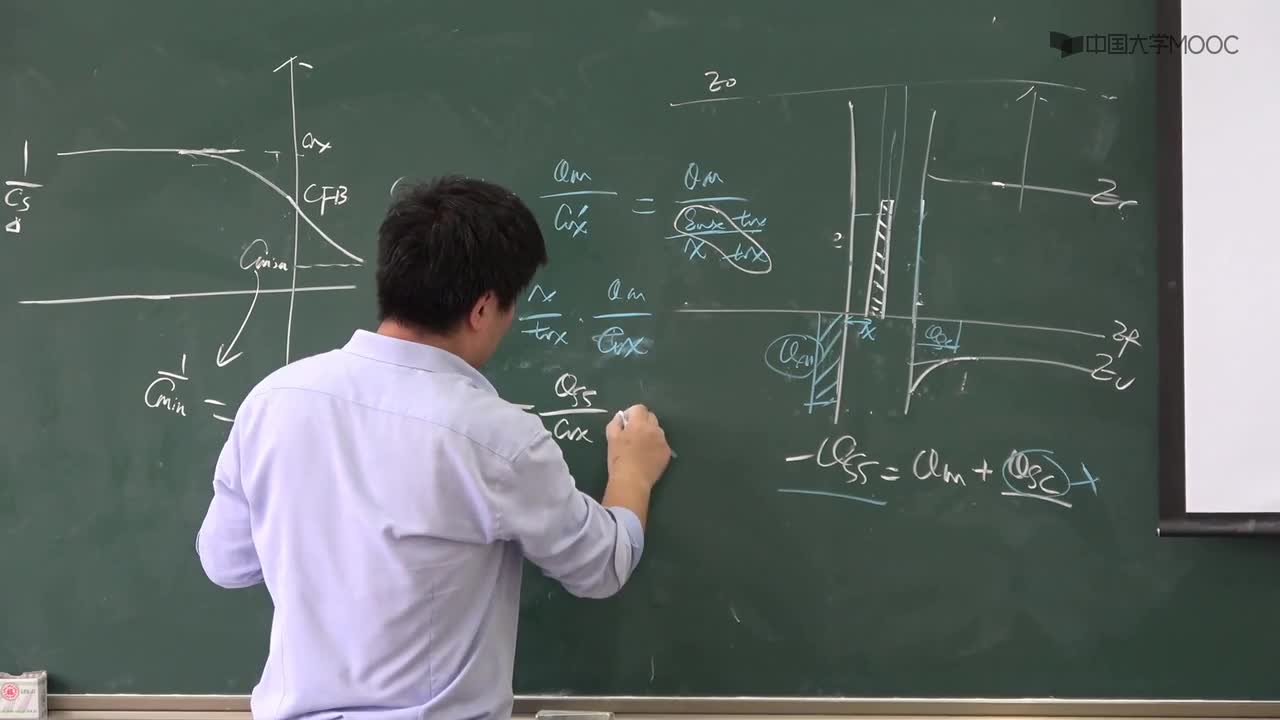

MOSCAP結構是在半導體制造過程中形成的一種基本器件結構(如圖1所示)。盡管這類器件可以用于真實電路中,但是人們通常將其作為一種測試結構集成在制造工藝中。由于這種結構比較簡單而且制造過程容易控制,因此它們是評測底層工藝的一種方便的方法。 ?????????????????????????????????????????????????????????????????????

?????????????????????????????????????????????????????????????????????

圖中文字:金屬,二氧化硅,電容計(交流信號),P型

圖1. P型襯底上形成的MOSCAP結構的C-V測量電路

圖1中的金屬/多晶層是電容的一極,二氧化硅是絕緣層。由于絕緣層下面的襯底是一種半導體材料,因此它本身并不是電容的另一極。實際上,其中的多數載流子是電容的另一極。物理上而言,電容C可以通過下列公式中的變量計算出來:

C = A (κ/d), 其中

A是電容的面積,

κ是絕緣體的介電常數

d是兩極的間距

因此,A 和 κ越大,絕緣體厚度越薄,電容值就越高。通常而言,半導體電容的大小范圍從幾納法到幾皮法,甚至更小。

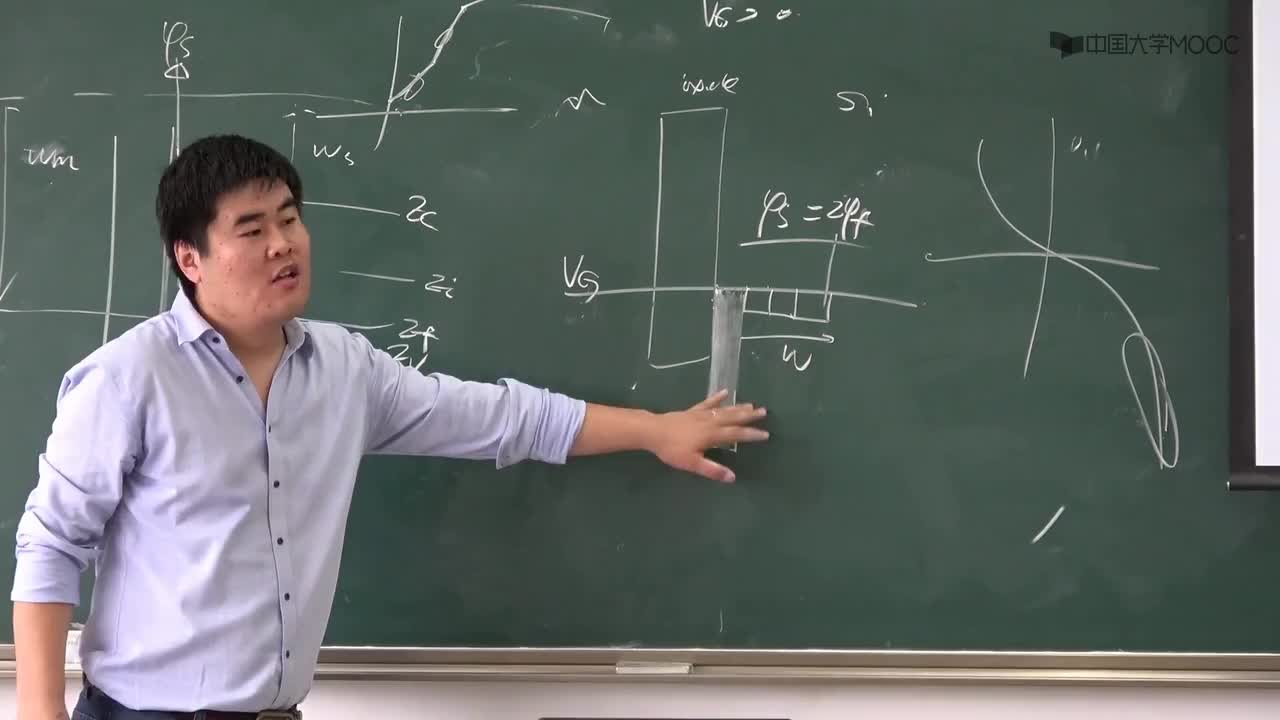

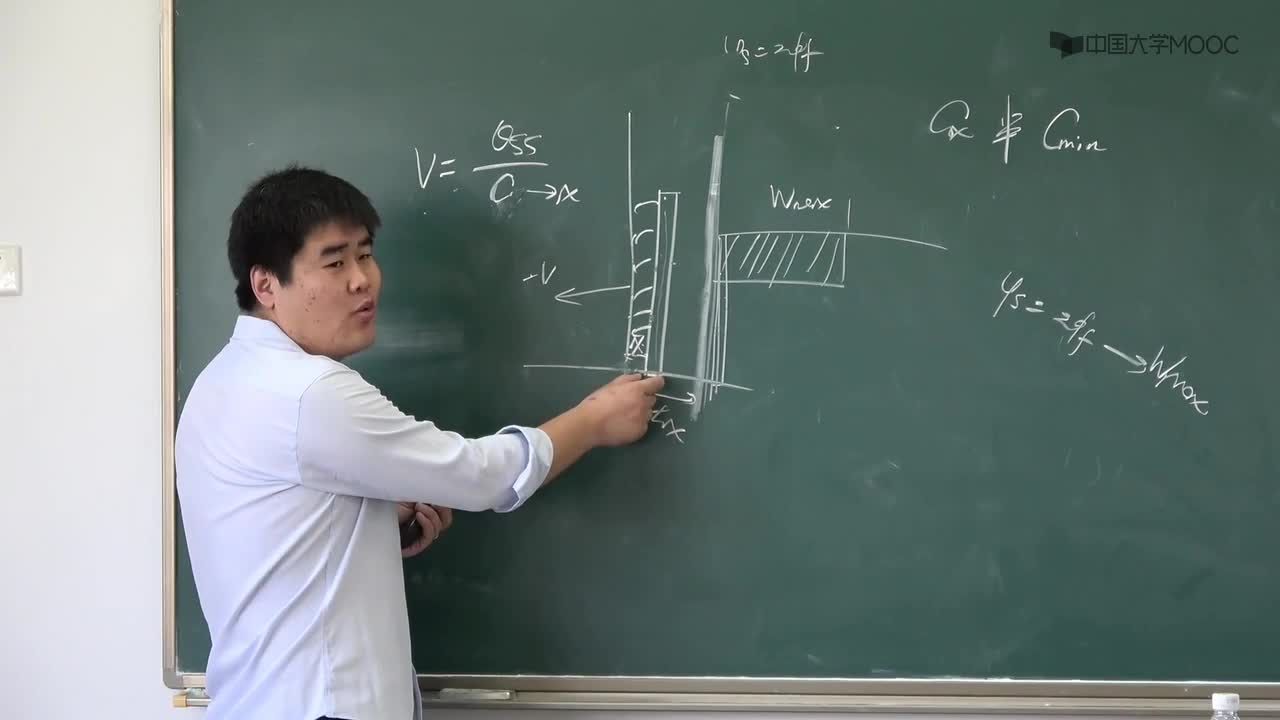

進行C-V測量時要在電容的兩極加載直流偏壓同時利用一個交流信號進行測量(如圖1所示)。通常情況下,這類測量使用的交流頻率范圍從10kHz到10MHz。所加載的偏壓作為直流電壓掃描驅動MOSCAP結構從累積區進入耗盡區,然后進入反型區(如圖2所示)。

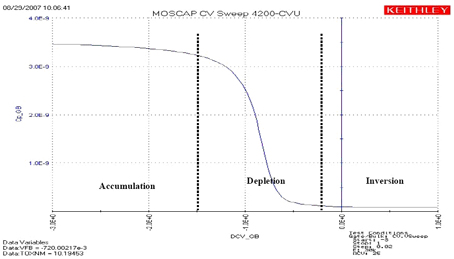

圖2. C-V測試中獲得的MOSCAP結構的直流偏壓掃描

強大的直流偏壓導致襯底中的多數載流子在絕緣層界面附近累積。由于它們無法穿透絕緣層,因此當電荷積累在界面附近(即d為最小值)時電容在累積區達到最大值。如圖1所示。從C-V累積測量可以得到的一個基本參數就是二氧化硅的厚度tox。

當偏壓降低時,多數載流子從氧化層界面被排斥開,耗盡區形成。當偏壓反相時,電荷載流子遠離氧化層達到最大距離,電容達到最小值(即d為最大值)。根據這時的反型區電容,可以推算出多數載流子的數量。這一基本原理同樣適用于MOSFET晶體管,只是它們的物理結構和摻雜更加復雜。

在偏壓掃過這三個區的過程中還可以得到多種其他參數,如圖2所示。利用不同的交流信號頻率可以得到其他細節信息。低頻可以揭示所謂的準靜態特征,而高頻測試則可以表現出動態性能。這兩類C-V測試通常都是需要的。

基本測試配置

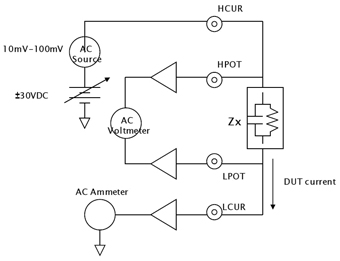

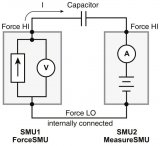

圖3給出了基本C-V測量配置的框圖。由于C-V測量實際上是在交流頻率下進行的,因此待測器件(DUT)的電容可以根據下列公式計算得到:

CDUT = IDUT / 2πfVac,其中

IDUT是流過DUT的交流電流幅值,

f是測試頻率,

Vac是測得的交流電壓的幅值和相角。

換而言之,這種測試通過加載交流電壓然后測量產生的交流電流、交流電壓和它們之間的阻抗相角,最終測出DUT的交流阻抗。

圖中文字:交流源,交流伏特計,DUT電流,交流安培計

圖3. C-V測量的基本測試配置

這些測量考慮了與電容相關的串聯與并聯電阻,以及耗散因子(漏流)。

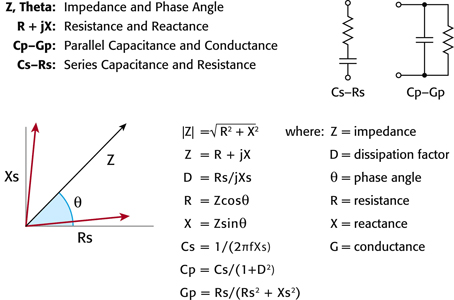

圖4給出了這類測量可以測出的主要電路變量。

z, theta:阻抗與相角

R+jX:電阻與電抗

Cp-Gp:并聯電容與電導

Cs-Rs:串聯電容與電阻

其中:Z=阻抗

D=耗散因子

θ=相角

R=電阻

X=電抗

G=電導

圖4. C-V測量得到的主要電氣變量

成功C-V測量的挑戰

C-V測試配置的框圖雖然看上去非常簡單,但是這種測試卻具有一定的挑戰。一般而言,測試人員在下面幾個方面會遇到麻煩:

* 低電容測量(皮法和更小的值)

* C-V測試儀器與圓片器件的連接

* 漏電容(高D)的測量

* 利用硬件和軟件采集數據

* 參數提取

克服這些挑戰需要仔細注意所用的技術以及合適的硬件和軟件。

低電容測量。 如果C較小,那么DUT的交流響應電流就較低,難以測量。但是,在較高的頻率下,DUT阻抗將減小,從而電流會增大,比較容易測量。半導體電容通常非常低(低于1pF),低于很多LCR表的測量范圍。即使那些聲稱能夠測量這些小電容值的測試儀可能也會由于說明書晦澀難懂而很難判斷最終的測量精度。如果無法明確給出測試儀整個量程的精度,那么用戶需要因此而咨詢制造商。

高D(漏)電容。半導體電容除了C值較低之外,還具有泄漏的特點。當與電容并聯的等價電阻太低時就會出現這種情況。這會導致電阻性阻抗超過電容性阻抗,C值被噪聲所淹沒。對于具有超薄柵氧層的器件,D的值可能大于5。一般而言,隨著D的增大,電容測量的精度迅速下降,因此高D是實際使用電容計的一個限制因素。同樣,較高的頻率有助于解決這一問題。在較高的頻率下,電容性阻抗較低,使得電容電流較高,更容易進行測量。

C-V測量的互連。大多數測試環境下,DUT都是圓片上的一個測試結構:它通過探測器、探針卡適配器和開關矩陣連接C-V測試儀。即使沒有開關,仍然也會使用探測器和大量的連線。在較高的頻率下,必須采用特殊的校正和補償技術。通常情況下,這是通過組合使用開路、短路或者校準器件來實現的。由于硬件、布線和補償技術非常復雜,因此經常與C-V測試應用工程師進行交流是一個好的辦法。他們擅長使用各種探測系統,克服各種互連問題。

獲取有用的數據。除了上述的精度問題,C-V數據采集中實際需要考慮的因素包括測試變量的儀器量程,參數提取軟件的多功能性和硬件的易用性。一般而言,C-V測試已僅限于約30V和10mA直流偏壓。但是,很多應用,例如LD MOS結構的特征分析、低k夾層電介質、MEMS器件、有機TFT顯示器和光電二極管,需要在較高的電壓或電流下進行測試。對于這些應用,需要單獨的高壓直流電源和電容計;高達400V的差分直流偏壓(0到±400V)和高達300mA的電流輸出是非常有用的。在C-V測試儀的HI和LO端加載差分直流偏壓能夠更靈活地控制DUT內的電場,這對于新型器件的研究和建模是非常有用的,例如納米級元件。

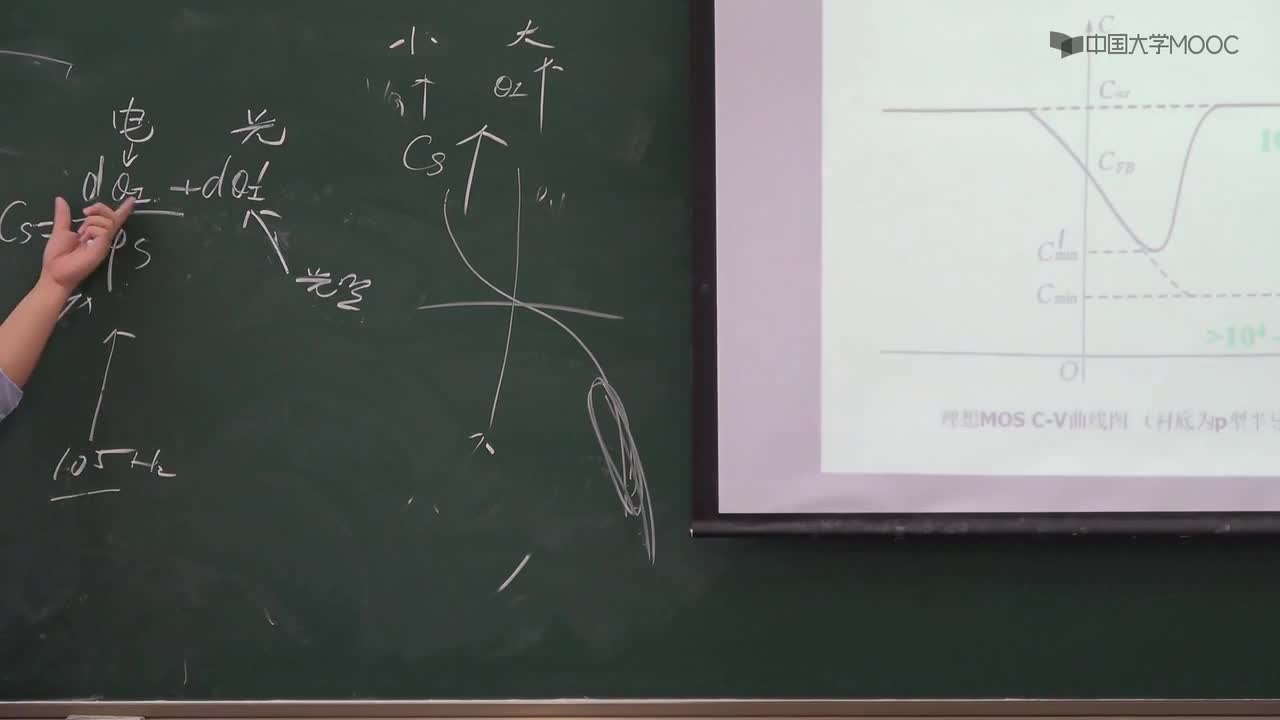

儀用軟件應該包括無需用戶編程可直接使用的測試例程。這些應該適用于大多數廣泛使用的器件工藝和測試技術,即本文前三段中提及的有關內容。有些研究者可能會對一些不常見的測試感興趣,例如對MIM(金屬-絕緣體-金屬)型電容進行C-V和C-f掃描,測量圓片上的互連小電容,或者對雙端納米器件進行C-V掃描。利用自動繪圖功能能夠方便的實現參數提取(例如,如圖5所示)。

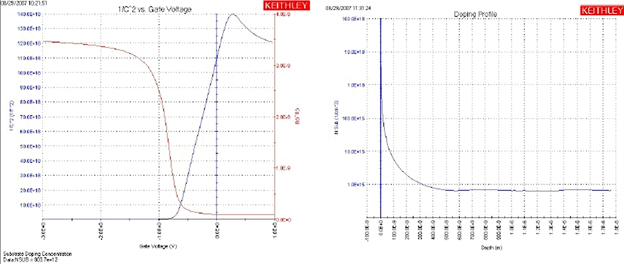

圖5. 利用吉時利4200-SCS進行參數提取的實例表現了半導體的摻雜特征(左邊的藍線),它與1/C2 與Vg的關系呈倒數關系(紅線)。右圖給出了摻雜分布,即每立方厘米的載流子數與襯底深度的函數關系。

通常,人們都希望工程技術人員和研究人員在幾乎沒有任何儀器使用經驗或培訓的情況下就能夠進行C-V測量。具有直觀用戶界面和簡單易用特征的測試系統使得這一點成為現實。其中包括簡單的測試配置、序列控制和數據分析。否則,用戶在掌握系統方面就要比采集和使用數據花費更多的時間。對測試系統其它考慮因素包括:

* 緊密集成的源-測量單元、數字示波器和C-V表

* 方便集成其他外部儀器

* 基于探針的高分辨率和高精度測量(直流偏壓低至毫伏級,電容測量低至飛法級)

* 測試配置和庫易于修改

* 提供檢測/故障診斷工具幫助用戶確定系統是否正常工作

電子發燒友App

電子發燒友App

評論