簡 介:這學(xué)期的信號與系統(tǒng)進(jìn)展到第五章,拉普拉斯變換與 z 變換。前幾天看到一篇博文中對于無限電阻網(wǎng)絡(luò)求解相鄰節(jié)點阻抗中使用了離散傅里葉變換 (DFT) 的方法比較新穎。分析了DFT在其中僅僅是起到

2022-08-16 16:26:17 1764

1764 當(dāng)SoC上有超過80%的芯片面積被各種形式的存儲器占用之時,存儲器的DFT測試已經(jīng)變得非常重要。

2023-12-09 09:56:55 1205

1205

DFT:全稱是 Design for Test,可測性設(shè)計,通過在芯片原始設(shè)計中插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節(jié)省芯片測試的成本

2021-07-23 07:28:32

雖然可測性設(shè)計(DFT)與內(nèi)置自檢(BIST)技術(shù)已在SoC(系統(tǒng)級芯片)設(shè)計中受到廣泛關(guān)注,但仍然只是被看作“后端”的事。實際上,這些技術(shù)在器件整個設(shè)計周期中都非常重要,可以保證產(chǎn)品測試錯誤覆蓋率

2011-12-15 09:53:14

DFT是什么?DFT在芯片設(shè)計領(lǐng)域的含義,即可測性設(shè)計(Design for Test), 可測試性設(shè)計(Design for Test,簡稱DFT)是電路和芯片設(shè)計的重要環(huán)節(jié),它通過在芯片原始

2012-01-11 14:33:22

DFT是什么?DFT在芯片設(shè)計領(lǐng)域的含義,即可測性設(shè)計(Design for Test), 可測試性設(shè)計(Design for Test,簡稱DFT)是電路和芯片設(shè)計的重要環(huán)節(jié),它通過在芯片原始

2012-01-11 14:28:06

量也大為減小.DFT與FFT相比還具有變換點數(shù)或采樣率選擇更靈活、實時性更好、更容易控制溢出和動態(tài)范圍、運(yùn)算編程簡單、可方便地在非DSP芯片中編程實現(xiàn)等優(yōu)點.因此在實際應(yīng)用中可以從具體條件出發(fā)來比較

2014-05-22 20:43:36

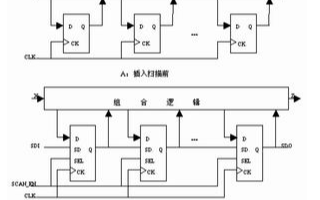

dft可測試性設(shè)計,前言可測試性設(shè)計方法之一:掃描設(shè)計方法可測試性設(shè)計方法之二:標(biāo)準(zhǔn)IEEE測試訪問方法可測試性設(shè)計方法之三:邏輯內(nèi)建自測試可測試性設(shè)計方法之四:通過MBIST測試寄存器總結(jié)...

2021-07-22 09:10:42

看教程一半測試程序采用生產(chǎn)者和消費(fèi)者架構(gòu),下面兩個圖(合成一張圖看)不是生產(chǎn)消費(fèi)結(jié)構(gòu),想請教一下下面程序架構(gòu)與生產(chǎn)消費(fèi)相比,有什么不足的地方,或有什么區(qū)別。比如會丟失數(shù)據(jù)嗎,顯示的數(shù)據(jù)量有不同嗎?

2016-09-26 20:59:39

AD7793,想請問一下INL的測試采用什么方法比較合理?

2023-12-01 07:30:13

ARM架構(gòu)核心板三種FormFactor之比較文 By易江春水國際上,在ARM核心板領(lǐng)域,最為常見的三種Form Factor 分別是SMARC,Qseven, Apalis, 分別有不同的廠家在

2014-09-28 10:35:31

實驗二 FFT與DFT計算時間的比較及圓周卷積代替線性卷積的有效性實驗:一 實驗?zāi)康?:掌握FFT基2時間(或基2頻率)抽選法,理解其提高減少乘法運(yùn)算次數(shù)提高運(yùn)算速度的原理。2:掌握FFT圓周卷積

2011-12-29 21:52:49

,是團(tuán)隊的測試流程,還是硬件在環(huán)仿真技術(shù)本身?......“HIL測試方法”一詞太過宏大,為敘述方便,本文特指“為了驗證ECU軟硬件的設(shè)計和實現(xiàn),基于硬件在環(huán)設(shè)備,如何設(shè)計測試流程、提取測試需求、設(shè)計測試

2017-02-10 14:05:57

關(guān)于IC設(shè)計的流程是怎樣的?有關(guān)IC設(shè)計的方法有哪些?

2021-06-21 07:51:54

The following is the Job Description of this position-- DFT Engineer. If someone is interested, plz feel

2016-07-15 13:58:30

以看出整個工藝流程存在的問題,比如前期工序SMT、DIP等,存在問題,就進(jìn)行調(diào)整,讓整個工藝更加完善。PCBA測試常見方法,主要有以下幾種: 1.手工測試手工測試就是直接依靠視覺進(jìn)行測試,通過視覺與比較來

2016-11-08 17:19:06

licode服務(wù)架構(gòu)及流程是怎樣的?

2022-02-10 07:02:57

什么是數(shù)字信號處理DFT?貌似有很多DFT啊

2011-12-15 09:39:26

在開發(fā)中進(jìn)行測量,可用以評估是否達(dá)成目標(biāo)規(guī)范的性能,同時在測試制程中的產(chǎn)品時將面臨各種挑戰(zhàn),包括確認(rèn)使用的方法是否可提供較為確定的所需數(shù)值范圍、缺乏某項參數(shù)的追溯,以及確認(rèn)可作為交叉檢查的替代技術(shù)

2019-05-31 07:51:04

ATCA在測試領(lǐng)域有哪些應(yīng)用實例?基于ATCA的測試系統(tǒng)架構(gòu)是如何構(gòu)成的?

2021-05-11 07:01:49

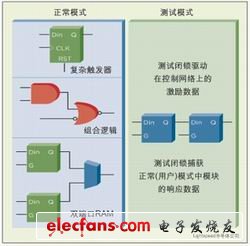

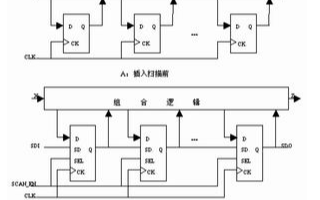

基于掃描的DFT方法掃描設(shè)計的基本原理是什么?掃描設(shè)計測試的實現(xiàn)過程是怎樣的?基于掃描的DFT對芯片測試的影響有哪些?

2021-05-06 09:56:36

嗨阿爾想知道在將基礎(chǔ)架構(gòu)交付給應(yīng)用程序團(tuán)隊之前如何測試基礎(chǔ)架構(gòu)?我基本上指的是 HAL 層、CMSIS 和所有帶外圍設(shè)備的 BSP 層。是否有用于這些功能的驗證測試的已知方法?謝謝!

2023-01-09 06:03:39

提高DFT設(shè)計測試覆蓋率的有效方法是什么

2021-05-07 06:37:41

攝像頭網(wǎng)口(RJ45)進(jìn)行浪涌測試的方法和流程是什么?施加的波形選擇1.2/50us或10/700us?還是組合波形?如何連接測試設(shè)備?

2019-08-29 11:47:31

看到一篇博文中對于無限電阻網(wǎng)絡(luò)求解相鄰節(jié)點阻抗中使用了離散傅里葉變換 (DFT) 的方法比較新穎。分析了DFT在其中僅僅是起到描述線性時不變離散時間系統(tǒng)的作用,所以將其替換成 z 變換進(jìn)行描述,則在分析求解過程中會更加的清晰。原作者:TsinghuaJoking

2022-08-19 15:59:46

自己制作的Matlab DFT習(xí)題

2020-10-31 21:13:21

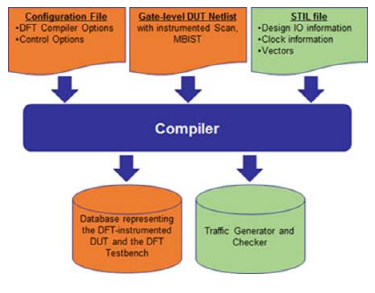

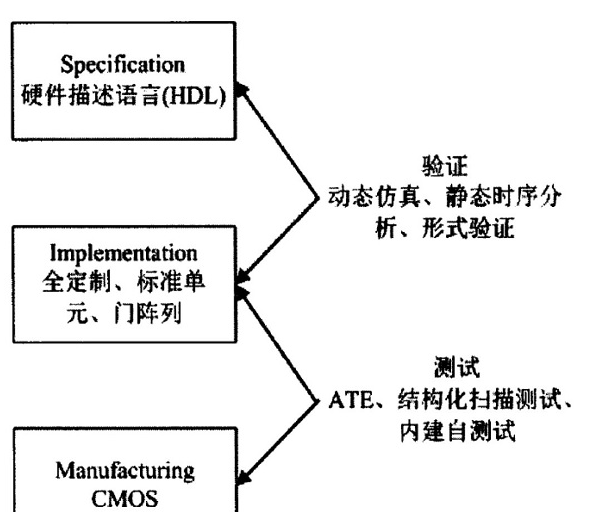

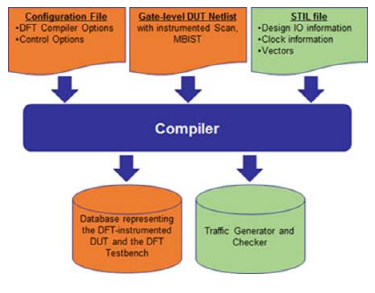

推薦的學(xué)習(xí)方法是:理解問題域;比較并掌握解決問題的不同方法;熟悉解決問題過程中遇到的各種難題;再通過運(yùn)用EDA工具解決實際問題來鞏固加深之前所學(xué)的知識。在了解DFT之前,先讓我們簡短回顧下整個數(shù)字芯片的設(shè)計流程

2016-05-25 15:32:58

DFT是什么原理?

2021-06-17 08:54:06

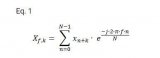

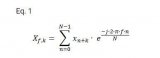

`其中的分辨率f△代進(jìn)去以后DFT表達(dá)式就變成了x[n]exp(-j2pi*n*k*fs/N),和DSP課本上的DFT公式不一樣啊,為什么和fs有關(guān)呢?`

2013-05-30 01:02:42

隨著電子電路集成度的提高,電路愈加復(fù)雜,要完成一個電路的測試所需要的人力和時間也變得非常巨大。為了節(jié)省測試時間,除了采用先進(jìn)的測試方法外,另外一個方法就是提高設(shè)計本身的可測試性。其中,可測試性包括

2011-12-15 09:32:30

在介紹嵌入式 SoC IC 概念的基礎(chǔ)上,介紹基于重用(re-use)的 SoC IC 設(shè)計方法和流程, 涉及滿足時序要求、版圖設(shè)計流程和測試設(shè)計的問題, 并給出設(shè)計計劃考慮項目。

2009-05-13 16:09:42 28

28 CTT與IRT測量原理之比較:通過對經(jīng)典測量理論與項目反應(yīng)理論在基本假設(shè)、測驗精度計量、測驗的標(biāo)準(zhǔn)誤以及測驗項目的篩選等四個主要領(lǐng)域的比較,可以發(fā)現(xiàn)項目反應(yīng)理論具有被試

2009-10-25 12:13:18 12

12 論述了一種測試混合信號集成電路襯底噪聲波形的方法采用電壓比較器利用襯底電壓對比

較器狀態(tài)的影響對噪聲作出統(tǒng)計測試根據(jù)測試結(jié)果重建噪聲波形設(shè)計了一

2010-08-29 16:08:46 14

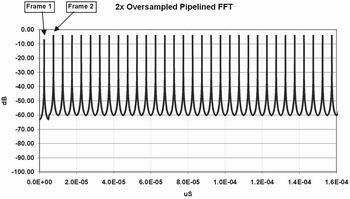

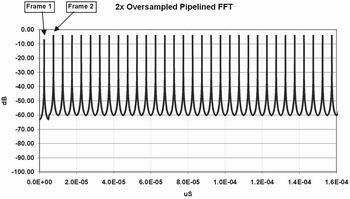

14 摘要:本文簡要地論述了FFT和多相位DFT濾波器組在響應(yīng)方面的差異。一般而言,多相位DFT(甚至包括任何濾波器組,比如PFT)在穩(wěn)態(tài)條件下有著很好的相鄰信道抑制性能,而瞬態(tài)響應(yīng)卻很糟糕。這符合了濾波器沖激響應(yīng)結(jié)論。

2006-03-11 13:17:03 2055

2055

MTD濾波器設(shè)計方法比較

早期MTD濾波器,直接采用DFT算法。該算法等效于一組窄帶濾波器組,具有數(shù)字硬件實現(xiàn)簡單的特點,由于MTD雷達(dá)中

2009-02-27 10:03:00 2348

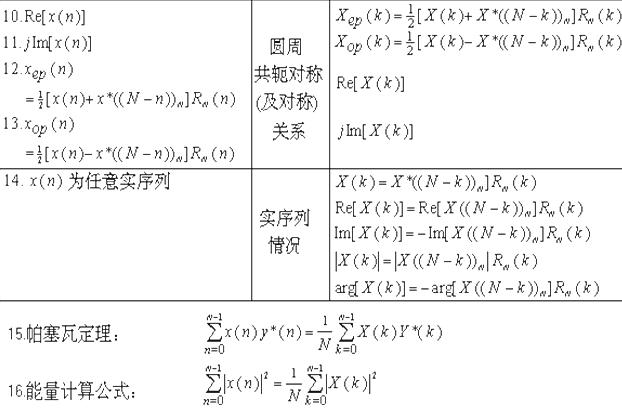

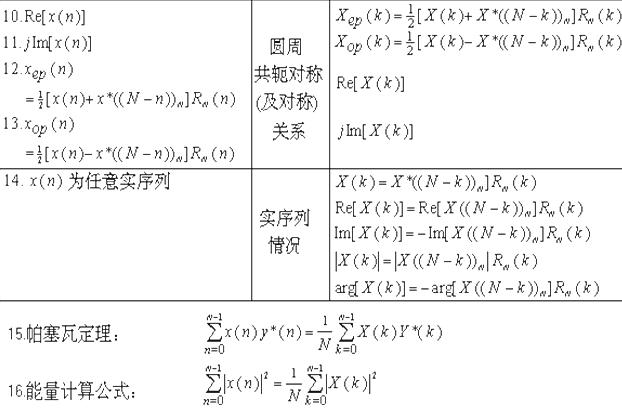

2348 DFT性質(zhì)一覽表

2009-07-25 11:41:03 3998

3998

視覺系統(tǒng)與視覺傳感器之比較

視覺傳感器迎來快速發(fā)展

在不久之前,設(shè)計質(zhì)量控制系統(tǒng)的工程師還不得不在若干種檢測選項中

2009-11-07 11:45:12 1833

1833 視覺傳感器與光電傳感器、人工檢驗之比較

光電傳感器與視覺傳感器之比較 與光電傳感器相比,視覺傳感器賦予機(jī)器設(shè)

2009-11-07 11:50:08 901

901 對講機(jī)的測試方法及流程

對講機(jī)在使用的過程中,其性能指標(biāo)有可能出現(xiàn)下降的情況,以至影響通信效果。因此,我們有必要掌握對

2010-02-07 11:16:14 6050

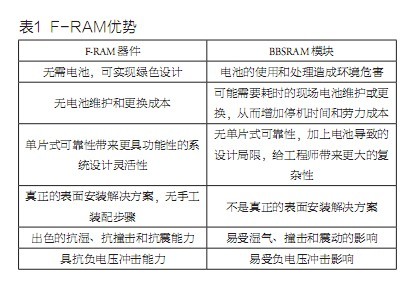

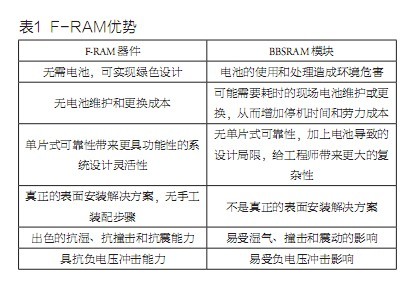

6050 F-RAM與BBSRAM功能和系統(tǒng)設(shè)計之比較

引言

高性能和環(huán)保是當(dāng)前技術(shù)創(chuàng)新的兩大要求。二者共同推動半導(dǎo)體元器件的發(fā)展,同時也為全球眾多企業(yè)和消費(fèi)者所

2010-03-03 16:29:43 1448

1448

HIL測試技術(shù)在汽車ECU開發(fā)流程中的應(yīng)用

1、V模式開發(fā)流程

V模式開發(fā)流程是現(xiàn)代最重要的開發(fā)方法,在這套開發(fā)流程中大量使用了計算機(jī)

2010-03-11 11:24:30 5437

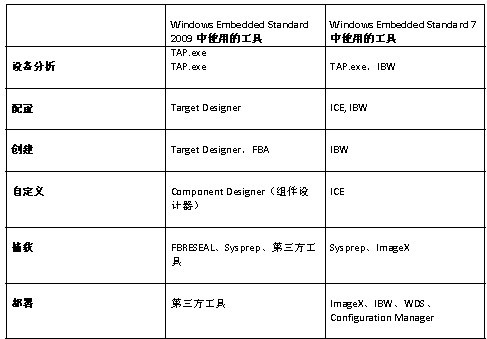

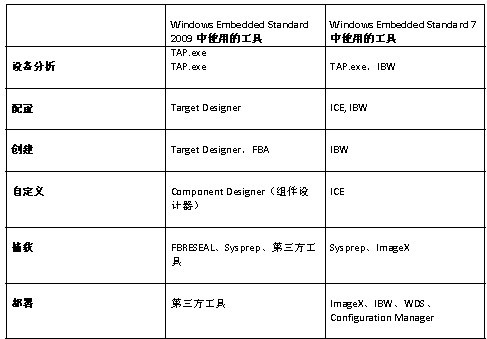

5437 WES7與WES2009嵌入式產(chǎn)品之比較

概述

本文介紹了Windows Embedded Standard 2009和Windows Embedded Standard 7在組件化、工具和映像構(gòu)建流程等方面的

2010-04-12 11:12:44 1823

1823

DFT:數(shù)字電路(fpga/asic)設(shè)計入門之可測試設(shè)計與可測性分析,離散傅里葉變換,(DFT)Direct Fouriet Transformer

可測試性技術(shù)(Design For Testability-

2010-06-07 11:00:48 29875

29875 DFT在數(shù)字信號處理中有很重要的作用,如頻譜分析、FIR DF的實現(xiàn)、線性卷積等。一個重要的原因是DFT有高效算法。 為了了解高效算法的重要以及實現(xiàn)高效算法的思路,先介紹DFT的運(yùn)算特

2011-09-07 23:59:55 57

57 首先給大家提供DFT和FFT的運(yùn)算量的教程,內(nèi)容有直接用DFT計算運(yùn)算量與用FFT計算的運(yùn)算量比較和多種DFT算法(時間抽取算法DIT算法,頻率抽取算法DIF算法等.

2011-09-08 00:01:48 71

71 基于滑動DFT算法推導(dǎo)出一種改進(jìn)的周期圖功率譜估計方法,并在軟件系統(tǒng)界面中應(yīng)用。根據(jù)傳統(tǒng)的功率譜估計方法和滑動DFT算法推導(dǎo)出改進(jìn)的功率譜估計算法,通過滑動DFT算法計算出

2011-09-09 11:02:32 0

0 為了提高大規(guī)模集成電路可測性設(shè)計(Design For Test,DFT)的故障覆蓋率,減少測試時間,通過分析自我測試(Self-Testing Using MISR and Parallel SRSG,STUMPS)方法中的測試機(jī)制,找出了其測試效果不

2011-10-28 17:18:20 61

61 本文進(jìn)行IP網(wǎng)絡(luò)監(jiān)控與傳統(tǒng)監(jiān)控之比較

2011-11-08 17:35:42 40

40 現(xiàn)今流行的可測試性設(shè)計(DFT:Design For Testability)為保證芯片的良品率擔(dān)任著越來越重要的角色。

2012-04-20 09:39:05 6249

6249

本內(nèi)容介紹了DFT可測試性設(shè)計的相關(guān)知識,并列舉了3中常見的可測性技術(shù)供大家學(xué)習(xí)

2012-05-30 16:42:27 7082

7082 DVR測試流程

2017-01-04 13:52:40 0

0 第3章--離散傅里葉變換(DFT)

2016-12-28 14:23:30 0

0 基于三層架構(gòu)的流程模擬系統(tǒng)的設(shè)計與應(yīng)用_劉紅霞

2017-01-19 21:54:24 0

0 基于電壓比較器襯底噪聲的測試方法

2017-01-22 13:38:08 5

5 DFT 是一種在設(shè)計階段將可測試性置入集成電路 (IC) 的方法,可以降低測試成本并提高制造良率,多年來以不同方式得到廣泛應(yīng)用。Ad-hoc 和結(jié)構(gòu)化這兩種方法能夠有效地檢測出電路中所有的故障,減少

2017-12-10 11:51:58 1

1 Ad-hoc DFT 包括一套提倡“良好”設(shè)計規(guī)范的規(guī)則,旨在簡化和加速測試流程。例如,提供置位和復(fù)位信號,使得所有觸發(fā)器均可初始化;避免引起振蕩的異步邏輯反饋;邏輯門設(shè)計應(yīng)注意避免扇入數(shù)過大(扇入

2018-04-12 14:29:00 2689

2689

對于許多現(xiàn)有的和未來的集成芯片器件來說,一項主要挑戰(zhàn)就是如何為龐大數(shù)量的設(shè)計創(chuàng)建測試圖案。對于有百萬門甚至數(shù)億門的設(shè)計,傳統(tǒng)上等到設(shè)計完成再創(chuàng)建測試圖案的方法是不切實際的,產(chǎn)生所有這些圖案需要龐大

2018-01-31 07:06:09 10838

10838

覺。使用滑動DFT的基本前提是很長一段時域數(shù)據(jù)流在一個長度為N的比較短的轉(zhuǎn)換窗口里。以一幅頻譜圖為例,頻譜圖是對很長一段或連續(xù)的時域采樣數(shù)據(jù)流按照一定的間隔實施到長度為N的窗口的頻域轉(zhuǎn)換。

2018-02-19 01:01:00 9726

9726

本文主要介紹了PICmicro中檔單片機(jī)系列之比較器模塊。

2018-06-25 04:20:00 0

0 SAR和Δ-Σ架構(gòu)的比較

2018-08-16 02:10:00 3796

3796 通過此視頻可快速瀏覽 PADS DFT 審核的一些主要功能、優(yōu)點和易用性。在設(shè)計流程的早期使用 PADS DFT 審核可大幅降低 PCB 的批量投產(chǎn)時間,確保 100% 的測試點覆蓋和制造前所有網(wǎng)絡(luò)的可測試性。

2019-05-21 08:06:00 2927

2927 PADS 可測試性設(shè)計 (DFT) 審核可以縮短上市時間。了解如何盡早在設(shè)計流程中利用 PCB 測試點和 DFT 審核優(yōu)化設(shè)計。

2019-05-14 06:26:00 3018

3018

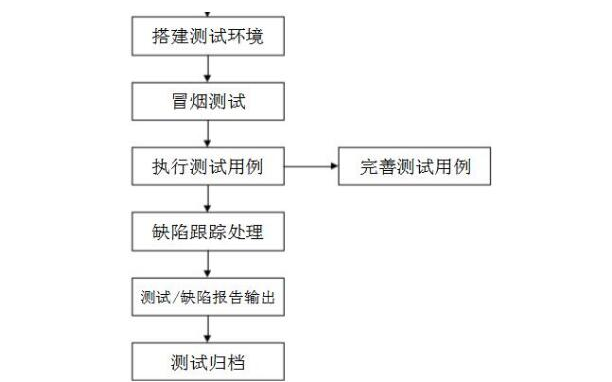

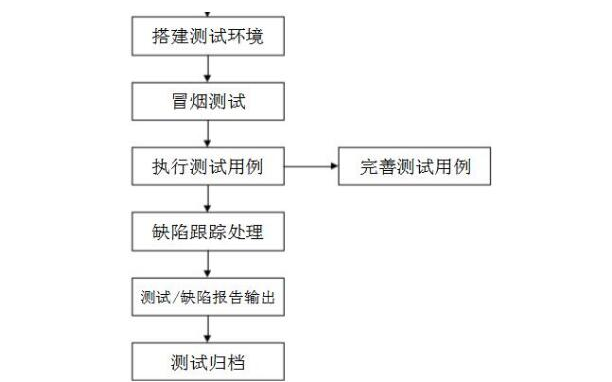

PCBA測試一般根據(jù)客戶的測試方案制定具體的測試流程,基本的PCBA測試流程如下:程序燒錄→ICT測試→FCT測試→老化測試。

2019-05-23 17:00:33 17183

17183 應(yīng)用離散傅里葉變換(DFT),分析離散信號x[k]的頻譜。深刻理解DFT分析離散信號頻譜的原理,掌握改善分析過程中產(chǎn)生的誤差的方法。

2019-08-06 17:16:55 11

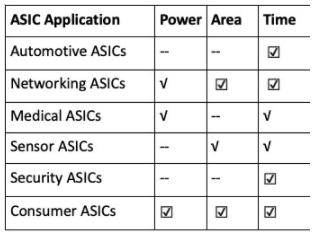

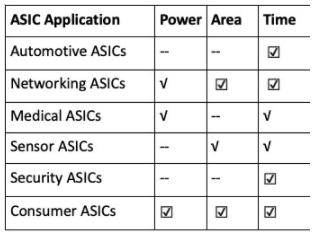

11 基于架構(gòu)和基于流的DFT方法 ASIC設(shè)計平均門數(shù)的增加迫使設(shè)計團(tuán)隊花費(fèi)20%到50%的ASIC開發(fā)工作量測試相關(guān)的問題,以實現(xiàn)良好的測試覆蓋率。雖然遵循設(shè)計測試規(guī)則被認(rèn)為是一種良好的做法,但是

2023-11-10 17:01:04 190

190 DFT 可以降低通過問題器件的風(fēng)險,如果最終在實際應(yīng)用中才發(fā)現(xiàn)器件有缺陷,所產(chǎn)生的成本將遠(yuǎn)遠(yuǎn)高于在制造階段發(fā)現(xiàn)的成本。它還能避免剔除無缺陷器件,從而提高良率。插入 DFT 亦能縮短與測試開發(fā)相關(guān)的時間,并減少測試裝配好的芯片所需的時間。

2019-09-16 14:31:51 1648

1648

墊設(shè)計測試(DFT)可以改善你的上市時間。了解如何使用PCB測試點優(yōu)化設(shè)計在設(shè)計流程的早期。

2019-10-14 07:00:00 2820

2820 近日,西門子旗下業(yè)務(wù)Mentor宣布推出一種創(chuàng)新的可測試性設(shè)計 (DFT) 自動化方法 — Tessent Connect,可提供意圖驅(qū)動的分層測試實現(xiàn)。與傳統(tǒng)的 DFT 方法相比,該方法可幫助 IC 設(shè)計團(tuán)隊以更少的資源實現(xiàn)更快的制造測試質(zhì)量目標(biāo)。

2019-12-04 15:54:49 3484

3484 。可測性設(shè)計(DFT)給整個測試領(lǐng)域開拓了一條切實可行的途徑,目前國際上大中型IC設(shè)計公司基本上都采用了可測性設(shè)計的設(shè)計流程,DFT已經(jīng)成為芯片設(shè)計的關(guān)鍵環(huán)節(jié)。

2020-07-06 11:38:47 9188

9188

隨著ASIC電路結(jié)構(gòu)和功能的日趨復(fù)雜,與其相關(guān)的測試問題也日益突出。在芯片測試方法和測試向量生成的研究過程中,如何降低芯片的測試成本已經(jīng)成為非常重要的問題。DFT(可測性設(shè)計)通過在芯片原始設(shè)計中插入各種用于提高芯片可測性的邏輯,從而使芯片變得容易測試,大大降低了芯片的測試成本。

2020-08-18 14:57:13 2880

2880

軟件測試方法是指測試軟件的方法。隨著軟件測試技術(shù)的不斷發(fā)展,測試方法也越來越多樣化,針對性更強(qiáng);選擇合適的軟件測試方法可以讓我們事半功倍。本文主要介紹的是軟件測試方法和規(guī)范,跟隨小編一起來了解一下具體的測試流程及規(guī)范吧。

2020-10-06 12:20:00 8281

8281

用元素和測試點補(bǔ)充您的操作設(shè)計以促進(jìn)電路板的功能測試被稱為可測試性( DFT )設(shè)計。 DFT 與制造設(shè)計( DFM )不應(yīng)混淆,盡管兩者都是基于 CM 設(shè)備和過程能力的設(shè)計人員活動。 DFM

2020-10-12 20:42:17 3771

3771 licode服務(wù)架構(gòu)及流程

2021-12-07 13:36:10 7

7 在本文中,我們檢查了掃描壓縮確實有助于減少 ASIC 設(shè)計中的測試時間 (DFT),但掃描通道減少也是一種有助于頂層測試時間的方法。

2022-06-02 14:25:09 1504

1504

昨天我們了解到芯片的CP測試是什么,以及相關(guān)的測試內(nèi)容和方法,那我們今天趁熱打鐵,來了解一下CP測試的流程。

2022-07-13 17:49:14 7556

7556 多物理場作用下的多尺度載流子遷移行為至關(guān)重要

界面問題是固態(tài)鋰電池失效的關(guān)鍵原因

DFT和MD方法研究固態(tài)電解質(zhì)構(gòu)效關(guān)系

2022-11-08 10:42:48 863

863 在本篇白皮書中,我們介紹了一個典型設(shè)計的 DFT 組件,并提出了多種可大幅改善 DFT 項目進(jìn)度的智能 DFT 方法。我們展示了如何將結(jié)構(gòu)化 DFT 和即插即用原則用于 DFT 基礎(chǔ)結(jié)構(gòu),來支持與其他設(shè)計開發(fā)工作相似的并行 DFT 開發(fā)和集成。

2022-11-30 10:15:00 575

575 香山處理器的第二代微架構(gòu),南湖微架構(gòu),引入了L3 Cache,可配置多核形態(tài),我們完成流片的是雙核版本的南湖。較第一代雁棲湖,設(shè)計規(guī)模在大幅膨脹,主頻也從1.3GHz提升到2GHz。規(guī)模化之后對DFT設(shè)計及物理實現(xiàn)都造成新的挑戰(zhàn),我們的設(shè)計方法學(xué)也需要與時俱進(jìn)。

2022-12-14 10:51:16 1400

1400 當(dāng)裸片尺寸無法繼續(xù)擴(kuò)大時,開發(fā)者開始考慮投入對 3D 堆疊裸片方法的研究。考慮用于 3D 封裝的高端器件已經(jīng)將當(dāng)前的可測試性設(shè)計 (DFT) 解決方案推向了極限。

2023-02-28 11:39:26 901

901 相信很多ICer們在Light芯片的過程中無論前后端都聽過DFT設(shè)計測試,DFT全稱Design for Test(即可靠性設(shè)計),眾所周知,測試的目的是為了保證芯片成品的質(zhì)量以及功能邏輯的可靠性的必須 措施。

2023-03-06 14:45:10 2413

2413 DFT是確保芯片在制造過程中具有可測試性的一種技術(shù)。DFT友好的ECO是指在進(jìn)行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設(shè)計方法。

2023-03-06 14:47:07 1371

1371 今天這期小編將繼續(xù)與大家一起學(xué)習(xí)DFT的相關(guān)知識和流程代碼,在開始之前,先解決一下上期DFT學(xué)習(xí)的章節(jié)最后留下的問題—DFT工程師在收斂時序timing的時候經(jīng)常遇到的hold的問題,即不同時鐘域的兩個SDFF(掃描單元的SI端hold違例問題。

2023-04-16 11:34:59 4291

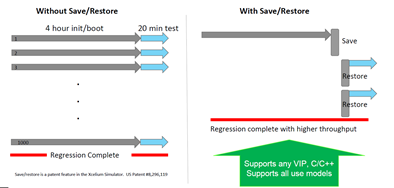

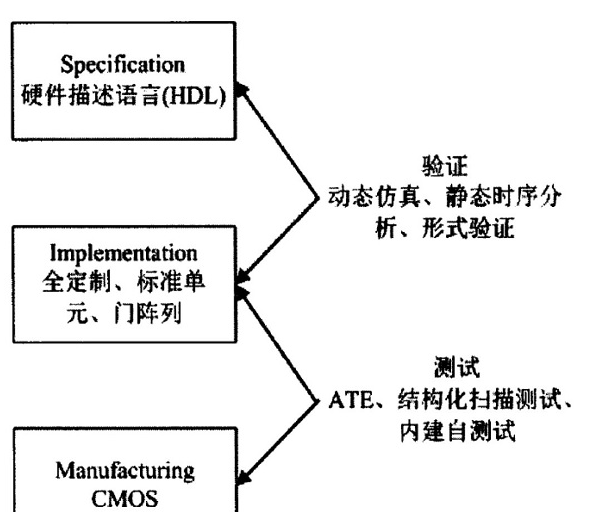

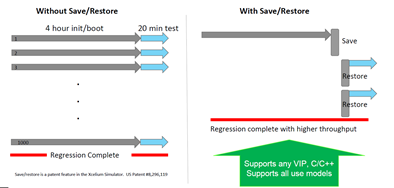

4291 當(dāng)今片上系統(tǒng)的設(shè)計復(fù)雜性日益增加,可能導(dǎo)致長達(dá)數(shù)小時、數(shù)天甚至數(shù)周的可測試性 (DFT) 仿真設(shè)計。由于這些往往發(fā)生在專用集成電路(ASIC)項目結(jié)束時,當(dāng)工程變更單(ECO)強(qiáng)制重新運(yùn)行這些長時間

2023-04-20 10:21:24 1127

1127

一個自動化的測試流程。

2023-05-04 17:48:40 0

0 DFT是確保芯片在制造過程中具有可測試性的一種技術(shù)。DFT友好的ECO是指在進(jìn)行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設(shè)計方法。DFT不友好的ECO會對芯片的測試和調(diào)試帶來很大的困難,可能導(dǎo)致芯片測試效率降低甚至無法測試。

2023-05-05 15:06:37 1262

1262

雖然不同,但兩個同樣重要。專業(yè)一點來說:PCB 測試設(shè)計(DFT) 是一種對電路板和布局優(yōu)化進(jìn)行操作和功能測試的方法。PCB 測試設(shè)計(DFT)可識別任何短路、開路、元件放置錯誤或有故障的元件。

2023-05-29 10:32:22 1969

1969

可測試性設(shè)計(Design for Test,DFT)和可檢驗性設(shè)計(Design for Inspection,DFI)是兩種用于增強(qiáng)產(chǎn)品的測試和檢驗?zāi)芰Φ脑O(shè)計方法。下面是它們的區(qū)別與聯(lián)系,包括

2023-06-26 14:43:19 466

466 隨著半導(dǎo)體技術(shù)的飛速發(fā)展,系統(tǒng)級芯片(SoC)設(shè)計已成為現(xiàn)代電子設(shè)備中的主流。在SoC設(shè)計中,可測試性設(shè)計(DFT)已成為不可或缺的環(huán)節(jié)。DFT旨在提高芯片測試的效率和準(zhǔn)確性,確保產(chǎn)品質(zhì)量和可靠性。

2023-09-02 09:50:10 1513

1513 fft和dft的區(qū)別聯(lián)系 快速傅里葉變換(FFT)和離散傅里葉變換(DFT)是信號處理和數(shù)學(xué)計算領(lǐng)域中最常見的技術(shù)之一。它們都是用于將離散信號從時域轉(zhuǎn)換到頻域的方法,而在此轉(zhuǎn)換過程中,它們都利用

2023-09-07 16:43:53 3139

3139 英諾達(dá)發(fā)布了自主研發(fā)的靜態(tài)驗證EDA工具EnAltius?昂屹? DFT Checker,該工具可以在設(shè)計的早期階段發(fā)現(xiàn)與DFT相關(guān)的問題或設(shè)計缺陷。

2023-09-13 09:05:18 746

746 DFT PLL向量,ATE怎么用? 自動測試設(shè)備(ATE)對PLL(鎖相環(huán))進(jìn)行測試時,我們首先要明白PLL在系統(tǒng)級芯片(SoC)中的重要性。它是SoC中關(guān)鍵的時鐘或信號同步部件,其性能直接影響

2023-10-30 11:44:17 662

662

本文將詳細(xì)介紹顯卡性能測試的方法和流程,以幫助讀者更好地了解如何評估自己的顯卡性能。 一、測試軟件和工具 要進(jìn)行顯卡性能測試,我們首先需要選擇適當(dāng)?shù)能浖凸ぞ摺J袌錾嫌泻芏?b class="flag-6" style="color: red">測試顯卡性能的軟件和工具

2023-12-07 17:21:10 1248

1248 SOC ( System on Chip)是在同一塊芯片中集成了CPU、各種存儲器、總線系統(tǒng)、專用模塊以及多種l/O接口的系統(tǒng)級超大規(guī)模集成電路。

由于SOC芯片的規(guī)模比較大、內(nèi)部模塊的類型以及來源多樣,因此SOC芯片的DFT面臨著諸多問題。

2023-12-22 11:23:51 503

503

近日,杭州廣立微電子股份有限公司(簡稱“廣立微”)宣布與芯來智融半導(dǎo)體科技(上海)有限公司(簡稱“芯來”)以及上海億瑞芯電子科技有限公司(簡稱“億瑞芯”)建立戰(zhàn)略合作伙伴關(guān)系,共同致力于Design for Test(DFT)可測試性設(shè)計領(lǐng)域的發(fā)展。

2024-01-24 17:09:19 518

518 企業(yè)架構(gòu)是一項非常復(fù)雜的系統(tǒng)性工程。公司在充分繼承原有架構(gòu)方法基礎(chǔ)上,博采眾家之長,融合基于職能的業(yè)務(wù)能力分析與基于價值的端到端流程分析,將”傳統(tǒng)架構(gòu)設(shè)計(TOGAF)”與“領(lǐng)域驅(qū)動(DDD)”方法相結(jié)合。

2024-01-30 09:40:00 178

178

電子發(fā)燒友App

電子發(fā)燒友App

評論