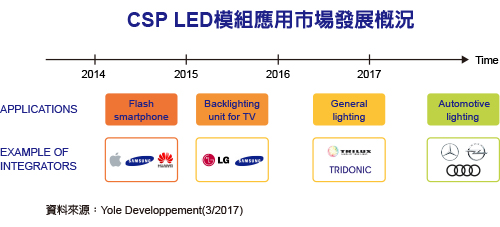

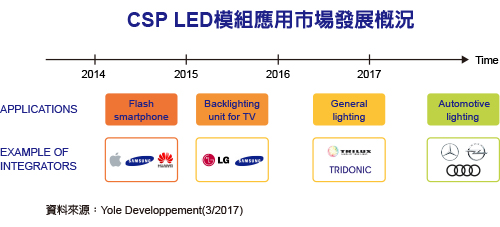

發光二極體(LED)封裝廠在生態系統將日趨邊緣化。上游LED晶粒廠為降低制造成本與微型化晶片尺寸,競相展開晶粒尺寸封裝(Chip Scale Package, CSP)技術布局,且該技術省略封裝制程,遂讓磊晶廠未來營運模式將跳過封裝廠,直接與下游燈具系統商合作,導致封裝廠在供應鏈的重要性大幅下降。

2014-05-06 09:03:50 1776

1776 LED封裝技術出現新面孔。一般半導體廠商已經相當熟悉的芯片級封裝(Chip Scale Package, CSP),正逐漸滲透到LED領域,如手機閃光燈與液晶電視背光用的LED皆已開始導入此一技術。

2017-03-27 09:32:36 2770

2770

1. BGA和CSP封裝技術詳解 2.?干貨分享丨BGA開路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 5181

5181 請問大家,0.4pitch的CSP封裝是怎么布線的,間距太小了

2016-06-29 21:36:01

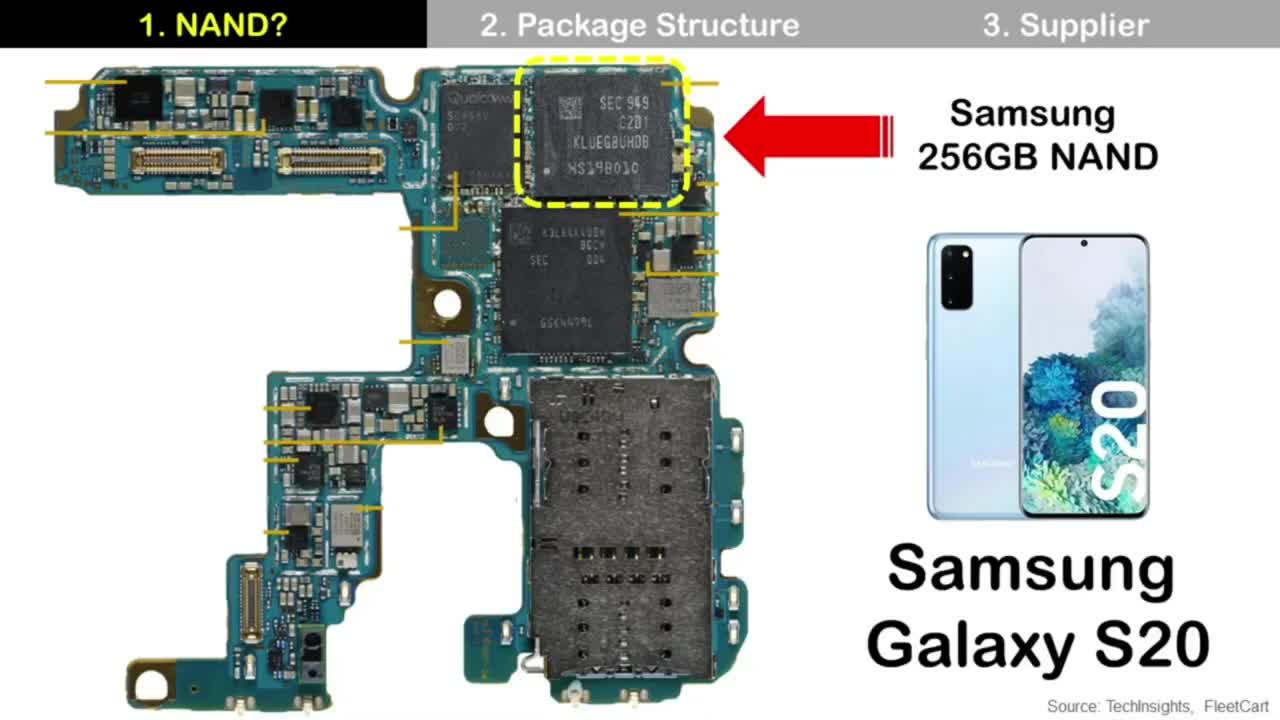

在便攜式、低引腳數和低功率產品中應用廣泛,主要用于閃存、RAM、DRAM存儲器等產品中。目前,超過100家公司開發CSP產品:Amkor、Tessera、Chip-scale、Sharp等,市場潛力巨大。

2020-03-18 09:01:54

csp模式不知道是哪里出現了問題?csp模式為什么不能讓電機轉起來?

2021-09-24 06:24:56

、無阻抗IC白/藍膜片、長期高價求購封裝測試廠淘汰的廢舊QFN、PLCC、BGA、CSP、WL-CSP等各種封裝后的IC芯片、Blue tape、chip、wafer.藍膜片、白膜片、IC硅片、IC晶

2020-12-29 08:27:02

在電子產品開發的實踐過程中,往往會碰到很多干擾方面的問題,這些問題對產品的可靠性和性能指標都會產生嚴重影響,同時需要大量時間和資源去進行排查修正,成為產品量產的瓶頸。在測試測量產品設計中,共地干擾就是較為常見的一類干擾。

2019-02-21 11:29:56

EtherCAT igh主站是如何控制松下伺服(csp模式)的?怎樣去編寫其代碼?

2021-10-08 06:12:54

本帖最后由 eehome 于 2013-1-5 10:01 編輯

便攜式應用本質存在空間限制,因此解決方案的大小至關重要。裸片可以最小化尺寸但是缺乏封裝的諸多優勢,如:保護、行業標準以及能夠被

2011-06-16 16:12:03

初學者,請老師們幫忙解疑!PBGA,CSP,SOP分別是什么意思.

2013-01-17 16:52:09

SMT組件中時,技術遇到的困難最大。在一級封裝組件應用中,倒裝片廣泛用于BGA和CSP,盡管BGA和CSP已經采用了引線-框架技術。在板級組裝中,采用倒裝片可以帶來許多優點,包括組件尺寸減小、性能提高

2013-10-22 11:43:49

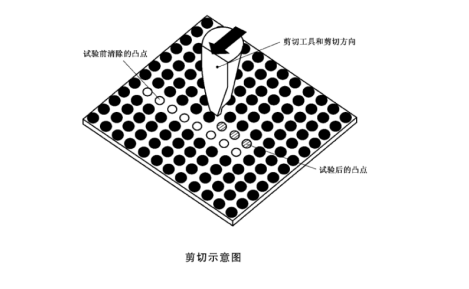

技術,由于減小板尺寸的市場需要,人們對0201元件十分關注。自從1999年中期0201元件推出,蜂窩電話制造商就把它們與CSP一起組裝到電話中,印板尺寸由此至少減小一半。處理這類封裝相當麻煩,要減少

2018-09-10 15:46:13

與CSP一起組裝到電話中,印板尺寸由此至少減小一半。處理這類封裝相當麻煩,要減少工藝后缺陷(如橋接和直立)的出現,焊盤尺寸最優化和元件間距是關鍵。只要設計合理,這些封裝可以緊貼著放置,間距可小至150m

2010-12-24 15:51:40

小,擊穿電壓穩定,良率高,鉗位 電壓一般,電容有低容,普容和高容,6寸可以做回掃型ESD產品;第三代TVS主要以8寸晶圓流片為主,以CSP晶圓級封裝為主(DFN),這種產品是高性能的ESD,采用8寸的先進

2020-07-30 14:40:36

適用于BGA,QFP,QFN.LGA.CSP,DIP.SOP,PLCC等一系列封裝測試的一家微電子公司,主要用于芯片的不良產品的檢測(開短路,電流等),兼容性檢測,及芯片燒錄資料,芯片老化,失效分析等一系列列的產品制作,聯系人張生,***,微信1749001524

2016-11-21 13:31:44

1、準備工作:量產第一件事就是先用最新版芯片精靈(ChipGenius)檢測自已U盤的主控型,做到心中有數,再根據上面的鏈接下載量產工具。再根據主控型號在站內搜索一下,多看幾篇量產教程。做到

2013-06-24 10:54:51

`什么? 你對CSP的了解還不夠?趕快來圍觀吧! 首先,得知道什么叫CSPCSP(Chip Scale Package),又稱為芯片級封裝器件, 其技術性主要體現為讓芯片面積與封裝面積之比超過1

2017-02-24 16:36:32

定義的CSP分類中。晶片級CSP是多種應用的一種低成本選擇,這些應用包括EEPROM等引腳數量較少的器件,以及ASIC和微處理器。CSP采用晶片級封裝(WLP)工藝加工,WLP的主要優點是所有裝配

2018-08-27 15:45:31

單片機的中測和成測是指什么意思,封裝的測試還是功能

2023-11-09 07:48:40

已經采用這些新的設計。一些半導體供應商采用CSP技術制造ASIP,從如何包裝芯片的角度來看,CSP技術與傳統的標準塑料封裝技術不同。CSP技術不再需要傳統塑封中芯片需要的引線框和包裝芯片的塑料封裝體

2018-11-23 16:58:54

和CSP也可達1000條。除了上述指標外,還有一個封裝成本問題。一般講,DIP、SOP價格最低,QFP較高,因而對于低、中引腳數的封裝,它們是優先考慮的形式,當然它們的封裝成本也還取決于引腳數的數目。TAB

2018-11-26 16:16:49

= 同一封裝中集成的die數。以一個帶有]為了提高良率,企業需要遵循兩個原則:1、確定并且僅在封裝中集成已知合格die]2、集成后,驗證跨die的功能,以檢測集成過程中的缺陷,以及其他難以通過測試單個die

2020-10-25 15:34:24

如果復制當前原理圖1到原理圖庫2,新建的元器件能夠復制,但是新器件的封裝無法復制過去,即自己建的元器件封裝卻沒有,這是為什么?如何在復制原理圖時,在原理圖2中復制過去的新器件封裝也能復制過去(或自建的器件及封裝都存在)?

2018-06-02 16:59:36

怎么選擇晶圓級CSP裝配工藝的錫膏?

2021-04-25 08:48:29

CSP具有更突出的優點:①近似芯片尺寸的超小型封裝;②保護裸芯片;③電、熱性優良;④封裝密度高;⑤便于測試和老化;⑥便于焊接、安裝和修整更換。因此,九十年代中期得到大跨度的發展,每年增長一倍左右。由于

2018-09-12 15:15:28

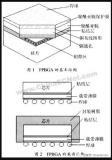

引言 無引線導線封裝(LLP)是一種基于導線架的晶片級封裝(CSP),它可以提高芯片的速度、降低熱阻并減小貼裝芯片所需要的PCB面積。由于這種封裝的尺寸小、高度很低,所以此封裝是高密度PCB

2018-09-10 16:37:26

晶圓級CSP的返修工藝包括哪幾個步驟?晶圓級CSP對返修設備的要求是什么?

2021-04-25 08:33:16

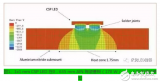

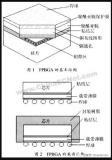

細間距的晶圓級CSP時,將其當做倒裝晶片并采用助焊劑浸蘸的方法進行組裝,以取代傳統的焊膏印刷組裝,如圖2所示,首先將晶圓級CSP浸蘸在設定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關于錫膏裝配和助焊劑裝配的優缺點。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

等。這些測試在一般的工廠內很難完成,這里推薦一些較簡單且容易在工廠完成的 簡易評估方法: ①正常情況下印刷結果檢查——可以選擇含0201/BGA/CSP/QFP等元件的印刷電路板,連續印刷10塊板

2018-11-22 16:27:28

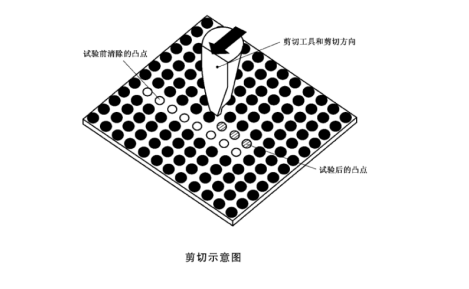

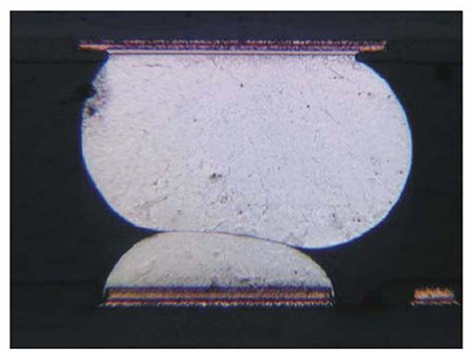

人們對一些應用在手持設各如手機和數碼相機等上的CSP的機械連接強度和熱循環可靠性非常關注。由于 組件中的各種材料的熱膨脹系數不匹配,輕微的熱變形就會導致應力存在于細小的焊點中。為了改善這種現 象

2018-09-06 16:40:03

晶圓級CSP的裝配對貼裝壓力控制、貼裝精度及穩定性、照相機和影像處理技術、吸嘴的選擇、助焊劑應 用單元和供料器,以及板支撐及定位系統的要求類似倒裝晶片對設備的要求。WLCSP貼裝工藝的控制可以參

2018-09-06 16:32:18

和熱循環測試,以及機械測試(推拉,跌落,振動,扭轉和彎曲)等。例如,可以用X-Ray檢查返修前后 焊點的情況,是否短路,在焊點內是否有空洞存在等。如圖1所示。圖1 X-Ray檢查返修前后的焊點

2018-09-06 16:39:59

經底部填充的CSP裝配,其穩健的機械連接強度得到很大的提升。在二級裝配中,由于底部填充,其抵御 由于扭轉、振動和熱疲勞應力的能力得以加強。但經過底部填充的CSP如何進行返修成了我們面臨

2018-09-06 16:32:17

。由于CSP具有更突出的優點:①近似芯片尺寸的超小型封裝;②保護裸芯片;③電、熱性優良;④封裝密度高;⑤便于測試和老化;⑥便于焊接、安裝和修整更換。因此,九十年代中期得到大跨度的發展,每年增長一倍左右

2023-12-11 01:02:56

芯片封裝測試流程詳解ppt?按封裝外型可分為:SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;? 決定封裝形式的兩個關鍵因素:?封裝效率。芯片面積/封裝面積,盡量接近1:1

2012-01-13 11:46:32

問題,CSP不但具有裸芯片的優點,還可像普通芯 片一樣進行測試老化篩選,使MCM的成品率具有保證,大大促進了MCM的發展和推廣應用。目前MCM已經成功地用于大型通用計算機和超級巨型機中,今后將用于工作站

2018-11-23 16:59:52

請問ADN4670BCPZ焊接溫度曲線有么?以及這種CSP封裝的焊接需要注意的事項有哪些?

2019-01-18 16:44:20

安卓開飯量產測試是有專門測試程序么?像firefly和友善的RK開發板都有特別多的接口,還有的帶屏幕各種傳感器,那么量產的時候要如何測試呢?是專門的測試工具和測試程么,那么多的接口一個個手工測是不是太慢?

2019-04-01 03:47:10

由于疊層CSP封裝的復雜性,其振動特性很難用精確的理論模型表示。同時,由于傳統的共振準則沒有考慮到系統的變異性和模糊性,導致分析結果與真值具有較大偏差。該文利用

2009-02-27 15:37:11 9

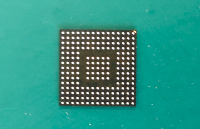

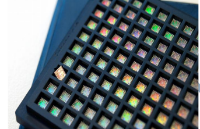

9 CSP產品簡介封裝完成後之面積(Footprint)約為晶片(Die)之1.2倍依其結構可分為四類Flex Circuit InterposerRigid Substrate InterposerLead Frame (Lead-on-Chip)Wafer Level Assembly可靠度簡

2009-07-06 09:28:14 12

12 基于進程代數的CSP 方法是一種重要的形式化協議分析驗證方法。本文首先簡單介紹了CSP 相關理論,并以NSPK 協議為例系統概述了安全協議的CSP 建模方法。為更好的查明協議的安全缺

2009-08-06 11:22:16 12

12 可以解決眾多封裝難題的CSP-ASIP

無線手持設備、掌上電腦以及其他移動電子設備的增加導致了消費者對各種小外形、特征豐富產品的需要。為了滿足越來越小的器件同時具有

2009-03-28 17:02:02 927

927 摘要:本文詳細討論了Maxim的晶片級封裝(WL-CSP),其中包括:晶圓架構、卷帶包裝、PCB布局、安裝及回流焊等問題。本文還按照IPC和JEDEC標準提供了可靠性測試數據。 注

2009-04-21 11:30:27 8552

8552

SMT最新技術之CSP及無鉛技術

CSP、0201無源元件、無鉛焊接和光電子,可以說是近來許多公司在PCB上實踐和積極*價的熱門先進技術。

2009-11-16 16:41:10 1405

1405 晶圓級CSP的返修工藝

經底部填充的CSP裝配,其穩健的機械連接強度得到很大的提升。在二級裝配中,由于底部填充,其抵御 由于

2009-11-20 15:42:17 483

483 晶圓級CSP的裝配工藝流程

目前有兩種典型的工藝流程,一種是考慮與其他元件的SMT配,首先是錫膏印刷,然后貼裝CSP,回流焊接

2009-11-20 15:44:59 1348

1348 半加成法SAP于載板之量產

當線寬線距小于50μm(2mil)者,傳統CCL的減成法幾已無用武之地。而目前CSP或FC覆晶等載板的Line/Width已逼近到了15μm/15μm

2009-12-22 09:29:33 18193

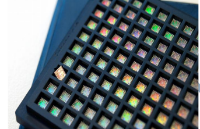

18193 CSP封裝內存

CSP(Chip Scale Package),是芯片級封裝的意思。CSP封裝最新一代的內存芯片封裝技術,其技術性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超

2009-12-25 14:24:49 636

636 高級封裝,高級封裝是什么意思

晶片級封裝CSP(Chip Scale Package)。幾年之前以上所有的封裝其封裝本體面積與芯片面積之比通常都是

2010-03-04 11:13:29 1420

1420 什么是CSP封裝

近幾年的硬件發展是日新月異,處理器已經進入G赫茲時代,封裝形式也是經歷了數種變化。不過,光有一顆速急力猛的芯還遠遠不夠

2010-03-04 11:43:25 14777

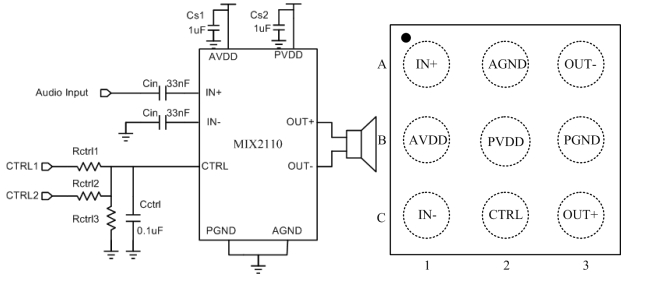

14777 上海矽諾微電子針對目前的便攜式市場推出全系列兼容的CSP-9封裝的D類音頻功放。該系列產品目前有三顆,分別是MIX

2011-01-11 09:15:17 1444

1444

2007年由飛利浦Lumileds推出的CSP技術,歷經五六年的沉寂,從2013年起漸漸被業界提及,去年開始更是頻頻登上各大展會和論壇。臺灣新世紀光電更預測CSP具備單位亮度更高,厚度更薄及成本低

2016-05-12 16:29:52 2687

2687

OV2715_CSP3_Datasheet

2016-12-25 23:00:49 4

4 芯片級封裝介紹本應用筆記提供指引使用與PCB安裝設備相關的芯片級封裝。包括系統的PCB布局信息制造業工程師和制造工藝工藝工程師。 包概述 倒裝芯片CSP的包概述半導體封裝提供的芯片級封裝代表最小

2017-03-31 10:57:32 45

45 超級CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級封裝

2017-09-14 11:31:37 22

22 CSP封裝的芯片測試,由于其封裝較小,采用普通的機械手測試無法實現,目前主要采用類似晶圓測試的方法,在芯片完成置球封裝后,先不做劃片,而直接用探針卡進行測試,測試完成后,再實行劃片、分選和包裝。

2017-10-27 15:11:10 7297

7297 模型檢測是通信順序進程(communicatmg sequential processes,簡稱CSP)形式化驗證的重要手段.當前,CSP模型檢測方法基于操作語義,需將進程轉化為遷移系統,進而

2018-01-23 16:03:53 1

1 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技術(下一代技術為襯底級別封裝,其封裝大小與芯片相同)。為了達成這一目的,LED制造商

2018-06-07 15:40:00 945

945

近幾年大陸背光產品價格持續下滑,億光等LED廠商在背光市場出貨比重仍不低,為避開陸廠價格競爭,今年億光將以mini LED、CSP封裝產品搶攻高端背光應用。

2018-04-27 11:20:00 2560

2560 目前CSP LED的主流結構可分為有基板和無基板,也可分為五面發光與單面發光。所說的基板自然可以視為一種支架。很顯然,為了滿足CSP對封裝尺寸的要求,傳統的支架,如2835,的確不能使用,但并不

2018-07-12 14:34:00 10628

10628 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技術(下一代技術為襯底級別封裝,其封裝大小與芯片相同)。為了達成這一目的,制造商盡可能

2018-08-10 15:43:52 14433

14433 CSP(Chip Scale Package)封裝,是芯片級封裝的意思。CSP封裝最新一代的內存芯片封裝技術,其技術性能又有了新的提升。CSP封CSP封裝裝可以讓芯片面積與封裝面積之比超過

2018-08-17 15:25:38 18203

18203 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技(下一代技術為襯底級別封裝,其封裝大小與芯片相同)。

2018-09-05 08:36:00 13375

13375 CSP封裝是最新一代的內存芯片封裝技術,其技術性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超過1:1.14,已經相當接近1:1的理想情況,絕對尺寸也僅有32平方毫米,約為普通的BGA的1/3,僅僅相當于TSOP內存芯片面積的1/6。與BGA封裝相比,同等空間下CSP封裝可以將存儲容量提高三倍。

2019-06-24 14:12:36 19779

19779 11月19日消息,據報道,臺積電與Google等美國客戶正在一同測試,合作開發先進3D堆棧晶圓級封裝產品,并計劃2022年進入量產。臺積電將此3D堆棧技術命名為“SoIC封裝”,可以垂直與水平的進行芯片鏈接及堆棧封裝。

2020-11-20 10:56:30 2161

2161 電子發燒友網為你提供TE(ti)CAT-CSP-5T相關產品參數、數據手冊,更有CAT-CSP-5T的引腳圖、接線圖、封裝手冊、中文資料、英文資料,CAT-CSP-5T真值表,CAT-CSP-5T管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-07-08 21:00:04

接近為1,而且電器性能以及可靠性也有大幅提升。正因于此,CSP封裝不斷滲透更多的應用市場,并且還在不斷擴大,而與此同時,與其相關的測試技術也在迅速發展。 CSP封裝的芯片測試,由于其封裝較小,無法采用普通的機械手測試實現,只有通過

2021-12-03 13:58:36 2405

2405 先進封裝形式μBGA、CSP的回流焊接技術介紹說明。

2022-05-06 15:17:46 4

4 倒裝芯片 CSP 封裝

2022-11-14 21:07:58 19

19 CSP封裝(Chip Scale Package)是指芯片級封裝,其封裝尺寸和芯片核心尺寸基本相同,一般芯片面積與封裝面積的比例約在1:1.1。CSP封裝最先規模應用在消費電子和個人電腦,與我們的生活息息相關。

2023-03-28 14:52:09 10625

10625 CSP2510C 數據表

2023-04-26 19:29:44 1

1 CSP(Chip Scale Package)封裝芯片是一種高密度、小尺寸的封裝形式,它在集成電路行業中具有廣泛的應用。對于CSP封裝芯片的測試方法而言,主要涉及到以下幾個方面:

2023-06-03 10:58:16 1142

1142 光電傳感器WL-CSP封裝芯片底部填充膠應用由漢思新材料提供光電傳感器芯片(CCD)經過聯系客戶工程技術和研究其提供的封裝工藝流程。了解到以下信息。客戶用膠項目是:光電傳感器芯片(CCD

2023-05-18 05:00:00 546

546

電子封裝是現代電子產品中不可或缺的一部分,它將電子元件組裝在一起,形成了一個完整的電子系統。其中,BGA和CSP是兩種常見的電子封裝技術,它們各有優缺點,廣泛應用于半導體制造、LCD顯示器等領域

2023-06-14 09:11:18 850

850

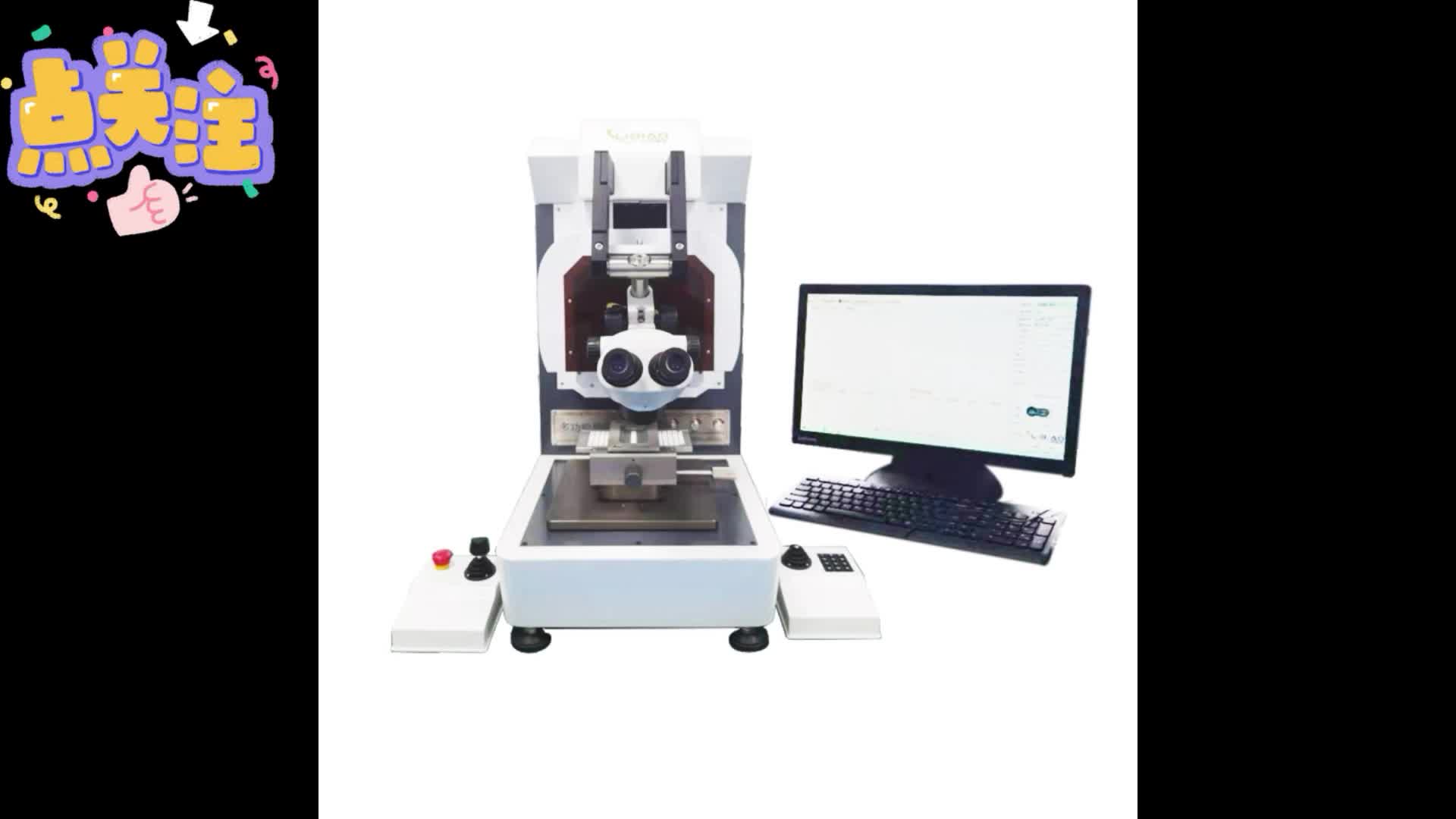

包括球柵陣列封裝(BGA)、無引線封裝(QFN)、芯片級封裝(CSP)等。 本文科準測控的小編將介紹半導體封裝推拉力測試機的技術參數和應用范圍,并探討其在BGA封裝測試中的重要性。 一、測試內容 引腳連接強度:測試封裝器件引腳與

2023-06-26 10:07:59 581

581

短1/5~1/6左右,同時CSP的抗噪能力強,開關噪聲只有DIP(雙列直插式封裝)的1/2。這些主要電學性能指標已經接近裸芯片的水平,在時鐘頻率己超過雙G的高速通信領域,LSI芯片的CSP將是十分理想的選擇。

2023-08-20 09:42:07 1110

1110

芯片封裝測試有技術含量嗎?封裝測試是干嘛的?? 芯片封裝測試是指針對生產出來的芯片進行封裝,并且對封裝出來的芯片進行各種類型的測試。封裝測試是芯片生產過程中非常關鍵的一環,而且也需要高度的技術含量

2023-08-24 10:41:57 2322

2322 晶圓封裝測試什么意思? 晶圓封裝測試是指對半導體芯片(晶圓)進行封裝組裝后,進行電性能測試和可靠性測試的過程。晶圓封裝測試是半導體芯片制造過程中非常重要的一步,它可以保證芯片質量,并確保生產出的芯片

2023-08-24 10:42:07 1311

1311 CSP是近幾年才出現的一種集成電路的封裝形式,目前已有上百種CSP產品,并且還在不斷出現一些新的品種。盡管如此,CSP技術還是處于發展的初期階段,因此還沒有形成統一的標準。不同的廠家生產不同的CSP

2023-09-08 14:09:40 294

294 BGA和CSP封裝技術詳解

2023-09-20 09:20:14 951

951

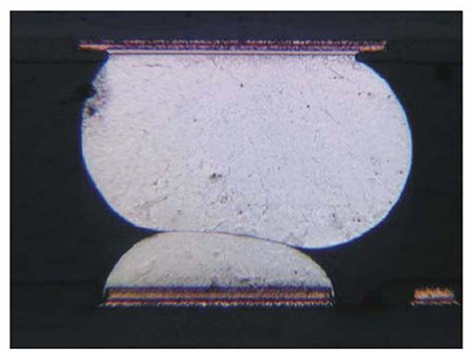

簡要解讀BGA、CSP封裝中的球窩缺陷

2023-10-08 08:47:53 339

339

CSP的高效優點體現在:用于板級組裝時,能夠跨出細間距(細至0.075mm)周邊封裝的界限,進入較大間距(1,0.8,0.75,0.5,0.4mm)區域陣列結構。 已有許多CSP器件在消費類電信領域

2023-10-17 14:58:21 321

321 2023年10月18日,昆山同興達芯片和金凸塊全過程的封裝測試項目量產儀式在昆山隆重舉行,下游客戶包括奕力科技股份有限公司的ic設計等世界級大工廠蒞臨參加,標志同興達先進封裝測試項目大規模量產化和市場化與上游公司的合作模式,進一步深化。

2023-10-20 09:46:43 507

507 為了實現集成電路芯片的電通路,一般需要將芯片裝配到在塑料或陶瓷載體上,這一過程可以稱為CSP。CSP的尺寸只是略大于芯片,通常封裝尺寸不大于芯片面積的1.5倍或不大于芯片寬度或長度的?1.2

2023-12-22 09:08:31 535

535

提及CSP封裝基板領域,興森科技目前每月的產量約為3.5萬平方米,其中廣州基地生產能力達到了2萬平方米/月,已處于飽和狀態;而廣州興科與珠海基地的產能分別為1.5萬平方米/月,且利用率都超過了50%。

2024-01-30 09:59:33 260

260 立錡推出的低壓輸入、CSP 小封裝降壓轉換器系列,不僅滿足各式小型穿戴式和 IoT 物聯網應用的需求,更在性能和尺寸上取得了絕佳平衡。

2024-03-14 15:03:10 192

192

電子發燒友App

電子發燒友App

評論