, I have this basic doubt that why at all HDL coder is there in Matlab when we have system generator

2018-12-18 10:40:58

你好: 我是一個購買的帳戶,所以我的許可證應該允許訪問所有內容。但是當我使用System Generator for DSP時,系統說我的SysGen簽出許可證失敗了。有人知道怎么解決嗎?謝謝

2019-01-28 07:16:36

錯誤:System Generator for DSP(SysGen)的許可證簽出失敗。無法聯系Xilinx許可證管理器。請檢查以下內容:(1)XILINX環境變量指向有效的ISE安裝(2

2018-12-29 10:35:12

FPGA中的數字控制器是什么?System Generator中的PID控制器是如何設計的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個不讓我繼續參與我的硬件協同仿真項目的問題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據我的理解,System Generator是MatLab到RTL的轉換,因此不包括Vivado的優化過程。問題1--是真的。確實,Vivado中的優化將大大改變系統描述,而系統描述不會向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天評估包,Matalb 2014B。簡單地說我想使用FIR編譯器,當我嘗試編輯它的參數時,我得到了兩個錯誤: - 1.“來自MEX

2020-03-24 09:01:59

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何時才能勝任64位Windows 7?以上來自于谷歌翻譯以下為原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,發現getway in這個模塊參數設置變化導致MATLAB閃退問題,貼圖如下其中getway in 這個模塊數據類型換成定點有符號或者無符號數都不得行,換成布爾值又會出現錯誤,不知為何啊!求教。

2018-01-05 21:43:53

翻譯成verilog,在FPGA里面實現,即system generator。altera有沒有類似的接口,與matlab可以互連,直接在matlab里設計我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

big.LITTLE和GPU相結合實現性能和功耗的最佳匹配

2021-02-02 07:00:45

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

各位好,最近在使用system generator 搭建一個ifft設計模塊,使用ise調用,但是在下載到板子后,示波器輸出波形去在沒有輸入的情況下仍然有波形,確定不是噪聲,波形還是很規律,求解釋呀!

2016-07-13 13:21:30

使用system generator導入xilinx模塊時,只要連線兩個模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

隨著集成電路的規模和復雜度不斷增大,驗證的作用越來越重要。要在較短的時間內保證芯片最終能正常工作,需要將各種驗證方法相結合,全面充分地驗證整個系統。FF-DX是一款高性能定點DSP,為了在提升芯片

2011-12-07 17:40:14

.Vivado 2016.4與Spartan-6不兼容。據Xilinx稱,Vivado不支持任何早于7系列的設備系列。)根據以下說明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在內部,有一個基于VHDL的框架,它將定制板上的不同部分與“DSP內核”連接,后者是在System Generator下開發的。在這

2019-01-15 10:39:11

在system generator中,我把(-128~127),變為(-1~1),但是下載到硬件中,使用chipscope抓取到的數據確實(-128~127),請問是怎么回事

2016-08-10 15:32:38

有做System Generator處理圖像的嗎?遇到一些問題,一起商量下

2020-09-28 19:04:58

generated by system generator, which one is moreefficency? Regards Ryan

2019-02-20 10:25:40

嗨,我正在嘗試學習如何使用System Generator來創建自己的IP核。首先,我在DocNav中找到了一個ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

編解碼器模塊將數字信號轉換為模擬信號格式。請讓我知道如何將AC97模塊與基于sysgen的設計模塊相結合。恐怕我必須使用包括EDK處理器在內的設計程序,我對此并不熟悉。有沒有更簡單或更快的方法,最多只使用系統生成器或ISE?我為初學者的問題道歉。謝謝。jein

2020-03-06 08:47:56

開始。其中物聯網軟硬件是很關鍵的一環,如何將軟件和硬件相結合,嵌入式軟件系統和硬件系統就需要先了解一下。一、嵌入式硬件系統大多數嵌入式系統的硬件平臺。它包括兩部分:1、以通用處理器為中心的協議處理...

2021-12-22 06:54:10

時間片調度法的原理是什么?基于μC/OSII時間片調度過程是怎么進行的?如何設計一種優先級和時間片相結合的調度法?

2021-04-27 06:41:33

各位大佬,我在安裝System Generator時,跟著教程走,發現在vivado中沒有出現System Generator for DSP這個選項,請問是我哪里安裝得不對嗎?

2023-09-26 21:54:58

當我完成SDx 2017.2的安裝時,沒有安裝System Generator的選項。我正在運行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

最近想做個小車,遇到個問題,就是想將履帶和輪子相結合,但是怎么樣設計呢?求各位幫忙一下!

2013-01-10 00:07:32

摘要: 嵌入式Linux和Java技術非常適于協同工作,他們的結合預示著下一代嵌入式系統已經開始出現。同時這種組合使開發技術進入一個新的層次,也提供了一個新的配置的選擇。在嵌入式Linux操作系統和Java技術相結合的開發環境...

2021-11-04 08:52:21

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創建一個雙向(inout)端口。我正在嘗試為Xilinx的外部存儲器創建一個接口

2019-05-09 14:36:24

最近在使用system generator設計一個rs編碼譯碼的模型,總的思想是在rs編碼產生信號后,插入一個誤碼,然后作為信號源進行解碼,看是否能夠正常的進行解碼,求解是怎么才能把rs編碼后的信號存儲起來作為信號源

2016-07-20 20:13:59

怎樣去設計FFD和RFD相結合的鏈狀拓撲結構?如何去實現公交車報站功能?如何去實現公交車輛定位?

2021-05-20 06:13:38

怎樣才能使JTAG邊界掃描與功能測試相結合

2021-05-06 07:56:42

智能小車如何與機械臂相結合?

2021-12-27 06:15:24

有用Xilinx的system generator做圖像處理的嘛?求交流 。我正在用這個做圖像處理,已經用了3個月了,在做一些算法,遇到一些困難,求一起交流學習。發現用這個開發的人真不多啊。

2014-05-09 14:57:21

做的一個簡單的狀態機與枚舉相結合的程序,挺簡單的。

2018-08-15 08:06:07

本帖最后由 eehome 于 2013-1-5 10:01 編輯

EDA先鋒工作室的精品書籍,國內少有的系統講述FPGA設計和驗證的好書,特別是驗證部分很精華,現在和大家分享,同時附上本書的實例源代碼和Verilog HDL語法國際標準。

2011-08-02 14:54:41

將模擬鑒相器輸出與頻率牽引輸出相結合的方法

2019-09-26 09:00:59

xilinx公司的網絡教程“利用 System Generator 進行 DSP 設計”誰有?上傳一份給小弟吧

2013-03-14 12:17:03

以前,我們有Matlab 2006a和ISE 8.2i,并且正在使用System Generator。我們不得不重新安裝Matlab 2006a以啟用新的工具箱,但現在Simulink中沒有

2018-11-19 14:42:56

介紹模擬峰值電壓的檢測方式,敘述基于Verilog-HDL 與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法, 給出相關的Verilog-HDL 主模塊部分。

2009-04-16 10:53:02 22

22 鑲鋼套與涂抹環氧塑料相結合修復曲軸軸頭

2009-05-21 14:51:15 25

25 介紹模擬峰值電壓的檢測方式,敘述基于Verilpg-HDL與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法,給出相關的Verilpg-HDL主模塊部分。

2009-07-18 10:30:06 14

14 本文首先介紹RVM驗證方法學和覆蓋率驅動技術,然后詳細分析如何使用結合覆蓋率驅動技術的RVM驗證方法學對SOC(System On Chip)進行完備的功能驗證, 最

2009-09-05 08:53:00 15

15

采用Gardner算法,對QPSK調制解調系統中的位同步系統進行設計與實現,大大提高了系統性能和資源利用率。重點闡述采用FPGA開發環境System Generator系統設計工具進行位同

2010-07-21 16:12:40 26

26 摘要:介紹模擬峰值電壓的檢測方式,敘述基于Verilog-HDL與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法,給出相關的Verilog-HDL主模塊部分。

2009-06-20 15:14:00 867

867

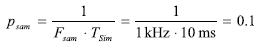

深入了解賽靈思System Generator中的時間參數

基于模型的設計(MBD)因其在縮小實時系統抽象的數學建模和物理實現之間差距方面的光明前景而備受關注。通過使用相同的

2009-12-29 11:40:30 1300

1300

該設計是基于System Generator設計平臺,在Matlab/Simulink環境下搭建系統模型,再進行功能仿真和驗證,完成QPSK調制器的設計。仿真結果表明,所設計的調制器能產生正確QPSK波形,達到了預期效果

2011-10-17 16:10:51 65

65 本書以實例講解的方式對HDL語言的設計方法進行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語言的基本概念、設計流程、語法及建模方式等。

2012-11-28 13:32:57 943

943 Xilinx公司推出的DSP設計開發工具System Generator是在Matlab環境中進行建模,是DSP高層系統設計與Xilinx FPGA之間實現的橋梁。在分析了FPGA傳統級設計方法的基礎上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 動靜態相結合LED顯示【C語言版】動靜態相結合LED顯示【C語言版】動靜態相結合LED顯示【C語言版】動靜態相結合LED顯示【C語言版】

2015-12-29 15:51:46 0

0 本章介紹了如何編寫測試驗證程序(test bench)。測試驗證程序用于測試和驗證設計的正確性。Verilog HDL提供強有力的結構來說明測試驗證程序。verilog相關教程材料,有興趣的同學可以下載學習

2016-04-25 16:09:32 17

17 Xilinx FPGA工程例子源碼:System Generator的設計實例

2016-06-07 14:41:57 22

22 設計與驗證,很不錯的一本書,《設計與驗證》以實例講解的方式對HDL語言的設計方法進行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語言的基本概念、設計流程、語法及建模方式等內容

2016-10-10 17:04:40 566

566 環境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實現步驟 1、模型搭建與仿真 在simulink環境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

最新版System Generator支持快速開發和實現基于All Programmable FPGA、SoC和MPSoC的無線電設計 賽靈思日前宣布推出高級設計工具System Generator

2017-02-09 01:23:41 279

279 在這個簡短的網絡研討會上,來自 ?MathWorks?? 的工程師演示了如何使用 MATLAB? 、 Simulink?? 和 ?HDL Coder?? 實現和驗證高性能 ?FFT (針對

2017-02-09 02:26:11 268

268 一直都在System Generator下做圖像處理相關的算法,感覺SysGen挺強大的,前幾天突發奇想,能否直接用SysGen實現數據的通信呢,畢竟一句HDL代碼都不寫對于做FPGA的人來說卻是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設計的方法都試驗過了,更高級的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司進行數字信號處理開發的一種設計工具,它通過將Xilinx開發的一些模塊嵌入到Simulink的庫中,可以在Simulink中進行定點仿真,可是設置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系統級建模工具,它是擴展mathworks公司的MATLAB下面的simulink平臺,添加了XILINX FPGA專用的一些模塊。加速簡化了FPGA的DSP系統級硬件設計。

2017-02-11 19:21:33 7386

7386

利用System Generator軟件平臺,實現基于模塊化建模方法的變換器建模,并簡化語言編寫控制系統的復雜過程。研究了從MATLAB-Xilinx環境中導出使用模塊化建模方法搭建的控制算法。通過

2017-11-15 14:31:34 4985

4985

現在的FPGA算法的實現有下面幾種方法: 1. Verilog/VHDL 語言的開發 ; 2. system Generator; 3. ImpulsC 編譯器實現從 C代碼到 HDL 語言; 4.

2017-11-17 14:29:06 7298

7298 在FPGA平臺上應用System Generator工具實現了高精度頻率估計Rife算法。不同于傳統的基于HDL代碼和IP核的設計方法,采用System Generator工具可以使復雜算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是專門為數字信號算法處理而推出的模型化設計平臺,可以快速、簡單地將DSP系統的抽象算法轉換成可綜合的、可靠的硬件系統,彌補了大部分對C語言以及Matlab工具很熟悉的DSP工程師對于硬件描述語言VHDL和Verilog HDL認識不足的缺陷。

2018-07-19 09:32:00 3716

3716

PLD/FPGA 常用開發軟件System Generator 9.10。 業內領先的高級系統級FPGA開發高度并行系統。

2017-11-26 11:34:56 12

12 采用System Verilog語言設計了一種具有層次化結構的可重用驗證平臺,該平臺能夠產生各種隨機、定向、錯誤測試向量,并提供功能覆蓋率計算。將驗證平臺在Synopsys公司的VCS仿真工具上運行

2018-01-12 11:28:24 2379

2379

本視頻產品演示介紹了 Xilinx 系統生成器(System Generator)和 Xilinx ISE? 項目瀏覽器(Project Navigator)設計環境之間的新整合。

2018-06-06 13:46:00 3024

3024

了解如何將Vivado HLS設計作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設計保存為IP模塊,并了解如何將此IP輕松整合到System Generator for DSP的設計中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多個時鐘域,從而可以實現復雜的DSP系統。

2018-11-27 06:42:00 3450

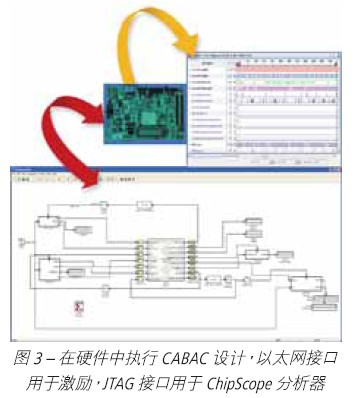

3450 了解如何使用Vivado System Generator for DSP進行點對點以太網硬件協同仿真。

System Generator提供硬件協同仿真,可以將FPGA中運行的設計直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 System Generator 數字上下變頻 (DUC/DDC)模塊集的易用性大幅提升,使得更加便于無線算法開發。這些新型模塊還添加了有助于加速驗證和編譯運行時間的增強功能,所有這些模塊提供了七八種參數設置。

2019-07-31 09:22:49 2293

2293 ),這里的D也是描述的首字母。 也就是說,HDL的D,是描述的意義。HDL也就是硬件描述語言。 2. 為了支持Soc的驗證,支持數模混合,新的System Verilog加入了HVL(Hardware Verification Language),即硬件驗證語言。 3. 合并之前的硬件描述語言功能,稱為

2021-04-15 15:44:02 2773

2773 mysql的安裝-與php、Apache相結合(深圳核達中遠通電源技術有限公司 產品功能用途)-文檔為mysql的安裝-與php、Apache相結合總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-18 16:33:33 20

20 本篇博文是面向希望學習 Xilinx System Generator for DSP 入門知識的新手的系列博文第一講。其中提供了有關執行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

如何使熱插拔與電子熔絲相結合

2022-11-03 08:04:33 0

0 本文使用Easier UVM Code Generator生成包含多個agent和interface的uvm驗證環境。

2023-06-06 09:13:02 584

584

正在加载...

電子發燒友App

電子發燒友App

評論