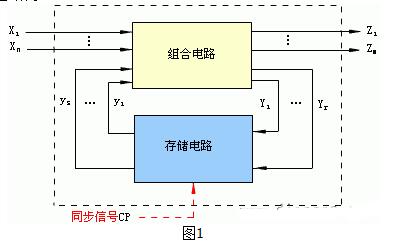

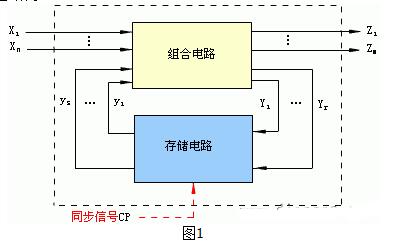

在數字電路中,凡是任一時刻的穩定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態有關者都叫時序邏輯電路。時序邏輯電路結構示意圖如圖2-41所示。時序邏輯電路的狀態是靠具有存儲功能的觸發器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

作者: 小魚,Xilinx學術合作 一. 概述 時序邏輯示意圖,如下圖所示。數據從一個寄存器出來,經過組合邏輯到達下一個寄存器。 在學習數字電路的過程中,我們都知道時序邏輯,但是大家對時序邏輯真的

2020-12-25 14:39:28 4147

4147

《UltraFast 設計方法時序收斂快捷參考指南》提供了以下分步驟流程, 用于根據《UltraFast設計方法指南》( UG949 )中的建議快速完成時序收斂: 1初始設計檢查:在實現設計前審核

2021-11-05 15:10:26 4603

4603

數字電路根據邏輯功能的不同特點,可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另一類叫做時序邏輯電路,簡稱時序電路或時序邏輯。

2022-12-01 09:04:04 459

459 時序邏輯電路的精華——計數器

2022-12-29 09:23:56 1010

1010 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-01-13 13:57:47 1830

1830

數字邏輯電路分為組合邏輯電路和時序邏輯電路。時序邏輯電路是由組合邏輯電路和時序邏輯器件構成(觸發器),即數字邏輯電路是由組合邏輯和時序邏輯器件構成。

2023-03-21 09:49:49 476

476 芯片設計是現代電子設備的重要組成部分,其中組合邏輯和時序邏輯是芯片設計中非常重要的概念。組合邏輯和時序邏輯的設計對于構建復雜的電路系統至關重要。

2023-08-30 09:32:15 809

809 表達式,畫出邏輯電路圖,并驗證4、利用74LS153和74LS138組成三位并行碼比較器,要求當兩個數相等時,輸出為“0”,否則輸出為“1”5、 利用74LS153、74LS48和一位LED七段

2020-06-09 04:31:10

時序邏輯電路一、實驗目的 1.掌握D、JK觸發器的邏輯功能和使用 2.掌握中規模集成計數器74LS161

2009-09-16 15:08:37

時序邏輯電路的特點

2019-10-08 05:34:53

、可編程器件設計時序邏輯電路的特點、方法;3 掌握時序邏輯電路的調試方法;4 進一步提高排除數字電路故障的能力。

2009-03-19 15:10:18

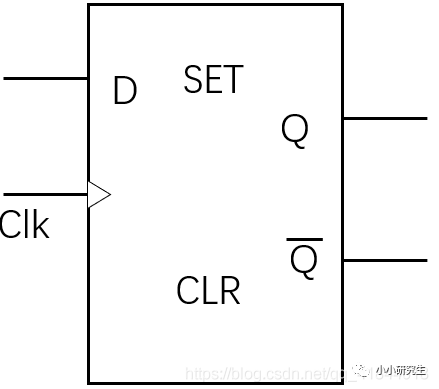

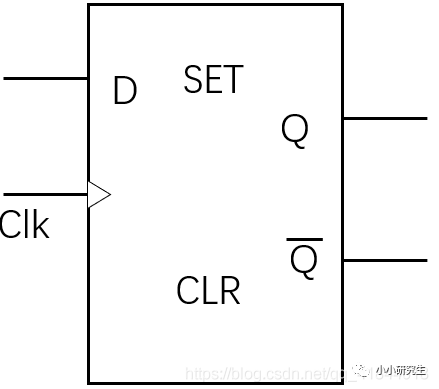

時序邏輯電路設計6.1 基本D觸發器的設計6.2 JK觸發器6.3 帶異步復位/置位端的使能T觸發器6.4 基本計數器的設計6.5 同步清零的計數器6.6 同步清零的可逆計數器6.7 同步預置數的計數器

2009-03-20 10:04:53

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經學習了組合邏輯電路的分析與設計的方法,這一章我們來學習時序電路的分析與設計的方法。在學習時序邏輯電路時應注意的重點是常用時序部件的分析與設計這一

2018-08-23 10:28:59

大神求救!我現在想要用FPGA實現一個數與一個數組(寬度為64)數相乘,累加,再取平均,用的是時序邏輯加上非阻塞賦值的方法實現,即從數組0開始相乘,一直到數組63,當乘完63時,將累加的數取平均輸出

2017-09-13 11:02:51

實現的布局位置和布線結果(Netlist)固定下來,保證這一布局布線結果可以在新的編譯中重現,相應地,這一組邏輯的時序收斂結果也就得到了保證。這個部分保留上一次編譯結果的過程就是Incremental

2016-06-02 15:54:04

的過程是從一次成功的時序收斂結果開始,把特定的一組邏輯(Design Partition)在FPGA上實現的布局位置和布線結果(Netlist)固定下來,保證這一布局布線結果可以在新的編譯中重現,相應

2017-12-27 09:15:17

基本的時序分析理論1本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態時序分析(STA,Static

2015-07-09 21:54:41

重新布局布線后的時序違規情況關于約束,我們要稍微提一下兩種不恰當的約束方法,即欠約束和過約束。我們假設下面提到的兩種情況下的原始系統實際時序要求都是一樣的,即前面我們所說的:din1 <

2015-07-14 11:06:10

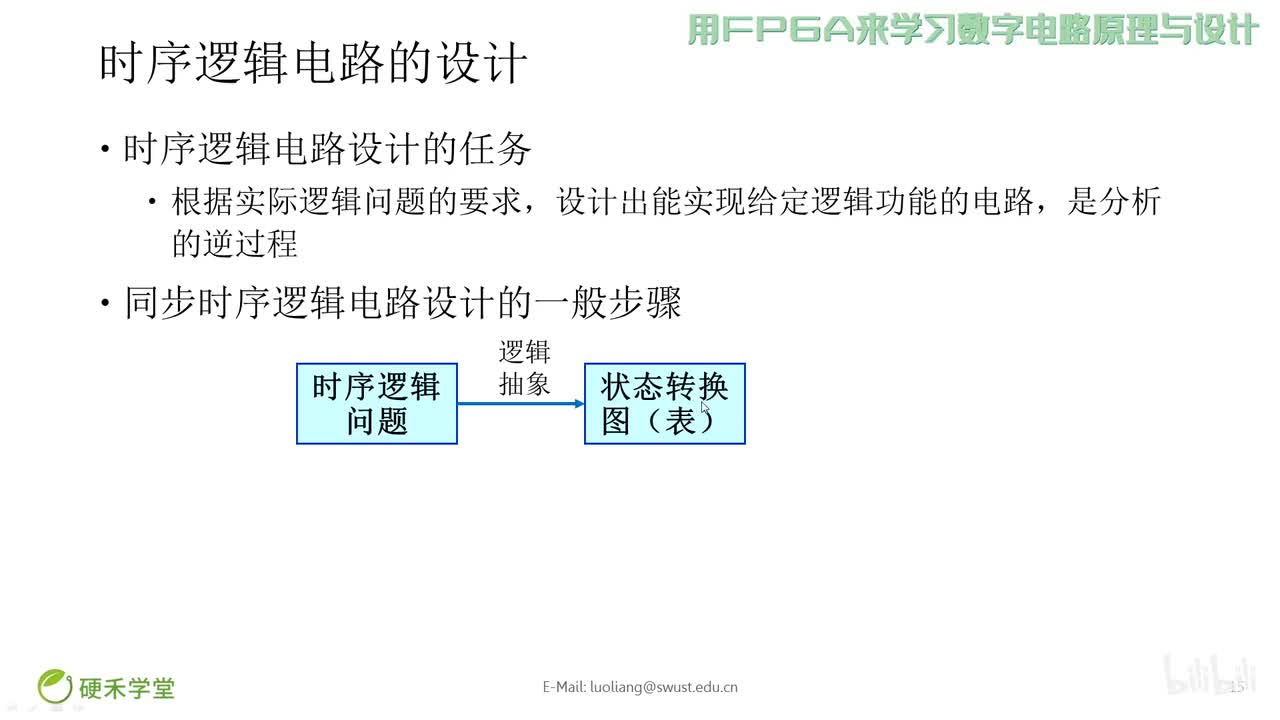

。 圖13 :狀態轉移圖(示例) 簡單時序邏輯電路的設計方法如下:邏輯抽象,得出電路的狀態轉換圖或狀態轉換表。狀態化簡若兩個電路狀態在相同的輸入下有相同的輸出,并且轉換到同樣一個狀態去,則稱這兩個

2023-02-22 17:00:37

地平面是提高性能和防止問題的簡單方法,在我看來,使用普通軌跡進行接地連接的情況很少。 銅是電阻器原理圖有電線,但在現實生活中沒有電線(除非有人開始使用超導體制造PCB ......)。物理互連(包括

2018-07-14 12:31:53

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

設計技巧概論13第2章 可編程邏輯器件設計方法162.1 可編程邏輯器件基礎162.1.1 可編程邏輯器件概述162.1.2 可編程邏輯器件的發展歷史172.2 PLD芯片制造工藝182.3 PLD芯片

2012-04-24 09:18:46

設計dout_vld的時序邏輯改為組合邏輯,將信號dout_vld提前一拍,就可以得到正確的結果。另一種方法,假設dout是組合邏輯設計的,就是把dout改為時序邏輯實現,將dout推遲一拍,達到信號對齊

2020-03-01 19:50:27

時序邏輯電路應用很廣泛,根據所要求的邏輯功能不同進行劃分,它的種類也比較繁多。在具體的授課環節中,主要選取了應用較廣、具有典型時序邏輯電路特征的三種邏輯器件進行比較詳細地介紹 。1.計數器一般來說

2016-10-25 23:03:31

Netlist 引入Post-fit Netlist的過程是從一次成功的時序收斂結果開始,把特定的一組邏輯(Design Partition)在FPGA上實現的布局位置和布線結果(Netlist)固定

2017-10-20 13:26:35

什么是時序邏輯?時序邏輯由哪幾部分構成?

2021-09-17 07:43:37

按部就班的完成各種復雜的任務,也能夠非常便利的達到時序要求,并且能夠解決各種異步處理帶來的亞穩態問題。因此,時序邏輯設計的一些方法和手段是大家必須掌握和熟練應用的。 ```

2017-11-17 18:47:44

。組合邏輯設計代碼: 對應的電路為: 時序邏輯對應代碼為: 對應的電路為: 可以思考一下,這個兩種設計方法都沒有任何錯誤。那么在設計時應該用哪一種呢? 在設計時,有沒有什么規定

2023-03-06 16:31:59

的設計。利用它,還可以導入時序約束并在已布局窗****叉探查(cross-probe)時序失敗的路徑。當工具本身的決策不好時,則可以通過平面布局模塊或通過手工布局部分組件的方式來糾正。這一過程通常需要

2012-12-14 16:04:56

”約束在正確的位置手動布局規劃這些觸發器。這種方法有效,但這樣做至少有兩個缺點: - 需要手動布局規劃幾十個人字拖 - 設計變得不那么便攜,因為我需要確保邏輯和名稱保持不變。我還確保它沒有作為

2018-10-11 14:48:34

手工綜合RTL級代碼的理論依據和實用方法時序邏輯綜合的實現方法

2021-04-08 06:06:35

電路的邏輯功能。時序邏輯電路對于時序邏輯電路,分析電路的最終目的是什么?實際情況往往是:已知時序電路圖,要求找出該電路的功能。時序邏輯電路一般分析方法1、驅動方程:按組合邏輯電路的分析方法,寫出觸發器輸入

2021-11-18 06:30:00

計數器及時序電路原理及實驗 一、實驗目的1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。 &

2009-10-10 11:47:02

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進行工作的?

2021-09-18 09:19:42

靜態時序分析與邏輯設計

2017-12-08 14:49:57

1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI、可編程器件設計時序邏輯電路的特點、方法;3 掌握時序邏輯電路的調試方法;4&

2009-03-18 20:06:31 47

47 時序邏輯電路的輸出不但和當前輸入有關,還與系統的原先狀態有關,即時序電路的當前輸出由輸入變量與電路原先的狀態共同決定。為達到這一目的,時序邏輯電路從某一狀態

2009-03-18 22:13:04 71

71 同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 中規模集成時序邏輯設計:計數器:在數字邏輯系統中,使用最多的時序電路要算計數器了。它是一種對輸入脈沖信號進行計數的時序邏輯部件。9.1.1 計數器的分類1.按數制

2009-09-01 09:09:09 13

13 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 0

0 基于PLD芯片的時序邏輯設計與實現:原理圖輸入設計直觀、便捷、操作靈活;1-1、原理圖設計方法簡介QuartusII已包含了數字電路的基本邏輯元件庫(各類邏輯門及觸發器),宏

2009-10-29 22:03:10 0

0 提出了從狀態轉換圖中直接求得觸發器的置位和復位函數,從而確定觸發器的驅動方程這樣一種設計同步時序邏輯電路的新方法.設計原理簡單,易于理解,適合于所有同步時序

2010-02-28 19:23:02 15

15 摘要:通過實際例子,闡述了次態卡諾圖在分析和設計時序邏輯電路中的使用方法。該方法的使用可以使時序邏輯電路的分析和設計得到一定的簡化,過程中思路清晰,狀態轉換直

2010-04-28 10:03:10 21

21 靜態時序概念,目的

靜態時序分析路徑,方法

靜態時序分析工具及邏輯設計優化

2010-07-09 18:28:18 129

129 數字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 本章首先介紹能夠存儲1 位二值信號的基本單元電路鎖存器和觸發器。著重介紹各種鎖存器和觸發器的電路結構、工作原理、邏輯功能、特性及其描述方法。接著介紹時序邏輯電

2010-08-10 11:55:44 0

0 數字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩定輸出只取決于當前的輸入,而與過去的輸入無關。在結構上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數字電路分為組合邏輯電路(簡稱組合電路)和時序邏輯電路(簡稱時序電路)兩類。在第三章中討論的電路為組合電路。組合電路的結構模型如圖4.1所示,它的輸出函數表達式為

2010-08-13 15:23:02 24

24 在討論時序邏輯電路的分析與設計之前,讓我們先回顧一下在第四章中介紹過的時序電路結構框圖和一些相關術語。時序電路的結構框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 數字集成電路,根據原理可分為兩大類,既組合邏輯電路和時序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態僅由同一時刻的輸入狀態決定,與電路的原

2010-08-18 15:05:23 55

55 一、基本要求1、理解R-S觸發器、J-K觸發器和D觸發器的邏輯功能;2、掌握觸發器構成的時序電路的分析,并了解其設計方法;3、理解計數器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 實驗十六 時序邏輯電路? 實驗(1) 計數器?一、實驗目的?⒈ 熟悉計數器的設計方法及工作原理。?⒉ 了解同步計數器與異步計數器的區別。?⒊ 應用

2008-09-24 22:17:08 3210

3210

第二十二講 同步時序邏輯電路的分析方法

內容提要7.1 概述一、時序電路的定義二、電路構成三、分類:1 同步2 異

2009-03-30 16:26:17 4893

4893

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發器16進制以內7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 3438

3438

時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 8146

8146

時序邏輯電路分析實例

例1 分析圖所示電路的邏輯功能。設起始狀態是

2009-04-07 23:20:25 4398

4398

使用邏輯分析儀調試時序問題

在今天的數字世界,嵌入式系統比以往任何時候都更為復雜。使用速度更快、功耗更低的設備和功能更強大的電路,

2009-08-26 12:09:14 1389

1389

時序邏輯電路的特點

在第三章所討論的組合邏輯電路中,任一時刻的輸出信號僅僅取決于該時刻的輸入信號,而與電路原來

2009-09-30 18:19:22 9900

9900

時序邏輯電路實例解析

一、觸發器 1、電位觸發方式觸發器

2010-04-15 13:46:25 5041

5041 通過介紹Multisim軟件的功能和特點,結合格雷瑪計數器的設計實例,敘述了在Multisim軟件平臺進行時序邏輯電路的設計原理及構成方法,并利用軟件對設計進行仿真。

2012-02-10 16:43:10 133

133 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 主要講了時序邏輯電路的相關知識,能夠方便大家學習使用

2016-02-29 14:25:53 0

0 華為靜態時序分析與邏輯設計,基礎的資料,快來下載吧

2016-09-01 15:44:10 56

56 電子專業單片機相關知識學習教材資料之時序邏輯電路的分析與設計

2016-09-02 14:30:26 0

0 華為BTS邏輯分析時序,感興趣的小伙伴們可以瞧一瞧。

2016-11-15 17:23:09 0

0 一種設計同步時序邏輯電路的新方法

2017-02-07 15:05:00 29

29 作時序和布局約束是實現設計要求的關鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設計只是 FPGA 設計量產準備工作中的一部分。接下來的挑戰是確保設計滿足芯片內的時序和性能要求。為此

2017-11-17 05:23:01 2416

2416

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2017-11-20 12:26:21 8630

8630 時序邏輯電路其任一時刻的輸出不僅取決于該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、寄存器等。由于時序邏輯電路具有存儲或記憶的功能,檢修起來就比較復雜。

2018-04-09 16:00:00 5673

5673

組合邏輯電路和時序邏輯電路都是數字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2018-01-30 17:26:04 91327

91327

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123040

123040

時序邏輯路是數字電路的一種,時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2018-01-30 19:19:25 63961

63961

傳統的基于模擬退火的現場可編程門陣列( FPGA)時序驅動布局算法在時延代價的計算上存在一定誤差,已有的時序優化算法能夠改善布局質量,但增加了時耗。針對上述問題,提出一種基于事務內存( TM)的并行

2018-02-26 10:09:04 0

0 本文開始介紹了時序邏輯電路的特點和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應用舉例。

2018-03-01 10:53:38 106879

106879

本文檔的主要內容詳細介紹的是數字電路教程之時序邏輯電路課件的詳細資料免費下載主要內容包括了:一 概述,二 時序邏輯電路的分析方法,三 若干常用的時序邏輯電路,四 時序邏輯電路的設計方法,五 時序邏輯電路中的競爭冒險現象

2018-12-28 08:00:00 12

12 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 30485

30485 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發器、 寄存器和計數器等。

2019-02-26 15:25:01 49627

49627 將驅動方程代入相應觸發器的特性方程中,便得到該觸發器的次態方程。時序邏輯電路的狀態方程由各觸發器次態的邏輯表達式組成。

2019-02-28 14:06:14 23502

23502 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 7636

7636

靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 掌握時序邏輯電路的設計方法及調試技巧,熟練掌握觸發器的功能及應用,熟練掌握常用MSI時序邏輯芯片的功能及應用

2020-05-20 08:00:00 20

20 本文檔的主要內容詳細介紹的是模擬電路教程之時序邏輯電路的課件資料免費下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設計方法。

2020-06-22 08:00:00 13

13 時序邏輯自動測試生成的PDF文件免費下載包括了:時序邏輯電路 ? 時間幀(Time Frame)擴展法 ? 基于仿真(simulation)方法 ? 測試數據壓縮與解壓縮 ? 商用ATPG工具介紹

2020-12-01 08:00:00 14

14 靜態時序分析是一種重要的邏輯驗證方法,設計者根據靜態時序分

析的結果來修改和優化邏輯,直到設計滿足要求。

2022-11-11 09:42:54 537

537 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2022-12-21 09:18:32 606

606 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-02-12 10:28:36 771

771 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 4816

4816

時序邏輯的代碼一般有兩種: 同步復位的時序邏輯和異步復位的時序邏輯。在同步復位的時序邏輯中復位不是立即有效,而在時鐘上升沿時復位才有效。 其代碼結構如下:

2023-03-21 10:47:07 400

400 組合邏輯最大的缺點就是會存在競爭冒險,使用時序邏輯就可以極大地避免這種問題,從而使系統更加穩定。

2023-05-22 15:30:24 791

791

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 1882

1882

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 2539

2539

電子發燒友網站提供《時序邏輯電路電子課件.ppt》資料免費下載

2023-11-21 14:43:40 0

0 產生相應的輸出信號。本文將詳細介紹時序邏輯電路的分類、基本原理、設計方法以及與組合邏輯電路的區別。 一、時序邏輯電路的分類 時序邏輯電路主要分為三類:鎖存器、觸發器和計數器。 鎖存器(Latch): 鎖存器是一種用于存

2024-02-06 11:18:34 499

499

電子發燒友App

電子發燒友App

評論