CMOS是Complementary Metal-Oxide Semiconductor一詞的縮寫。在業余電子制作中我們經常會用到它,這里系統、詳細的介紹一些CMOS集成電路基礎知識及使用注意事項。

CMOS集成電路的性能及特點

l 功耗低

CMOS集成電路采用場效應管,且都是互補結構,工作時兩個串聯的場效應管總是處于一個管導通,另一個管截止的狀態,電路靜態功耗理論上為零。實際上,由于存在漏電流,CMOS電路尚有微量靜態功耗。單個門電路的功耗典型值僅為20mW,動態功耗(在1MHz工作頻率時)也僅為幾mW。

l 工作電壓范圍寬

CMOS集成電路供電簡單,供電電源體積小,基本上不需穩壓。國產CC4000系列的集成電路,可在3~18V電壓下正常工作。

l 邏輯擺幅大

CMOS集成電路的邏輯高電平“1”、邏輯低電平“0”分別接近于電源高電位VDD及電影低電位VSS。當VDD=15V,VSS=0V時,輸出邏輯擺幅近似15V。因此,CMOS集成電路的電壓電壓利用系數在各類集成電路中指標是較高的。

l 抗干擾能力強

CMOS集成電路的電壓噪聲容限的典型值為電源電壓的45%,保證值為電源電壓的30%。隨著電源電壓的增加,噪聲容限電壓的絕對值將成比例增加。對于VDD=15V的供電電壓(當VSS=0V時),電路將有7V左右的噪聲容限。

l 輸入阻抗高

CMOS集成電路的輸入端一般都是由保護二極管和串聯電阻構成的保護網絡,故比一般場效應管的輸入電阻稍小,但在正常工作電壓范圍內,這些保護二極管均處于反向偏置狀態,直流輸入阻抗取決于這些二極管的泄露電流,通常情況下,等效輸入阻抗高達103~1011Ω,因此CMOS集成電路幾乎不消耗驅動電路的功率。

l 溫度穩定性能好

由于CMOS集成電路的功耗很低,內部發熱量少,而且,CMOS電路線路結構和電氣參數都具有對稱性,在溫度環境發生變化時,某些參數能起到自動補償作用,因而CMOS集成電路的溫度特性非常好。一般陶瓷金屬封裝的電路,工作溫度為-55 ~ +125℃;塑料封裝的電路工作溫度范圍為-45 ~ +85℃。

l 扇出能力強

扇出能力是用電路輸出端所能帶動的輸入端數來表示的。由于CMOS集成電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS集成電路用來驅動同類型,如不考慮速度,一般可以驅動50個以上的輸入端。

l 抗輻射能力強

CMOS集成電路中的基本器件是MOS晶體管,屬于多數載流子導電器件。各種射線、輻射對其導電性能的影響都有限,因而特別適用于制作航天及核實驗設備。

l 可控性好

CMOS集成電路輸出波形的上升和下降時間可以控制,其輸出的上升和下降時間的典型值為電路傳輸延遲時間的125%~140%。

l 接口方便

因為CMOS集成電路的輸入阻抗高和輸出擺幅大,所以易于被其他電路所驅動,也容易驅動其他類型的電路或器件。

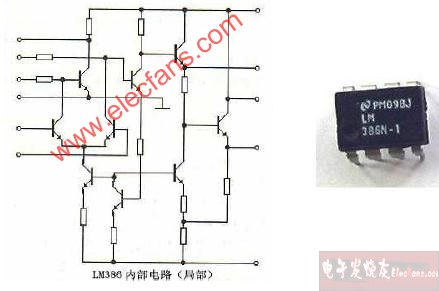

CMOS集成電路的工作原理

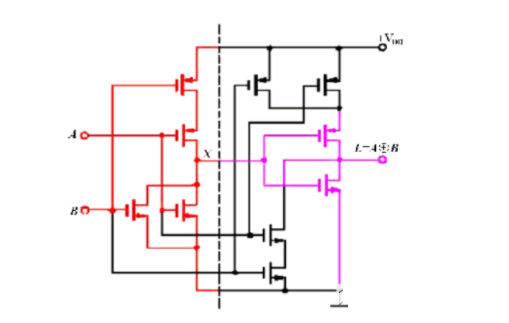

下面我們通過CMOS集成電路中的一個最基本電路-反相器(其他復雜的CMOS集成電路大多是由反相器單元組合而成)入手,分析一下它的工作過程。

利用一個P溝道MOS管和一個N溝道MOS管互補連接就構成了一個最基本的反相器單元電路如附圖所示。圖中VDD為正電源端,VSS為負電源端。電路設計采用正邏輯方法,即邏輯“1”為高電平,邏輯“0”為低電平。

附圖中,當輸入電壓VI為底電平“0”(VSS)時,N溝道MOS管的柵-源電壓VGSN=0V(源極和襯底一起接VSS),由于是增強型管,所以管子截止,而P溝道MOS管的柵-源電壓VGSN=VSS—VDD。若| VSS—VDD |》| VTP|(MOS管開啟電壓),則P溝道MOS管導通,所以輸出電壓V0為高電平“1”(VDD),實現了輸入和輸出的反相功能。

當輸入電壓VI為底電平“1”(VDD)時,VGSN=(VDD—VSS)。若(VDD—VSS)》 VGSN ,則N溝道MOS管導通,此時VGSN=0V, P溝道MOS管截止,所以輸出電壓V0為低電平“0”(VSS),與VI互為反相關系。

由上述分析可知,當輸入信號為“0”或“1”的穩定狀態時,電路中的兩個MOS管總有一個處于截止狀態,使得VDD和VSS之間無低阻抗直流通路,因此靜態功耗極小。這便是CMOS集成電路最主要的特點。

CMOS集成電路應用常識

電路的極限范圍

表1列出了CMOS集成電路的一般參數,表2列出了CMOS集成電路的極限參數。CMOS集成電路在使用過程中是不允許在超過極限的條件下工作的。當電路在超過最大額定值條件下工作時,很容易造成電路損壞,或者使電路不能正常工作。

表1 CMOS集成電路(CC4000系列)的一般參數表

表2 CMOS集成電路(CC4000系列)的極限參數表

應當指出的是:CMOS集成電路雖然允許處于極限條件下工作,但此時對電源設備應采取穩壓措施。這是因為當供電電源開啟或關閉時,電源上脈沖波的幅度很可能超過極限值,會將電路中各MOS晶體管電極之間擊穿。上述現象有時并不呈現電路失效或損壞現象,但有可能縮短電路的使用壽命,或者在芯片內部留下隱患,使電路的性能指標逐漸變劣。

工作電壓、極性及其正確選擇

在使用CMOS集成電路時,工作電壓的極性必須正確無誤,如果顛倒錯位,在電路的正負電源引出端或其他有關功能端上,只要出現大于0.5V的反極性電壓,就會造成電路的永久失效。

雖然CMOS集成電路的工作電壓范圍很寬,如CC4000系列電路在3~18V的電源電壓范圍內都能正常工作,當使用時應充分考慮以下幾點:

1. 輸出電壓幅度的考慮。

電路工作時,所選取的電源工作電壓高低與電路輸出電壓幅度大小密切相關。由于CMOS集成電路輸出電壓幅度接近于電路的工作電壓值,因此供給電路的正負工作電壓范圍可略大于電路要求輸出的電壓幅度。

2. 電路工作速度的考慮。

CMOS集成電路的工作電壓選擇,直接影響電路的工作速度。對CMOS集成電路提出的工作速度或工作頻率指標要求往往是選擇電路工作電壓的因素。如果降低CMOS集成電路的工作電壓,必將降低電路的速度或頻率指標。

3. 輸入信號大小的考慮。

工作電壓將限制CMOS集成電路的輸入信號的擺幅,對于CMOS集成電路來說,除非對流經電路輸入端保護二極管的電流施加限流控制,輸入電路的信號擺幅一般不能超過供給電壓范圍,否則將會導致電路的損壞。

4. 電路功耗的限制。

CMOS集成電路所選取的工作電壓愈高,則功耗就愈大。但由于CMOS集成電路功耗極小,所以在系統設計中,功耗并不是主要考慮的設計指標。

輸入和輸出端使用規則

1. 輸入端的保護方法。

在CMOS集成電路的使用中,要求輸入信號幅度不能超過VDD—VSS。輸入信號電流絕對值應小于10mA。如果輸入端接有較大的電容C時,應加保護電阻R,如附圖3所示。R的阻值約為幾十歐姆至幾十千歐姆。

2. 多余輸入端的處置。

CMOS集成電路多余輸入端的處置比較簡單,下面以或門及與門為例進行說明。如附圖4所示,或門(或非門)的多余輸入端應接至VSS端;與門(與非門)的多余輸入端應接至VDD端。當電源穩定性差或外界干擾較大時,多余輸入端一般不直接與電源(地)相連,而是通過一個電阻再與電源(地)相連,如圖5所示,R的阻值約為幾百千歐姆。

另外,采用輸入端并聯的方法來處理多余的輸入端也是可行的。但這種方法只能在電路工作速度不高,功耗不大的情況下使用。

3. 多余門的處置。

CMOS集成電路在一般使用中,可將多余門的輸入端接VDD或VSS,而輸出端可懸空不管。當用CMOS集成電路來驅動較大輸入電流的元器件時,可將多余門按邏輯功能并聯使用。

4. 輸出端的使用方法。

在高速數字系統中,負載的輸入電容將直接影響信號的傳輸速度,在這種情況下,CMOS集成電路的扇出系數一般取為10~20。此時,如果輸出能力不足,通常的解決方法是選用驅動能力較強的緩沖器(如四同相/反相緩沖器CC4041),以增強輸出端吸收電流的能力。

寄生可控硅效應的防護措施

由于CMOS集成電路的互補特點,造成了在電路內部有一個寄生的可控硅(VS)效應。

當CMOS集成電路受到某種意外因素激發,如電感、電火花,在電源上引起的噪聲往往要超過CMOS集成電路的擊穿電壓(約25V)。這時,集成電路的VDD端和VSS端之間會出現一種低阻狀態,電源電壓突然降低,電流突然增加,如果電源沒有限流措施,就會把電路內部連接VDD或VSS的鋁線燒斷,造成電路永久性損壞。

如果電源有一定的限流措施(例如電源電流限在250mA以內),在出現大電流、低電壓狀態時,及時關斷電源,就能保證電路安全無損。重新打開電源,電路仍能正常工作。

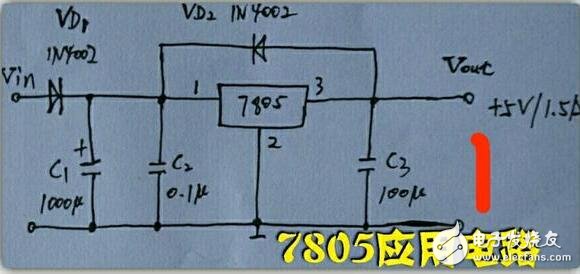

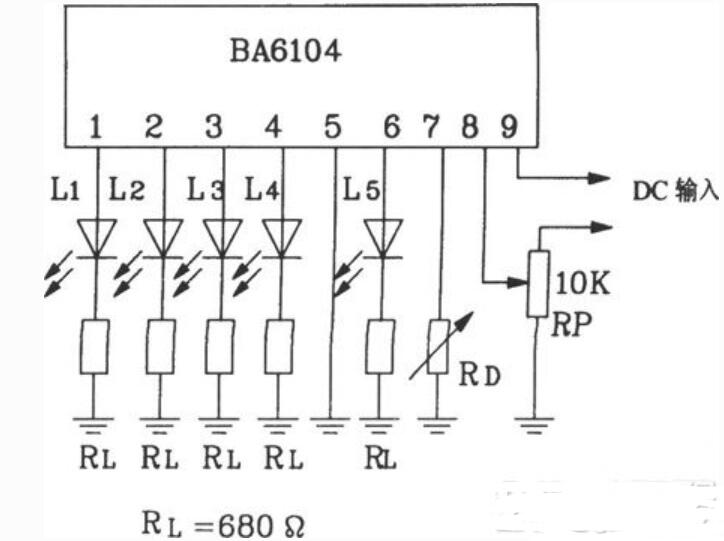

簡單的限流方法是用電阻和穩壓管進行限流,如附圖1所示。圖中穩壓管的擊穿電壓就是CMOS集成電路的工作電壓,電阻用來限流,電容用來提供電路翻轉時所需的瞬態電流。

寄生VS造成損壞的電路用萬用表電阻擋就可判斷。正常電路,VDD—VSS之間有二極管特性:VS燒毀的電路,VDD~VSS之間呈開路狀態。

在系統中,被損壞的電路如果加交流信號,其輸出電平范圍很窄,既高電平不到VDD,低電平不到VSS,而且不能驅動負載。

正常的CMOS集成電路用JT-1晶體管特性測試儀測量,能得到如圖2所示的擊穿特性曲線。測試方法:VDD接正電源,VSS接地,所有的輸入端接VDD或VSS,測量集成電路的擊穿特性。

下一節將討論——CMOS集成電路基礎知識(二):CMOS集成電路的接口電路,敬請留意。

電子發燒友App

電子發燒友App

評論