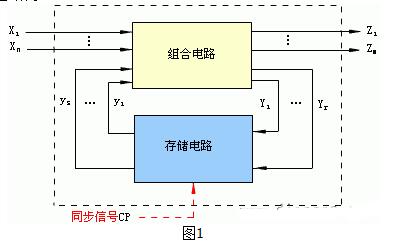

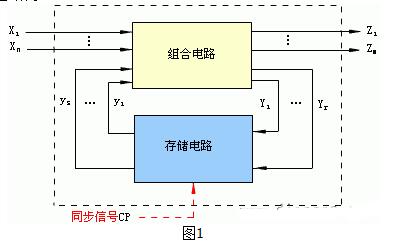

在數字電路中,凡是任一時刻的穩定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態有關者都叫時序邏輯電路。時序邏輯電路結構示意圖如圖2-41所示。時序邏輯電路的狀態是靠具有存儲功能的觸發器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

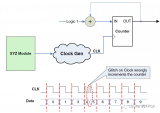

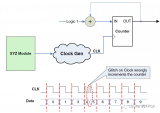

表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 2767

2767

描述 本設計咨詢主要介紹一個錯誤的時鐘偏移計算導致錯誤時序收斂的問題。 出現問題的情況: 這可能會影響使用生成時鐘的設計,其具有以下特征: 使用 Vivado 2018.2.x 及更早版本。 用戶

2020-12-24 11:16:24 5086

5086 了解嗎? (1)純組合邏輯電路的缺點在哪? (3)純組合邏輯電路完成不了什么功能? (2)為什么需要時鐘和寄存器呢? 帶著這三個疑問我們來認識一下時序邏輯電路。 二. 同步時序邏輯電路的作用 1. 時序邏輯電路對于組合邏輯的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

數字電路根據邏輯功能的不同特點,可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另一類叫做時序邏輯電路,簡稱時序電路或時序邏輯。

2022-12-01 09:04:04 459

459 時序邏輯電路的精華——計數器

2022-12-29 09:23:56 1010

1010 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-01-13 13:57:47 1830

1830

數字邏輯電路分為組合邏輯電路和時序邏輯電路。時序邏輯電路是由組合邏輯電路和時序邏輯器件構成(觸發器),即數字邏輯電路是由組合邏輯和時序邏輯器件構成。

2023-03-21 09:49:49 476

476 在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

1230 FPGA設計中的絕大部分電路為同步時序電路,其基本模型為“寄存器+組合邏輯+寄存器”。同步意味著時序路徑上的所有寄存器在時鐘信號的驅動下步調一致地運作。

2023-08-03 09:27:25 915

915

芯片設計是現代電子設備的重要組成部分,其中組合邏輯和時序邏輯是芯片設計中非常重要的概念。組合邏輯和時序邏輯的設計對于構建復雜的電路系統至關重要。

2023-08-30 09:32:15 809

809 組合邏輯產生的時鐘可能有毛刺,會被錯誤地當成有效時鐘邊沿,在設計中會導致功能錯誤。因此,不要使用組合邏輯的輸出作為時鐘。

2024-01-22 09:30:50 168

168

時序邏輯電路的特點

2019-10-08 05:34:53

時序邏輯電路的設計實驗1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

。同步的數字系統正是由許多的寄存器,以及寄存器中間的組合邏輯構成的(也包括寄存器間的直接連接)。顯然,如果要數字系統正常工作,每個寄存器的建立時間和保持時間都必須得到滿足。假設時鐘信號ck到達所有寄存器

2020-08-16 07:25:02

進去, 1080p出來的時候,視頻正常 播放出來。 可是當 1080p進, 4k出來的時候,視頻圖像上會有水波紋。當時就猜想是 FPGA 送給 下游器件SII9136的 時序不能滿足。于是把輸出的時鐘

2016-11-15 18:15:03

,但問題是,最后數組63相乘這一步就是沒有實現,我看網上說是時序邏輯會延后一個時鐘周期導致最后一步沒有加上,我試著將程序中timer==7‘d63改為timer==7‘d64,最后一個就加上了,但這樣的話,新的問題又來了,我希望64個周期算完的,卻要65個周期,這要什么方法解決這個問題?

2017-09-13 11:02:51

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

寄存器的代碼編寫。接下來我們要更進一步從深沉次來探討基于寄存器的同步以及時鐘的設計原則。(特權同學,版權所有)雖然在上一章已經對組合邏輯和時序邏輯的基本概念做過描述,但是這里還是要再額外嘮叨幾句組合邏輯

2015-06-29 09:31:03

基本時序路徑本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 對于FPGA內部而言,通常有四大類的基本時序

2015-07-20 14:52:19

VGA驅動接口時序設計之3時鐘約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 如圖8.26所示

2015-07-30 22:07:42

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

的不同,我們可以從三方面來理解,分別是code(代碼),電路圖和波形圖三方面。 從代碼層面來看,時序邏輯即敏感列表里面帶有時鐘上升沿,如果是沒有上升沿或者是帶有“*”號的代碼,為組合邏輯。電路層面,兩種

2020-03-01 19:50:27

什么是時序邏輯?時序邏輯由哪幾部分構成?

2021-09-17 07:43:37

時序邏輯電路的特點:各觸發器的時鐘端全部連接在一起,并接在系統時鐘端,只有當時鐘脈沖到來時,電路的狀態才能改變。改變后的狀態將一直保持到下一個時鐘脈沖的到來,此時無論外部輸入 x 有無變化,狀態表...

2021-11-11 06:13:35

本文來自芯社區,謝謝。1:什么是同步邏輯和異步邏輯? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 同步時序邏輯電路的特點:各觸發器的時鐘端全部連接在一起,并接在系統

2021-07-26 08:26:57

的延時。而在時序邏輯中,該實例除了組合邏輯滿足條件外,只有在時鐘信號clk的每個上升沿輸出z2才會發生變化。這里有一個細節大家也需要注意,x和y的組合邏輯輸出值在時鐘上升沿到來的前后的某段時間內(即建立

2017-11-17 18:47:44

。組合邏輯設計代碼: 對應的電路為: 時序邏輯對應代碼為: 對應的電路為: 可以思考一下,這個兩種設計方法都沒有任何錯誤。那么在設計時應該用哪一種呢? 在設計時,有沒有什么規定

2023-03-06 16:31:59

涉及時序邏輯電路的實例,希望能夠幫助大家理解在FPGA中實現時序邏輯電路。與組合邏輯電路相比,時序邏輯電路需要時鐘的參與,電路中會有存儲器件的參與,時序邏輯電路的輸出不僅取決于這一時刻的輸入,也受此

2022-07-22 15:25:03

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進行工作的?

2021-09-18 09:19:42

靜態時序分析與邏輯設計

2017-12-08 14:49:57

1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI、可編程器件設計時序邏輯電路的特點、方法;3 掌握時序邏輯電路的調試方法;4&

2009-03-18 20:06:31 47

47 時序邏輯電路的輸出不但和當前輸入有關,還與系統的原先狀態有關,即時序電路的當前輸出由輸入變量與電路原先的狀態共同決定。為達到這一目的,時序邏輯電路從某一狀態

2009-03-18 22:13:04 71

71 同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 中規模集成時序邏輯設計:計數器:在數字邏輯系統中,使用最多的時序電路要算計數器了。它是一種對輸入脈沖信號進行計數的時序邏輯部件。9.1.1 計數器的分類1.按數制

2009-09-01 09:09:09 13

13 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 0

0 基于PLD芯片的時序邏輯設計與實現:原理圖輸入設計直觀、便捷、操作靈活;1-1、原理圖設計方法簡介QuartusII已包含了數字電路的基本邏輯元件庫(各類邏輯門及觸發器),宏

2009-10-29 22:03:10 0

0 摘要:通過實際例子,闡述了次態卡諾圖在分析和設計時序邏輯電路中的使用方法。該方法的使用可以使時序邏輯電路的分析和設計得到一定的簡化,過程中思路清晰,狀態轉換直

2010-04-28 10:03:10 21

21 靜態時序概念,目的

靜態時序分析路徑,方法

靜態時序分析工具及邏輯設計優化

2010-07-09 18:28:18 129

129 數字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

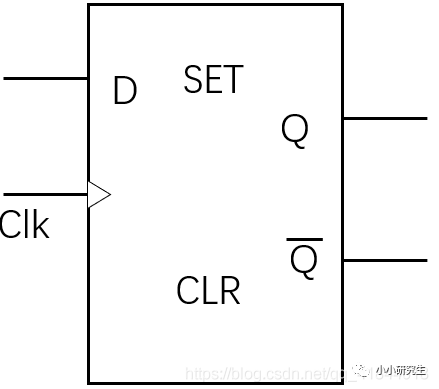

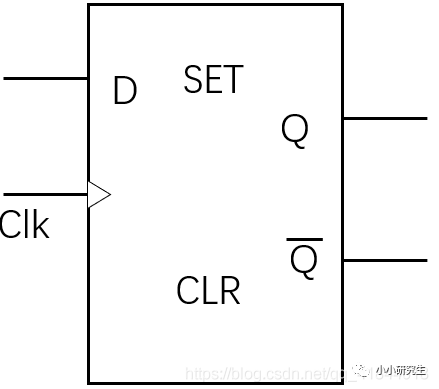

39 本章首先介紹能夠存儲1 位二值信號的基本單元電路鎖存器和觸發器。著重介紹各種鎖存器和觸發器的電路結構、工作原理、邏輯功能、特性及其描述方法。接著介紹時序邏輯電

2010-08-10 11:55:44 0

0 數字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩定輸出只取決于當前的輸入,而與過去的輸入無關。在結構上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數字電路分為組合邏輯電路(簡稱組合電路)和時序邏輯電路(簡稱時序電路)兩類。在第三章中討論的電路為組合電路。組合電路的結構模型如圖4.1所示,它的輸出函數表達式為

2010-08-13 15:23:02 24

24 在討論時序邏輯電路的分析與設計之前,讓我們先回顧一下在第四章中介紹過的時序電路結構框圖和一些相關術語。時序電路的結構框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 數字集成電路,根據原理可分為兩大類,既組合邏輯電路和時序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態僅由同一時刻的輸入狀態決定,與電路的原

2010-08-18 15:05:23 55

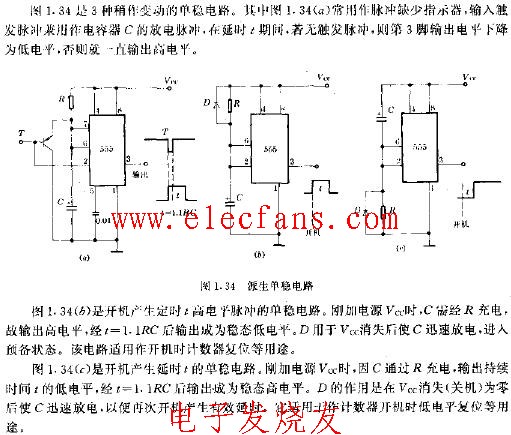

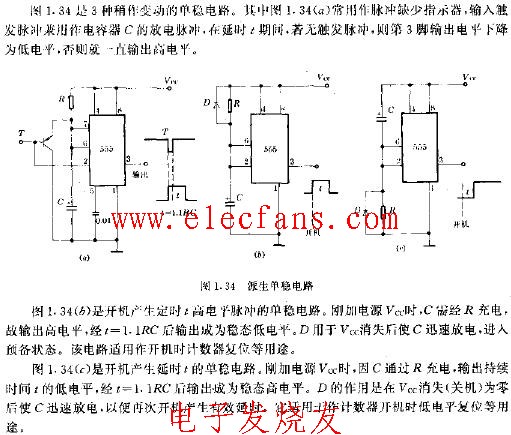

55 派生單穩電路

2008-05-19 23:06:06 775

775

實驗十六 時序邏輯電路? 實驗(1) 計數器?一、實驗目的?⒈ 熟悉計數器的設計方法及工作原理。?⒉ 了解同步計數器與異步計數器的區別。?⒊ 應用

2008-09-24 22:17:08 3210

3210

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發器16進制以內7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 3438

3438

時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 8146

8146

時序邏輯電路分析實例

例1 分析圖所示電路的邏輯功能。設起始狀態是

2009-04-07 23:20:25 4398

4398

使用邏輯分析儀調試時序問題

在今天的數字世界,嵌入式系統比以往任何時候都更為復雜。使用速度更快、功耗更低的設備和功能更強大的電路,

2009-08-26 12:09:14 1389

1389

時序邏輯電路的特點

在第三章所討論的組合邏輯電路中,任一時刻的輸出信號僅僅取決于該時刻的輸入信號,而與電路原來

2009-09-30 18:19:22 9900

9900

時序邏輯電路實例解析

一、觸發器 1、電位觸發方式觸發器

2010-04-15 13:46:25 5041

5041 定義了時鐘單位階躍信號C(n) 提出了一種利用帶相對時鐘坐標的邏輯方程表示邏輯信號的方法通過對所設計的DDR SDRAM控制器的讀寫時序的分析建立了控制器主要信號的時序表達式并利用

2011-09-26 15:34:12 39

39 c++面向對象課程實驗指導書題目_繼承與派生。

2016-01-14 16:25:42 0

0 主要講了時序邏輯電路的相關知識,能夠方便大家學習使用

2016-02-29 14:25:53 0

0 華為靜態時序分析與邏輯設計,基礎的資料,快來下載吧

2016-09-01 15:44:10 56

56 電子專業單片機相關知識學習教材資料之時序邏輯電路的分析與設計

2016-09-02 14:30:26 0

0 華為BTS邏輯分析時序,感興趣的小伙伴們可以瞧一瞧。

2016-11-15 17:23:09 0

0 在傳統設計中,所有計算機運算(算法邏輯和存儲進程) 都參考時鐘同步執行,時鐘增加了設計中的時序電路數量。在這個電池供電設備大行其道的移動時代,為了節省每一毫瓦(mW) 的功耗,廠商間展開了殘酷的競爭

2017-10-25 15:41:59 25

25 在傳統設計中,所有計算機運算(算法、邏輯和存儲進程)都參考時鐘同步執行,時鐘增加了設計中的時序電路數量。在這個電池供電設備大行其道的移動時代,為了節省每一毫瓦(mW)的功耗,廠商間展開了殘酷的競爭

2017-11-15 15:40:13 12

12 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2017-11-20 12:26:21 8630

8630 時序邏輯電路其任一時刻的輸出不僅取決于該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、寄存器等。由于時序邏輯電路具有存儲或記憶的功能,檢修起來就比較復雜。

2018-04-09 16:00:00 5673

5673

組合邏輯電路和時序邏輯電路都是數字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2018-01-30 17:26:04 91327

91327

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123040

123040

時序邏輯路是數字電路的一種,時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2018-01-30 19:19:25 63961

63961

本文開始介紹了時序邏輯電路的特點和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應用舉例。

2018-03-01 10:53:38 106879

106879

域帶來的亞穩態、采樣丟失、潛在邏輯錯誤等等一系列問題處理不當,將導致系統無法運行。本文總結出了幾種同步策略來解決跨時鐘域問題。

2018-09-01 08:29:21 5302

5302

時序邏輯電路對于組合邏輯的毛刺具有容忍度,從而改善電路的時序特性。同時電路的更新由時鐘控制。

2018-11-24 11:17:51 3197

3197

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 30485

30485 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發器、 寄存器和計數器等。

2019-02-26 15:25:01 49627

49627 將驅動方程代入相應觸發器的特性方程中,便得到該觸發器的次態方程。時序邏輯電路的狀態方程由各觸發器次態的邏輯表達式組成。

2019-02-28 14:06:14 23502

23502 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 7636

7636

靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 掌握時序邏輯電路的設計方法及調試技巧,熟練掌握觸發器的功能及應用,熟練掌握常用MSI時序邏輯芯片的功能及應用

2020-05-20 08:00:00 20

20 本文檔的主要內容詳細介紹的是模擬電路教程之時序邏輯電路的課件資料免費下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設計方法。

2020-06-22 08:00:00 13

13 組合邏輯生成的時鐘,在FPGA設計中應該避免,尤其是該時鐘扇出很大或者時鐘頻率較高,即便是該時鐘通過BUFG進入全局時鐘網絡。

2020-10-10 10:28:32 3639

3639

本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 口靜態時序工具可識別的時廳敵障數要比仿真多得多,包括:建立/保持和恢復移除檢査(包括反向建立保持):最小和最大跳變:時鐘脈泩寬度和時鐘畸變;門級時鐘的瞬旴脒沙檢測;總線競爭與總線懸浮錯誤;不受

2021-01-14 16:04:03 9

9 文章目錄高溫下STM32采用內部晶振作為系統時鐘的時鐘源導致時序紊亂問題高溫導致時鐘紊亂問題引出時鐘紊亂問題總結高溫下STM32采用內部晶振作為系統時鐘的時鐘源導致時序紊亂問題單片機的時序問題在整個

2021-12-14 18:58:22 5

5 如例6.1所述,在多個“Always” 進程中使用阻塞賦值。程序塊“Always”在時鐘的正邊緣觸發,綜合器推斷時序邏輯。如前所述,所有阻塞賦值都在活動隊列中進行計算和更新。讀者請參閱之前分享的分層事件隊列一文。

2022-09-06 09:44:02 3306

3306 時鐘信號在很大程度上決定了整個設計的性能和可靠性,盡量避免使用FPGA內部邏輯產生的時鐘,因為它很容易導致功能或時序出現問題。內部邏輯(組合邏輯)產生的時鐘容易出現毛刺,影響設計的功能實現;組合邏輯固有的延時也容易導致時序問題。

2022-10-26 09:04:51 823

823 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-02-12 10:28:36 771

771 使用always_ff和在靈敏度列表中指定一個時鐘邊沿并不意味著過程中的所有邏輯都是時序邏輯。綜合編譯器將推斷出每個被非阻塞賦值的變量的觸發器。阻塞賦值也可能推斷出觸發器,這取決于賦值語句相對于程序中其他賦值和操作的順序和上下文。

2023-02-20 10:38:06 442

442 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 4816

4816

? ? 1、時序錯誤的影響 ? ? ? 一個設計的時序報告中,design run 時序有紅色,裕量(slack)為負數時,表示時序約束出現違例,雖然個別違例不代表你的工程就有致命的問題,但是這是

2023-03-17 03:25:03 426

426 時序邏輯的代碼一般有兩種: 同步復位的時序邏輯和異步復位的時序邏輯。在同步復位的時序邏輯中復位不是立即有效,而在時鐘上升沿時復位才有效。 其代碼結構如下:

2023-03-21 10:47:07 400

400 組合邏輯最大的缺點就是會存在競爭冒險,使用時序邏輯就可以極大地避免這種問題,從而使系統更加穩定。

2023-05-22 15:30:24 791

791

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 1882

1882

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 2539

2539

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過? 異步FIFO中讀地址同步在寫時鐘域時序分析不通過的原因可能有以下幾個方面: 1. 讀地址同步在寫時鐘域時序分析未覆蓋完全 在時序分析時,可能

2023-10-18 15:23:55 312

312 時序邏輯電路 一 : 觸發器 1:D 觸發器 : 時序邏輯電路最小單元 。 (1):D 觸發器工作原理 忽略清零端情況下 : 當使能條件 ( 往往為時鐘的觸發沿 : 上升沿 / 下降沿 ) 滿足

2023-11-02 12:00:01 308

308

電子發燒友網站提供《完美時序-時鐘產生和分發設計指南.pdf》資料免費下載

2023-11-18 10:27:02 0

0 電子發燒友網站提供《時序邏輯電路電子課件.ppt》資料免費下載

2023-11-21 14:43:40 0

0 時序邏輯電路是一種能夠存儲信息并根據時鐘信號按照特定順序執行操作的電路。它是計算機硬件中非常重要的一部分,用于實現存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據輸入信號的組合情況,立即

2024-02-06 11:18:34 499

499 成部分之一。 寄存器屬于時序邏輯電路。時序邏輯電路是指其輸出狀態不僅依賴于當前的輸入,還依賴于過去的輸入和時鐘信號的變化。在寄存器中,時鐘信號用來控制數據的輸入和輸出,確保在時鐘上升沿或下降沿時,數據能夠穩定地從輸入

2024-02-18 09:37:20 249

249 本文將介紹一個跨時鐘錯誤的案例如圖所示,phy_status作為一個多bit的phy_clk時鐘域的信號,需要輸入csr模塊作為一個可讀狀態寄存器

2024-03-11 15:56:48 152

152

電子發燒友App

電子發燒友App

評論