Cadence設計系統公司(Cadence Design Systems, Inc.)(納斯達克代碼:CDNS)今日宣布與TSMC簽訂了一項長期合作協議,共同開發16納米FinFET技術,以其適用于

2013-04-09 11:00:05 798

798 為簡化和加速復雜IC的開發,Cadence 設計系統公司 (NASDAQ:CDNS) 今天推出Tempus? 時序簽收解決方案。這是一款新的靜態時序分析與收斂工具,旨在幫助系統級芯片 (SoC) 開發者加速時序收斂,將芯片設計快速轉化為可制造的產品。

2013-05-21 15:37:37 2929

2929 Cadence益華電腦總裁兼執行長陳立武表示:“在當今復雜SoC上達成設計收斂還要滿足上市時間要求,堪稱為一項艱巨的挑戰。我們開發了Tempus時序signoff分析,與客戶和生態系伙伴們并肩合作,克服這個挑戰。”

2013-05-27 09:09:49 2038

2038 Cadence系統芯片開發工具已經通過臺積電(TSMC) 16納米 FinFET制程的設計參考手冊第0.1版與 SPICE 模型工具認證,客戶現在可以享用Cadence益華電腦流程為先進制程所提供的速度、功耗與面積優勢。

2013-06-06 09:26:45 1236

1236 進入20納米節點后,FPGA廠商除了比拼先進制程技術外,亦開始推出全新的設計架構及開發工具,助力客戶突破20納米以下FPGA產品將遇到的設計瓶頸,讓FPGA市場競爭戰況愈來愈激烈。

2014-01-29 11:59:02 1130

1130 解決方案的基礎,通過集成的散熱、功率消耗和靜態時序分析功能,為客戶提供系統驅動的功率、性能和面積 (PPA),用于單個小芯片。 Cadence? Integrity? 3D-IC 平臺是業界首個綜合性

2021-10-14 11:19:57

Cadence工具VirtusoDracula入門介紹Cadence工具Virtuso/Dracula入門介紹.... 21.使用 Virtuso/Diva/Dracula之前的準備

2012-08-10 18:39:06

板設計。Cadence 在仿真、電路圖設計、自動布局布線、版圖設計及驗證等方面有著絕對的優勢。Cadence 包含的工具較多幾乎包括了EDA 設計的方方面面。對于初學者來說,cadence的步驟確實

2019-01-22 15:47:53

在使用cadence設計原理圖時,有時會出現一些連線錯誤,如單網絡,信號互連錯誤等等,業界有沒有專業的針對cadence的檢查工具,能夠設置一些條件,將錯誤檢查出來,如有這方面的信息,請提供以下,謝謝!!

2015-02-09 15:58:47

中興的cadence工具培訓使用教程,絕對好東西。

2016-04-06 13:45:34

臺積電0.18工藝電源電壓分別是多少?是1.8v跟3.3v嗎?

2021-06-25 06:32:37

臺積電宣布5nm基本完工開始試產:面積縮小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

有機會“獨吞”A7代工訂單。 臺積電作為全球規模最大的專業集成電路制造公司,其技術優勢的領先,在業界可謂屈指可數。臺積電積極開發20納米制程,花旗環球證券指出,在技術領先MAX3232EUE+T優勢下,未來1

2012-09-27 16:48:11

臺積電正在大量生產用于蘋果iPhone8手機的10nm A11處理器。消息稱,蘋果可能在下個月初正式發布iPhone 8,但是具體發貨日期仍然不確定。 據悉,臺積電已經采用10nm FinFET

2017-08-17 11:05:18

納米定位臺外殼是特殊鋼材嗎,市場價格怎樣?

2015-12-23 07:57:06

關于納米級電接觸電阻測量的新技術看完你就懂了

2021-04-09 06:43:22

,還有一些其他的納米級測量儀器也日益成為研究的熱點,例如激光干涉儀。這些測量工具各有特點,可用于不同的納米級尺寸測量需求。

納米級測量儀器在納米科技研究領域中扮演著重要的角色。通過共聚焦顯微鏡、光學輪廓儀等的運用,科研人員們能夠更加深入地了解納米世界的奧秘。

2023-10-11 14:37:46

`只用一根納米管,便可實現部件眾多的普通收音機的所有功能。由于納米管極其微小,因而它一遇到無線電信號便會快速振動。把這根納米天線與外圍電路接通,我們便可以操縱它完成選臺、放大,將音頻成分同無線電波的其他成分分離開來(解調)`

2020-03-18 11:33:07

ESP32 是集成 2.4 GHz Wi-Fi 和藍牙雙模的單芯片方案,采用臺積電 (TSMC) 低功耗 40 納米工藝,具有超高的射頻性能、穩定性、通用性和可靠性,以及超低的功耗,滿足不同的功耗需求,適用于各種應用場景。

2023-09-18 09:03:17

退出7納米研發,令業界十分震驚。自GF 退出戰局后,全球7納米大戰的芯片大廠僅剩英特爾、臺積電和三星這三家,高端芯片戰場上呈現三國鼎立之勢。全球第二大芯片廠 GF何故離場?GF是全球第二大芯片代工廠

2018-09-05 14:38:53

%。西安二廠預計將生產13.5萬片,比之前的14.5萬片減少了約7%。業界觀察人士認為,三星選擇砍掉部分NAND產能,因為當前內存市場形勢慘淡。

【臺積電28nm設備訂單全部取消!】

4月消息,由于

2023-05-10 10:54:09

仿真,提供業界一流的晶體管級精度,以滿足在先進制程上復雜的生產工藝要求,它補充了Cadence Voltus IC電源完整性解決方案中全芯片、模塊級電源簽收工具,完善了公司電源簽收的技術方案

2018-09-30 16:11:32

應用處理器代工市場已是毫無敵手,可望直取英特爾SoFIA、蘋果A9大單。 臺積電今年全力沖刺20納米系統單芯片制程(20SoC)產能,由于已搶下蘋果A8處理器及高通、英特爾、NVIDIA等大單,不僅第

2014-05-07 15:30:16

,未來就要看競爭對手的制程技術能否趕得上腳步。 近期高通與臺積電持續緊密合作,業界傳出在最先進的7納米制程技術上,臺積電因為技術開發領先三星電子(Samsung Electronics),可望拿回高通7

2017-09-22 11:11:12

據外媒報道,預計臺積電將獲得高通新一代電源管理芯片(PWM IC)70%至80%的訂單。高通前一代電源管理芯片是由中芯國際(SMIC)生產的,后者在其8英寸晶圓廠使用0.18至0.153微米工藝來生

2017-09-27 09:13:24

;nbsp; 很多人會回答:我想當高級主管,進臺積聯電賺股票。因為我崇拜張忠謀、曹興誠。以下是我就業三年以來,對***電子信息產業的一些看法: &

2009-08-23 11:28:40

各類常用工藝庫臺積電,中芯國際,華潤上華

2015-12-17 19:52:34

納米制程功耗低性能強國民做安全芯片起家,自帶多種加密算法安全性高與臺積電簽訂多份采購訂單,供貨較為穩定MCU產品已得到多家行業龍頭客戶認可并導入(華為、大疆、寧德時代)寬產品線、覆蓋32位MCU從低端到高端的絕大多數應用場景國民技術MCU表示Pin數與flash容量的字母后綴與ST、GD對應含義

2021-11-01 07:51:48

90/65nm下后端設計中由于多模式-角落,以及布局布線工具和簽收工具之間的誤差性,布線后修復各種時序違規如渡越時間、負載、建立時間、保持時間、串擾等將是一項十分耗時的工作。如何快速修復各種違規

2010-05-28 13:41:58

本帖最后由 華強芯城 于 2023-3-17 09:16 編輯

晶圓代工巨頭——臺積電近日傳出漲價20%的消息,業內轟動。這是臺積電繼2020年底上漲超10%之后,一年之內,又一次的大幅上漲

2021-09-02 09:44:44

模擬時序控制器IC。它能控制和監視四個電壓域。電壓的上電和關斷是通過控制相應電壓轉換器上的使能(開/關)引腳進行的。電壓轉換器的開啟時間可以利用小電容產生的時間延遲來調整。各輸出電壓通過相應的監控引腳

2021-04-12 07:00:00

求介紹納米定位臺是怎么運行的?、

2013-06-21 15:21:53

這些年,英特爾、三星、臺積電在制程上的恩恩怨怨,堪比武俠小說中恩怨情仇。這些大廠的爭斗均是圍繞14納米和16納米,那么問題來了,這個14納米和16納米有什么好爭的?下面芯易網就來簡單做一下介紹。納米

2016-12-16 18:20:11

這些年,英特爾、三星、臺積電在制程上的恩恩怨怨,堪比武俠小說中恩怨情仇。這些大廠的爭斗均是圍繞14納米和16納米,那么問題來了,這個14納米和16納米有什么好爭的?下面芯易網就來簡單做一下介紹。納米

2016-06-29 14:49:15

10nm將會流片,而張忠謀更是信心十足,他直言不諱地表示10nm量產后將會搶下更高的份額。臺積電聯席CEO劉德音此前也曾在一次投資人會議上透露,公司計劃首先讓自己的10納米芯片產線在今年底前全面展開

2016-01-25 09:38:11

請問一下cadence工具好用還是synopsys工具好用?

2021-06-23 06:34:29

Cadence高速PCB的時序分析:列位看觀,在上一次的連載中,我們介紹了什么是時序電路,時序分析的兩種分類(同步和異步),并講述了一些關于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 cadence 視頻教程 (第20課):adence SPB 15.7 視頻教程,手把手教你學習cadence軟件使用方法。本套視頻教程是于博士信號完整性研究網于爭博士主講。從一個工程師的角度出發講解軟件的操

2009-09-16 19:15:39 0

0 時序計算和Cadence 仿真結果的運用中興通訊康訊研究所 EDA 設計部 余昌盛 劉忠亮摘要:本文通過對源同步時序公式的推導,結合對SPECCTRAQuest 時序仿真方法的分析,推導出了使

2009-12-21 09:05:39 172

172 Cadence 高速 PCB 的時序分析 1.引言 時序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發了一封 e-mail,希望能夠得到一份時序分析的案

2010-04-05 06:37:13 0

0 中芯國際采用Cadence DFM解決方案用于65和45納米 IP/庫開發和全芯片生產

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設計低功耗尖端器件成為可能

2009-10-31 07:48:01 1228

1228 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設計創新領先企業Cadence設計系統公司今天宣布推出一款全面的低功耗設計流程,面向

2009-11-04 17:05:17 589

589 三星電子有限公司使用Cadence統一數字流程,從RTL到GDSII,成功實現了20納米測試芯片的流片

2011-07-27 08:47:49 967

967 格羅方德半導體(GLOBALFOUNDRIES )日前宣布了該公司推進尖端20納米的制造工藝走向市場的一項重大的進展。羅格方德半導體利用電子設計自動化(EDA)的先進廠商如Cadence Design Systems、Magma De

2011-09-20 08:49:00 711

711 根據源同步的一些基本問題,在Cadence仿真環境下,對源同步時序進行仿真,仿真結果表明,設計能滿足噪聲容限和過沖,仿真后的可知數據線和時間的延時約為0.3ns,滿足源同步系統設

2012-05-29 15:26:26 0

0 Cadence與三星的合作為移動消費電子產品帶來了新的工藝進展,使得20納米及未來工藝節點設計成為可能。

2012-06-10 10:43:54 984

984 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 該14納米產品體系與芯片是ARM、Cadence與IBM之間在14納米及以上高級工藝節點上開發系統級芯片(SoC)多年努力的重要里程碑。使用FinFET技術以14納米標準設計的SoC能夠大幅降低功耗。 這

2012-11-16 14:35:55 1270

1270 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已攜手Cadence?,為其20和14納米制程提供模式分類數據

2013-05-13 10:20:02 770

770 光刻物理分析器成功完成20納米系統級芯片(SoC)測試芯片流片。雙方工程師通過緊密合作,運用Cadence解決方案克服實施和可制造性設計(DFM)驗證挑戰,并最終完成設計。

2013-07-09 15:53:24 769

769 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布,歷經廣泛的基準測試后,半導體制造商聯華電子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence? “設計內”和“簽收”可制造性設計(DFM)流程對28納米設計進行物理簽收和電學變量優化。

2013-07-18 12:02:09 905

905 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)與上海華力微電子有限公司,今天共同宣布華力微電子基于Cadence ? Encounter? 數字技術交付出55納米平臺的參考設計流程。

2013-08-16 12:02:40 1445

1445 中芯國際新款40納米 Reference Flow5.1結合了最先進的Cadence CCOpt和GigaOpt工藝以及Tempus 時序簽收解決方案, 新款RTL-to-GDSII數字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲器設計上進行了驗證 ,可實現多塊模的整合。它將臺積電的3D堆疊技術和Cadence?3D-IC解決方案相結合,包括了集成的設計工具、靈活的實現平臺,以及最終的時序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1346

1346 利用Cadence工具進行板級電路信號完整性仿真

2016-02-22 16:21:13 52

52 2016年3月22日,中國上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10納米 FinFET工藝的數字、定制/模擬和簽核工具通過臺積電(TSMC)V1.0設計參考手冊(DRM)及SPICE認證。

2016-03-22 13:54:54 1026

1026 “我們與 Cadence 密切合作開發參考流程,幫助我們的客戶加快其差異化的低功耗、高性能芯片的設計,”中芯國際設計服務中心資深副總裁湯天申博士表示,“Cadence創新的數字實現工具與中芯國際28納米工藝的緊密結合,能夠幫助設計團隊將28納米設計達到更低的功耗以及更快的量產化。”

2016-06-08 16:09:56 2242

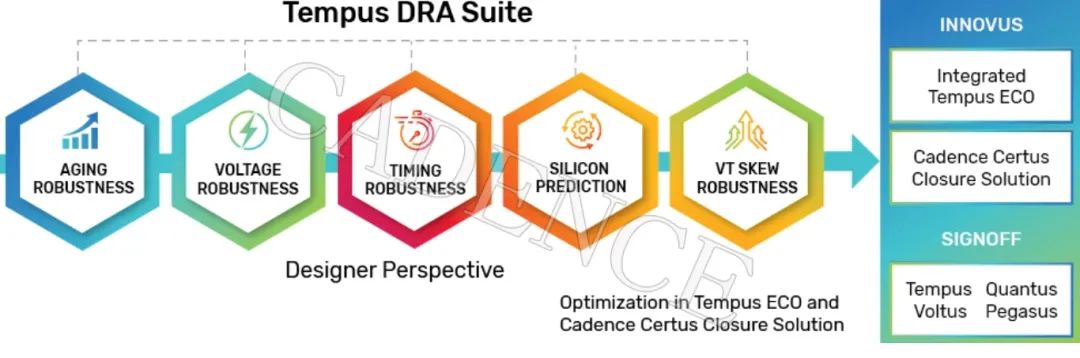

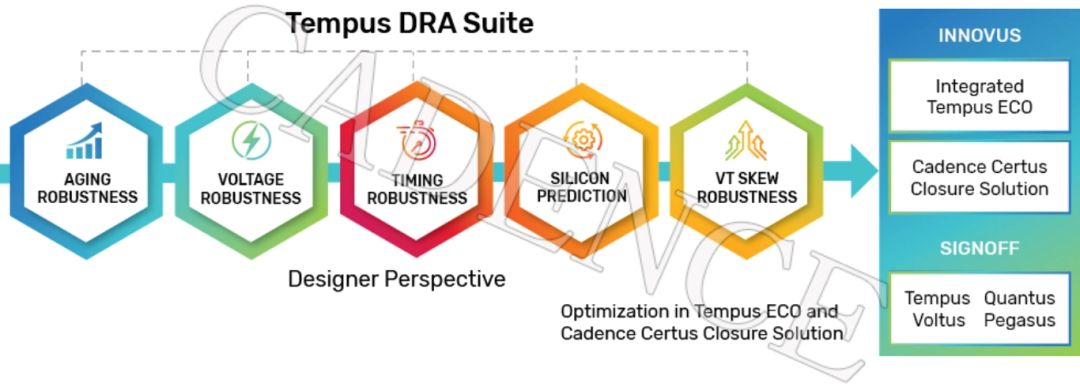

2242 之簽收與驗證部門,公司副總裁Anirudh Devgan看來,傳統的簽收流程卻沒能跟上這種需求的步伐。為幫助系統級芯片(SoC)開發者加速時序收斂,將芯片設計快速轉化為可制造的產品,Cadence于近期宣布推出劃時代時序簽收解決方案Tempus。它有何過人之處?讓我們一睹為快。 時序簽收目前在整個

2017-12-04 10:30:45 0

0 時序簽收是設計在被拿去制造前最后的時序檢驗步驟。因此,準確性至關重要。由于有越來越多的操作條件和操作模式需要驗證,今天我們所看到的時序簽收步驟需要花費較長的時間。

2019-10-14 14:20:05 1754

1754 EDA工具CADENCE原理圖與PCB設計說明

2021-07-15 09:38:12 50

50 基于Cadence軟件DRACULA工具的LVS檢查(村田電源技術(上海)有限公司深圳分公司)-基于Cadence軟件DRACULA工具的LVS檢查? ? ? ? ? ?

2021-09-18 17:40:54 24

24 基于Cadence軟件DRACULA工具的DRC檢查(ups電源技術維修)-該文檔為基于Cadence軟件DRACULA工具的DRC檢查講解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 15:25:26 27

27 CadenceLIVE China用戶大會開幕,燧原科技又有兩篇論文獲得了本次“CadenceLIVE杰出論文獎”,其中《Tempus-PI 仿真和實測關鍵時序路徑的一致性研究》則獲得“Best

2021-10-19 14:17:23 1387

1387 借助 Tempus SPICE 級精度的老化分析功能,Samsung Foundry 能夠提供長期的高度可靠性設計,同時達到更好的 PPA 結果和高達 4.2% 的頻率提升 Cadence

2021-11-19 11:00:13 2967

2967 Cadence Stylus Common UI 可在 Genus Synthesis、Innovus Implementation 和 Tempus Signoff 工具之間實現連續且易于

2022-04-08 09:26:03 3162

3162 電子發燒友網站提供《時序分析工具對比報告.pdf》資料免費下載

2022-09-27 11:08:11 0

0 上述流程會用到兩個主要工具,分別是用于模塊層次優化的 Tempus ECO,以及用于 SoC 層面靜態時序分析的 Tempus STA。這里缺失了全芯片(或子系統)優化與簽核。至于分區間功耗恢復等則只能忽略,因為實在沒時間處理。

2022-11-01 14:18:14 698

698 ,2023 年 6 月 30 日——楷登電子(美國? Cadence ?公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence?Virtuoso?Studio 設計工具和解決方案已獲得 Samsung Foundry 認證。 雙方的共同客戶可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 681

681 TimeGen 是一款圖形界面的波形繪制軟件,使用鼠標進行操作,廣泛應用于IC設計、硬件設計、集成電路等領域,安裝在windows系統中。TimeGen提供了直觀的用戶界面和豐富實用的繪圖工具,可以

2023-08-04 10:42:15 6597

6597

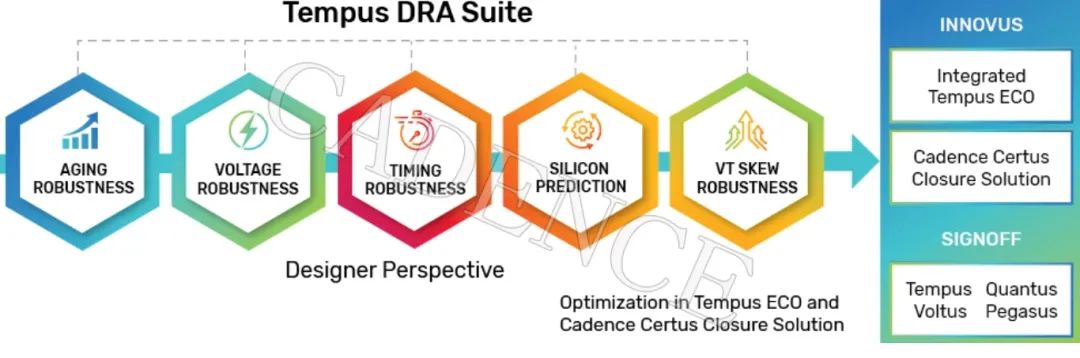

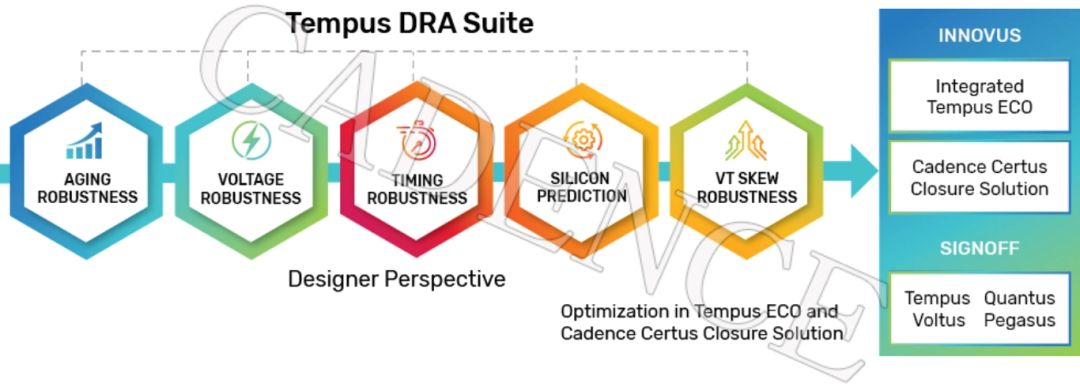

實現簽核時,為了保證芯片設計的耐用性,設計師會面臨重重挑戰,利用 Cadence Tempus 設計穩健性分析(DRA)套件為設計工程師提供領先的建模技術,可實現最佳功耗、性能和面積目標(PPA

2023-11-01 14:50:03 210

210

公司,NASDAQ:CDNS )近日宣布,Realtek 成功使用 Cadence Tempus ?Timing Solution 簽核 N12 高性能 CPU 內核,同時顯著改善了功率、性能和面

2023-11-06 10:10:01 206

206 優勢 1 Samsung Foundry 使用 Cadence Tempus Timing Solution 和 Quantus Extraction Solution 成功實現 SF5A

2023-12-04 10:15:01 244

244 及其影響的分析,客戶才能實現較現行設計方法更優秀的 PPA 目標。例如,全局額定值或全局的裕度會造成性能和功耗的顯著浪費。 為了應對類似挑戰,Cadence 持續創新并開發了 Cadence Tempus 設計穩健性分析(DRA)套件,提供解決上述問題所需要的分析能力。該套

2023-12-12 10:10:02 215

215

正在加载...

電子發燒友App

電子發燒友App

評論