全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復(fù)雜SoC的低功耗驗(yàn)證效率提高了30

2013-05-14 10:31:40 1832

1832 生活的抬頭、物聯(lián)網(wǎng)的建立,手持式消費(fèi)性電子產(chǎn)品與無線功能需求越來越高、設(shè)計(jì)越來越復(fù)雜,要提高性能的同時(shí)又要兼顧低功耗,需要有一高性能低功耗的主控 MCU 來作為平臺(tái)。另一方面,工業(yè)上的智能化也在展開,如

2017-10-08 15:38:58

,手持式消費(fèi)性電子產(chǎn)品與無線功能需求越來越高、設(shè)計(jì)越來越復(fù)雜,要提高性能的同時(shí)又要兼顧低功耗,需要有一高性能低功耗的主控 MCU 來作為平臺(tái)。另一方面,工業(yè)上的智能化也在展開,如遠(yuǎn)程監(jiān)控、數(shù)字化、網(wǎng)絡(luò)化...

2021-11-26 08:12:26

劉洋意法半導(dǎo)體(STMicroelectronics)目前宣布其首批整合其高性能8位架構(gòu)的超低功耗8位微控制器STM8L系列開始量產(chǎn)。STM8L系列以節(jié)省運(yùn)行和待機(jī)功耗為特色,該平臺(tái)采用意法半導(dǎo)體

2019-07-24 08:03:04

在之前的 IC 設(shè)計(jì)中,關(guān)注的參數(shù)主要是性能(timing)和面積(area)。 EDA 工具在滿足性能要求的情況下,最小化面積。功耗是一個(gè)不怎么關(guān)心的問題。 CMOS 工藝在相對較低的時(shí)鐘頻率下

2023-09-21 07:38:14

變異。需要多重物理IP平臺(tái),包括基于面積/功耗優(yōu)化庫、為高端性能定制優(yōu)化庫以及為CPU定制的優(yōu)化庫。 中芯國際SoC研發(fā)中心技術(shù)處長吳漢明博士:資金短缺是新工藝研發(fā)攔路虎 技術(shù)節(jié)點(diǎn)的發(fā)展方向離不開

2019-05-20 05:00:10

性價(jià)比合適的低功耗芯片,海速芯(十速)屬于臺(tái)資背景,創(chuàng)立95年,這樣的8位低功耗芯片去選擇好不好?

2022-12-09 18:10:00

上受益于和TSMC的合作。這種緊密的合作關(guān)系使Altera能夠在CycloneIII中充分發(fā)揮TSMC低功耗65nm工藝技術(shù)的優(yōu)勢,和競爭器件相比,大大降低了功耗。我們在45nm產(chǎn)品開發(fā)中也取得了很大進(jìn)步,將在2008年推出我們的首款45nm產(chǎn)品。

2019-07-16 08:28:35

``什么是低功耗?如何界定* 平均工作電流為 uA 級* 峰值電流不超過 15mA* 采用紐扣電池供電,電池壽命可達(dá)數(shù)年 在很多低功耗應(yīng)用場景中,是采用紐扣電池來供電的,采用紐扣電池來供電是低功耗

2018-02-06 15:32:54

和NMOS都導(dǎo)通時(shí)所引起的功耗;低功耗設(shè)計(jì)方法在設(shè)計(jì)一個(gè)系統(tǒng)時(shí)必須清楚性能和功耗的關(guān)系,也就是說需要明白你的系統(tǒng)是需要在盡可能低功耗的條件下提高性能,還是在盡可能高性能的條件下降低功耗,這對于...

2021-11-11 06:03:31

降低功耗不光能夠大大的節(jié)約電能還能簡化電源部分的設(shè)計(jì),甚至可以用于手持設(shè)備上面使用,這些都已經(jīng)越來越成為未來產(chǎn)品的設(shè)計(jì)方向。

2021-02-26 07:27:17

Altera及其他PFGA/ASIC廠家實(shí)現(xiàn)高性能和低功耗的顯著設(shè)計(jì)目標(biāo)。 圖3 EM1130的SmartVID有助FPGA顯著降低靜態(tài)功耗 任何數(shù)字功率控制器獲得成功的基本要求之一是可行的,易于

2018-11-30 17:05:26

是,硬核IP模塊功耗降低了65%,而性能提高了50%,表1列出了Cyclone V FPGA中的硬核IP功能,以及通過硬核實(shí)現(xiàn)所節(jié)省的資源量。表1 Cyclone V FPGA中的硬核IP功能 硬核IP

2015-02-09 15:02:06

檢測電路,以適應(yīng)于不同電機(jī)及不同控制方式的要求;同時(shí)由于采用了高性能的MCU,更多類型的通信接口可被靈活應(yīng)用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

和最低的成本獲得最可靠的接收效果。因此它是真正意義上的無線高頻調(diào)制信號輸入,數(shù)字解調(diào)信號輸出的單片接收器件。發(fā)射端:是一款低功耗、高性能、寬工作電壓、大輸出功率的 433MHz短距離無線通訊發(fā)射機(jī)

2021-12-25 16:54:05

描述適用于高性能 DAQ 系統(tǒng)的 TIDA-01055 參考設(shè)計(jì)優(yōu)化了 ADC 基準(zhǔn)緩沖器,以提高 SNR 性能并降低功耗(使用 TI OPA837 高速運(yùn)算放大器)。該器件用于復(fù)合緩沖器配置

2018-12-07 11:51:25

高性能,低功耗:越來越多的應(yīng)用需要滿足這一需求,尤其是由電池供電的移動(dòng)設(shè)備。特別是在物聯(lián)網(wǎng)、工業(yè)4.0和數(shù)字化時(shí)代,這些手持設(shè)備大大方便了人們的日常生活。從移動(dòng)生命體征監(jiān)測到工業(yè)環(huán)境中的機(jī)器和系統(tǒng)

2021-11-10 07:00:00

顯示器需要“靈巧集成”,因?yàn)樵诮M合各種顯示接口功能時(shí)還要克服一些重大技術(shù)難題。如果要把高性能模擬電路和高速數(shù)字電路集成到一個(gè)解決方案中,需要有專門的混合信號設(shè)計(jì)技術(shù)方面的經(jīng)驗(yàn)。一個(gè)集成的接口需要產(chǎn)品

2018-12-13 09:53:01

可以自如地控制假肢完成復(fù)雜動(dòng)作時(shí),你是否知道與假肢相連的探測器可以檢測人體肌肉的最細(xì)微運(yùn)動(dòng)從而實(shí)現(xiàn)對假肢的控制;也許你并沒有留意到用手機(jī)通話時(shí)顯示屏?xí)詣?dòng)關(guān)閉以便降低功耗,這是手機(jī)檢測到顯示屏被物體

2019-07-16 06:23:53

,采用低K值電介質(zhì)工藝,不僅提高了性能還降低了寄生電容。結(jié)構(gòu)的改變,如增強(qiáng)的邏輯單元內(nèi)部互連,可實(shí)現(xiàn)更強(qiáng)大的功能,而無需更多的功耗。StraTIx II更大的改變是采用了六輸入查找表(LUT)架構(gòu),能夠

2015-02-09 14:58:01

。除此之外,設(shè)計(jì)中采用一些低功耗技巧,也可以降低靜態(tài)功耗。IGLOO具有功耗友好的器件架構(gòu),能提供靜態(tài)、睡眠、Flash*Freeze功耗模式,允許采用動(dòng)態(tài)電壓和頻率調(diào)節(jié)技術(shù)來降低系統(tǒng)整體實(shí)際功耗。提供可選擇

2019-07-05 07:19:19

來實(shí)質(zhì)的功耗節(jié)省。然而,在設(shè)計(jì)過程的初始階段,自動(dòng)減少功耗則比較困難。但這并不代表無法降低功耗: 首先可以采用高級設(shè)計(jì)技術(shù)來減少功耗,例如電壓/功率島劃分、模塊級時(shí)鐘門控、功率下降模式、高效存儲(chǔ)器配置

2017-06-29 16:46:52

(PSR)功能。在啟用 PSR 功能時(shí),采用多種低功耗選項(xiàng)來降低動(dòng)態(tài)操作功耗。通過 I2C 專用的硬件引腳或固件控制,可以方便地將 IT6151設(shè)置為待機(jī)模式,這是一種在無顯示條件下使用的極低功耗

2022-10-08 15:42:42

如果我只在 12.5Hz 下操作加速度計(jì),LSM6DS3TR-C 的低功耗模式和高性能模式有什么區(qū)別?

2022-12-09 06:47:13

的使用使用定時(shí)器來觸發(fā)ADC轉(zhuǎn)換,以盡量減少所用資源您可使用上述幾種功能在您的應(yīng)用中降低MSP432 MCU的ADC功耗?

2017-04-18 20:07:50

,且具有最低功耗”。 MAX3948主要優(yōu)勢 4個(gè)發(fā)射通道的總功耗低于2W,使QSFP+模塊功耗降至3.5W以下。 直流耦合激光器接口(專利申請中,申請?zhí)?3/352,011)有效降低功耗、減少

2012-12-12 16:36:17

)等功能以及驅(qū)動(dòng)發(fā)射器線圈的集成式全橋。該設(shè)計(jì)提供足夠的發(fā)射輸出功率,使5 W無線充電接收器輸出到設(shè)備的電池進(jìn)行充電,并采用高級數(shù)字ASK信號處理,以確保可靠的互操作性。低功耗CoolFlux DSP

2015-02-07 15:50:42

,nRF52832 WL-CSP器件具有超緊湊3.0 X 3.2mm占位面積,并提供相同的全功能單芯片特性集和同級最佳超低功耗應(yīng)用運(yùn)作; 其功能強(qiáng)大的板載64MHz ARM? Cortex?-M4F

2016-07-24 09:37:57

MCUMSP430FR5994 MCU 方框圖MSP430F599x 微控制器是采用這種新型 LEA模塊外設(shè)的領(lǐng)先器件。這些高性能的 16 位 MCU 具有屢獲殊榮的超低功耗架構(gòu)、最大 256KB 的嵌入式鐵電隨機(jī)存取存儲(chǔ)器 (FRAM) 以及多種靈活高效的外設(shè),構(gòu)成了一個(gè)適用于很多數(shù)字信號處理應(yīng)用的絕佳 MCU 平臺(tái)。`

2019-12-20 15:30:02

cogobuy降低功耗的措施 每個(gè)廠商對于降低功耗都有不同的處理方式。雖然每個(gè)MCU都有休眠狀態(tài)或都有可能實(shí)現(xiàn)很低的工作耗電量,但是有的芯片在處于很低功耗的時(shí)候,基本功能也所剩無幾了,沒有

2012-03-23 11:18:31

的四分之一,為瞄準(zhǔn)新一代高性能可穿戴產(chǎn)品而設(shè)計(jì)。nRF52832 WL-CSP器件具有超緊湊3.0 X 3.2mm占位面積,并提供相同的全功能單芯片特性集和同級最佳超低功耗應(yīng)用運(yùn)作; 其功能強(qiáng)大的板載

2017-08-16 10:43:56

申請理由:1.實(shí)現(xiàn)超低功耗,高性能智能手環(huán)設(shè)計(jì)2.智能手環(huán)需要六軸加速度計(jì)來檢測人行步數(shù),F(xiàn)ireBLE內(nèi)置MPU6050,在功耗和性能上它一個(gè)不錯(cuò)的選擇3.方便設(shè)計(jì)手環(huán),提高可用性,可靠性項(xiàng)目描述

2015-07-08 15:17:13

申請理由:實(shí)現(xiàn)超低功耗,高性能設(shè)計(jì),提高功能的可用性,可靠性程度,Cortex-A8是不錯(cuò)的選擇。項(xiàng)目描述:本項(xiàng)目完成基于嵌入式系統(tǒng)智能穿戴手表樣機(jī)的研制,智能手表內(nèi)置超低功耗藍(lán)牙4.0模塊,可以

2015-07-08 14:57:19

【單片機(jī)開發(fā)300問】怎樣進(jìn)一步降低功耗功耗,在電池供電的儀器儀表中是一個(gè)重要的考慮因素。PIC16C××系列單片機(jī)本身的功耗較低(在5V,4MHz振蕩頻率時(shí)工作電流小于2mA)。為進(jìn)一步降低功耗

2011-12-07 13:59:56

MC33129用于隔離式2.0 W反激式穩(wěn)壓器的典型應(yīng)用。 MC34129 / MC33129是高性能電流模式開關(guān)穩(wěn)壓器,專為低功耗數(shù)字電話應(yīng)用而設(shè)計(jì)

2020-07-29 09:56:40

從Xilinx公司推出FPGA二十多年來,研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其

2019-09-20 06:33:32

,工業(yè)界對芯片設(shè)計(jì)的要求已從單純追求高性能、小面積轉(zhuǎn)為對性能、面積、功耗的綜合要求。而微處理器作為數(shù)字系統(tǒng)的核心部件,其低功耗設(shè)計(jì)對降低整個(gè)系統(tǒng)的功耗具有重要的意義。

2019-10-14 07:48:14

過程來減少資源的使用使用定時(shí)器來觸發(fā)ADC轉(zhuǎn)換,以盡量減少所用資源您可使用上述幾種功能在您的應(yīng)用中降低MSP432 MCU的ADC功耗?

2016-11-18 10:14:35

—— 集高性能、高實(shí)時(shí)、低功耗,高性價(jià)比于一身 的RISC-V 通用微控制器。 “先楫的HPM6700系列在今年1月份量產(chǎn)之后,在市場上得到了廣泛的認(rèn)可,已經(jīng)批量出貨。HPM6300延承了HPM6700

2022-05-07 17:16:04

模式標(biāo)準(zhǔn)的嚴(yán)格效率要求。電池供電型應(yīng)用的用戶希望獲得最長的運(yùn)行時(shí)間,而降低功耗可以直接延遲設(shè)備運(yùn)行時(shí)間。今天,我們都知道,使用同步整流器可以降低功耗,并提高散熱性能。低功耗應(yīng)用的降壓轉(zhuǎn)換器和控制器設(shè)計(jì)人

2013-08-12 15:05:53

基于Cortex-A53架構(gòu)的低功耗高性能處理器RK3328有哪些功能呢?

2022-03-09 06:27:22

本設(shè)計(jì)以MSP430 G2553為核心控制器,搭建了低功耗數(shù)字多功能表系統(tǒng)。對于交流電壓測量,用AD637真有效值轉(zhuǎn)換芯片將交流信號轉(zhuǎn)換為直流電壓后測量;對于電阻測量,阻值較小電阻采用恒流源法測量

2018-06-21 01:59:36

基于ZU3EG的低功耗高性能嵌入式AI高性能計(jì)算模組 省的空間可以用來增加能夠提高系統(tǒng)性能的組件,尤其是設(shè)計(jì)小組希望添加一個(gè)以上處理器時(shí),這一點(diǎn)非常重要。設(shè)計(jì)嵌入式DSP處理器或系統(tǒng)功耗要求嚴(yán)格的系統(tǒng)時(shí),采用DSP專用技術(shù)、操作系統(tǒng)及其支持軟件可以降低功耗

2016-08-20 11:26:46

本文基于Viitex-5 LX110驗(yàn)證平臺(tái)的設(shè)計(jì),探索了高性能FPGA硬件系統(tǒng)設(shè)計(jì)的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

2021-04-26 06:43:55

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,如同其它多數(shù)事物一樣,降低功耗的設(shè)計(jì)就是一種協(xié)調(diào)和平衡藝術(shù),在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-15 08:28:42

復(fù)雜器件專業(yè)技術(shù)相結(jié)合,將為系統(tǒng)供應(yīng)商提供低功耗的芯片方案,供他們在此基礎(chǔ)上持續(xù)提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導(dǎo)入到最新的FPGA中,進(jìn)一步降低功耗。最終實(shí)現(xiàn)

2019-07-31 07:13:26

對于各種不同的數(shù)據(jù)中心工作負(fù)載,F(xiàn)PGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

每輛汽車中都有一個(gè)包含傳感器、電機(jī)和開關(guān)的龐大車載網(wǎng)絡(luò)。這些網(wǎng)絡(luò)不斷發(fā)展以適應(yīng)車輛上日益增加的連通性,總功耗也隨之增加,因此可能會(huì)對車輛的排放產(chǎn)生負(fù)面影響。 根據(jù)所使用的網(wǎng)絡(luò)協(xié)議,有幾種方法可以降低功耗

2022-11-04 07:07:38

為什么需要低功耗設(shè)計(jì)?如何實(shí)現(xiàn)數(shù)字IC低功耗的設(shè)計(jì)?

2021-11-01 06:37:46

節(jié)省功耗的特性的實(shí)現(xiàn)和各種最少功耗數(shù)據(jù)存儲(chǔ)技術(shù)的實(shí)現(xiàn)。除此之外,設(shè)計(jì)中采用一些低功耗技巧,也可以降低靜態(tài)功耗。 IGLOO具有功耗友好的器件架構(gòu),能提供靜態(tài)、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

射頻VMMK器件是怎么提高性能的?通過降低寄生電感和電容嗎?

2019-08-01 08:23:35

需要消耗功率,特別是在處理大量數(shù)據(jù)的時(shí)候,需要高性能的處理器,這可能會(huì)消耗大量的功率。因此,系統(tǒng)中某一功能用軟件實(shí)現(xiàn),還是用硬件實(shí)現(xiàn),需要綜合計(jì)算后進(jìn)行設(shè)計(jì)。 3.3采用快速算法 數(shù)字信號處理中

2014-01-21 11:22:57

高低電平翻轉(zhuǎn)跳變沿期間,電流很大,存在較大功耗,所以,降低硬件電路功耗主要是降低電路動(dòng)態(tài)功耗。 (3)采用多CPU系統(tǒng) 盡管現(xiàn)在已有各種可在不過多加重功耗負(fù)擔(dān)的前提下提高性能的技術(shù),但用一個(gè)芯片

2020-07-08 15:52:10

可選,并能夠以低電流進(jìn)行備用電池供電。此外,產(chǎn)品還應(yīng)盡可能地提高響應(yīng)速度,并具備更多的內(nèi)部資源。 近日,微芯(Microchip)公司推出的具有多種靈活低功耗休眠模式且工作電流超低的PIC24F

2019-07-10 08:10:06

。為了使產(chǎn)品更具競爭力,工業(yè)界對芯片設(shè)計(jì)的要求已從單純追求高性能、小面積轉(zhuǎn)為對性能、面積、功耗的綜合要求。而微處理器作為數(shù)字系統(tǒng)的核心部件,其低功耗設(shè)計(jì)對降低整個(gè)系統(tǒng)的功耗具有重要的意義。 本文首先介紹

2016-06-29 11:28:15

CJC89888芯片特點(diǎn)是什么?低功耗芯片設(shè)計(jì)要點(diǎn)是什么?怎么實(shí)現(xiàn)低功耗單芯片高性能音頻CODEC的設(shè)計(jì)?

2021-06-03 06:27:25

降低功耗的最重要的途徑是使用MSP430的時(shí)鐘系統(tǒng)來最大限度地提高MSP430處于低功耗模式的時(shí)間。怎樣降低msp430的功耗?

2014-11-09 23:10:18

高性能、低功耗是當(dāng)前電子技術(shù)發(fā)展的方向,對于汽車中的各種ECU來說如何實(shí)現(xiàn)低功耗呢?一、ECU也耗油據(jù)不完全統(tǒng)計(jì),我國汽車保有量在20000萬輛以上,由此帶來的能源消耗以及環(huán)境污染問題越發(fā)嚴(yán)峻。目前

2019-05-10 04:23:39

在產(chǎn)品設(shè)計(jì)時(shí),除考慮降低成本、增加功能之外,還越來越重視其環(huán)保性能。選擇低功耗及采用無鉛/符合RoHS標(biāo)準(zhǔn)的封裝的IC器件是設(shè)計(jì)環(huán)保系統(tǒng)的關(guān)鍵。設(shè)計(jì)MAX9509低功耗視頻濾波放大器時(shí),需要考慮一些特殊

2020-12-17 09:52:10

基礎(chǔ)(凌特資料)實(shí)現(xiàn)可靠的高性能數(shù)字電源為了更好地理解數(shù)字電源的架構(gòu)選擇和關(guān)鍵性能參數(shù),最好先搞清楚使用數(shù)字回路的好處。通過采用數(shù)字回路控制來實(shí)現(xiàn)電源轉(zhuǎn)換,可使開發(fā)人員的設(shè)計(jì)和業(yè)務(wù)大大受益。通過可再編程

2020-07-02 14:31:59

Altera20nmArria10FPGA和SoC中,以及14nmStratix10FPGA和SoC中。該新功能支持設(shè)計(jì)人員以相同的定點(diǎn)性能和效率在浮點(diǎn)中實(shí)現(xiàn)其算法,且不會(huì)對功耗、面積或者密度產(chǎn)生任何影響,也不會(huì)損失定點(diǎn)特性或

2019-07-03 07:56:05

假定晶體管的過渡時(shí)間是有限的,因此在每次信號切換時(shí)都存在短路功耗。 在數(shù)字IC整個(gè)設(shè)計(jì)流程中可以通過改變工作電壓,翻轉(zhuǎn)率和負(fù)載電容來改善switch power,從而改善動(dòng)態(tài)功耗。 低功耗設(shè)計(jì)的常用

2020-07-07 11:40:06

增加的功耗就會(huì)抵消所降低的功耗,這也是動(dòng)態(tài)降低功耗設(shè)計(jì)的取舍標(biāo)準(zhǔn)。為克服控時(shí)鐘的缺點(diǎn),可以采用粗粒度的系統(tǒng)設(shè)計(jì)方法。門控時(shí)鐘的應(yīng)用并不拘泥于對每個(gè)觸發(fā)器的控制,而是從大處著眼,控制系統(tǒng)中較大的功能

2013-05-16 20:00:33

,使其低于采用獨(dú)立MCU和分立外設(shè)的情況。本系列文章共分三部分,在第二部分中,我們將介紹SoC以及如何提高其效率,從而有利于系統(tǒng)設(shè)計(jì),降低功耗。

2016-07-29 15:25:00

stm32進(jìn)入低功耗模式,必須用中斷來喚醒,現(xiàn)在就是不用這種模式,如何通過程序來降低功耗啊

2019-05-06 18:43:22

的厚度減小)。 今天,我們已經(jīng)擁有在單芯片上實(shí)現(xiàn)完整系統(tǒng)/子系統(tǒng)高度集成的SoC。除了集成度之外,就功耗而言,這些SoC也有助于降低平均功耗,使其低于采用獨(dú)立MCU和分立外設(shè)的情況。 本系列文章共分三部分,在第二部分中,我們將介紹SoC以及如何提高其效率,從而有利于系統(tǒng)設(shè)計(jì),降低功耗。

2020-08-20 12:30:00

生活的抬頭、物聯(lián)網(wǎng)的建立,手持式消費(fèi)性電子產(chǎn)品與無線功能需求越來越高、設(shè)計(jì)越來越復(fù)雜,要提高性能的同時(shí)又要兼顧低功耗,需要有一高性能低功耗的主控 MCU 來作為平臺(tái)。另一方面,工業(yè)上的智能化也在展開,如

2019-01-25 16:15:23

Tensilica 日前宣布與Cadence 合作,根據(jù)Tensilica 的330HiFi 音頻處理器和388VDO 視頻引擎,為其多媒體子系統(tǒng)建立一個(gè)通用功耗格式(CPF)的低功耗參考設(shè)計(jì)流程。Cadence 和Tensilica公司的工

2009-12-04 13:54:39 32

32 中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設(shè)計(jì)低功耗尖端器件成為可能

2009-10-31 07:48:01 1228

1228 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司今天宣布推出一款全面的低功耗設(shè)計(jì)流程,面向

2009-11-04 17:05:17 589

589 Microchip超低功耗(XLP)系列 新增高密度8-bit微控制器

新聞?wù)?#8226; PIC18F47J13是第一款采用28接腳封裝并配備128 KB快閃程式內(nèi)存的8-bit微控制器&#

2010-09-30 11:33:05 721

721 比同類競爭產(chǎn)品性能提高33%,片上內(nèi)存擴(kuò)大250%且功耗降低20% ADI(Analog Devices,Inc.)最新推出32位浮點(diǎn)數(shù)字信號處理器(DSP)產(chǎn)品SHARC2148x

2011-02-28 12:59:03 39

39 中芯國際新款40納米 Reference Flow5.1結(jié)合了最先進(jìn)的Cadence CCOpt和GigaOpt工藝以及Tempus 時(shí)序簽收解決方案, 新款RTL-to-GDSII數(shù)字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 9月24日——全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence? 混合信號低功耗設(shè)計(jì)流程,使其最新款節(jié)能型

2013-09-25 09:59:51 913

913 “我們與 Cadence 密切合作開發(fā)參考流程,幫助我們的客戶加快其差異化的低功耗、高性能芯片的設(shè)計(jì),”中芯國際設(shè)計(jì)服務(wù)中心資深副總裁湯天申博士表示,“Cadence創(chuàng)新的數(shù)字實(shí)現(xiàn)工具與中芯國際28納米工藝的緊密結(jié)合,能夠幫助設(shè)計(jì)團(tuán)隊(duì)將28納米設(shè)計(jì)達(dá)到更低的功耗以及更快的量產(chǎn)化。”

2016-06-08 16:09:56 2242

2242 一種高性能低功耗SEU免疫鎖存器_黃正峰

2017-01-08 10:40:54 0

0 的 PowerVR Series7XT Plus GPU,實(shí)現(xiàn)了更高性能與更低功耗的圖形功能。具備完整功能的 10 核 Helio X30 是聯(lián)發(fā)科迄今為止最先進(jìn)的智能手機(jī)芯片組,與前一代產(chǎn)品相比,性能提高了 2.4 倍,功耗節(jié)省達(dá) 60%。

2017-03-17 12:04:20 15059

15059 隨著架構(gòu)師開始利用 AI 提高性能和降低功耗,并為未來芯片的開發(fā)、制造和更新奠定基礎(chǔ),人工智能也開始影響半導(dǎo)體設(shè)計(jì)。技術(shù)增加了芯片粒度,但隨著架構(gòu)需要處理更大數(shù)據(jù)量,設(shè)計(jì)起點(diǎn)也變了。

2018-11-16 16:46:53 4174

4174 與傳統(tǒng)FPGA架構(gòu)相比,UltraScale架構(gòu)引入了許多創(chuàng)新,可提高性能并降低功耗。

在本視頻中,我們將重點(diǎn)介紹路由,邏輯和實(shí)現(xiàn)軟件的增強(qiáng)功能......

2018-11-22 06:45:00 3056

3056 采用極紫外(EUV)光刻技術(shù)的Cadence 數(shù)字全流程解決方案已通過Samsung Foundry 5nm早期低功耗版(5LPE)工藝認(rèn)證。

2019-07-11 16:36:47 3436

3436 UltraSoC宣布:為其嵌入式分析架構(gòu)新增高速通信功能,它可支持在數(shù)據(jù)中心、高性能計(jì)算、人工智能(AI)和存儲(chǔ)應(yīng)用中進(jìn)行調(diào)試和性能優(yōu)化。

2019-12-02 19:26:30 747

747 電磁突破可以降低功耗,提高數(shù)字存儲(chǔ)器的速度。克里斯蒂安·比內(nèi)克(Christian Binek)說,“達(dá)到這一點(diǎn)是一個(gè)非常痛苦的過程。”

2021-04-14 16:40:36 1626

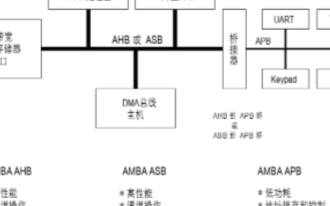

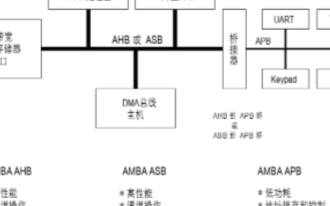

1626 AHB(高級高性能總線):用于高性能高時(shí)鐘頻率的系統(tǒng)模塊,AHB 擔(dān)當(dāng)高性能系統(tǒng)的中樞總線。AHB 支持處理器,片上存儲(chǔ)器,片外存儲(chǔ)器以及低功耗外設(shè)宏功能單元之間的有效連接。

2021-07-02 10:35:07 2893

2893

的先進(jìn)設(shè)計(jì)。另一款 CPU 設(shè)計(jì)采用 AI 賦能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的數(shù)字設(shè)計(jì)流程,借助臺(tái)積電 N5 制程工藝,成功讓功耗降低 8%,設(shè)計(jì)面積縮小 9%,同時(shí)顯著提升了工程效率。

2023-02-06 15:02:48 1048

1048 內(nèi)容提要 1 通過利用 Cadence AI 驅(qū)動(dòng)云端數(shù)字全流程,Imagination 成功將其最新 5nm 節(jié)點(diǎn)的漏電功耗降低 20%,將總功耗降低 6%,同時(shí)改善了面積和性能

2023-10-18 15:50:01 160

160 電子發(fā)燒友網(wǎng)站提供《設(shè)計(jì)低功耗和高性能的工業(yè)應(yīng)用.pdf》資料免費(fèi)下載

2023-11-16 14:50:42 0

0

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論