隨著電子組件功能提升,各種電子產品不斷朝向高速化方向發展,然而高性能化、多功能化、可攜帶化的結果,各式各樣的EMC(Electro Magnetic Compatibility)問題,卻成為設計者揮之不去的夢魘。

目前EMI(Electro Magnetic Interference)噪訊對策,大多仰賴設計者長年累積的經驗,或是利用仿真分析軟件針對框體結構、電子組件,配合國內外要求條件與規范進行分析,換句話說電子產品到了最后評鑒測試階段,才發現、對策EMI問題,事后反復的檢討、再試作與對策組件的追加,經常變成設計開發時程漫無節制延長,測試費用膨脹的主要原因。

EMI主要發生源之一亦即印刷電路板(Printed Circuit Board,以下簡稱為PCB)的設計,自古以來一直受到設計者高度重視,尤其是PCB Layout階段,若能夠將EMI問題列入考慮,通常都可以有效事先抑制噪訊的發生,有鑒于此本文要探討如何在PCB的Layout階段,充分應用改善技巧抑制EMI噪訊的強度。

測試條件

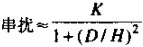

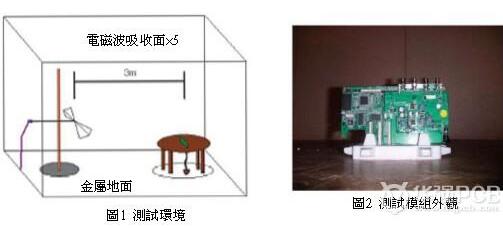

如圖1所示測試場地為室內3m半電波暗室,預定測試頻率范圍為30MHz~1000MHz的電界強度,依此讀取峰值點(Peak Point)當作測試數據(圖2)。

圖3是被測基板A的外觀,該基板為影像處理系統用電路主機板,動作頻率為27MHz與54MHz,電路基板內建CPU、Sub CPU、FRASH,以及SDRAM×5、影像數據/數字轉換處理單元、影像輸出入單元,此外被測基板符合“VCCI規范等級B”的要求,測試上使用相同的電源基板(Board)與變壓器(Adapter)。

首先針對被測基板A進行下列電路設計變更作業:

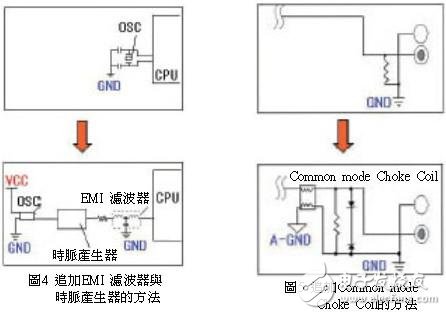

?CPU的頻率線(Clock Line)追加設置EMI噪訊對策用濾波器(Filter),與頻率產生器(Clock Generator)( 圖4)。

?影像輸出入單元追加設置Common mode Choke Coil(DLWxxx系列)(圖5)

?各IC電源輸入線的Bypass Condenser與電源之間,追加設置Ferrite Beads(圖6)。

?追加設置Bypass Condenser,使各IC的所有電源腳架,全部從基板電源層(Plane)通過Bypass Condenser提供電源(圖7)。

各種EMI噪訊對策

a.EMI噪訊對策用電容

接著進行EMI測試獲得圖8的測試結果,根據測試結果再進行噪訊抑制設計作業,在此同時將設計變更的被測基板A的設計數據讀入EMI噪訊抑制支持工具,并針對支持工具指出的主要部位,例如頻率線、Bus導線Via周圍,分散設置EMI噪訊對策用電容(圖9),主要原因是信號導線的return路徑如果太長或是非連續狀態時,EMI噪訊有增大之虞,為了縮短Return路徑,因此設置連接電源與接地的電容。

圖10~圖13是改變上述電容容量時的EMI噪訊測試結果,根據測試結果顯示,依照圖14的頻率范圍設置的大容量EMI噪訊對策用電容DuF,可以抑制低頻噪訊Level。雖然設置電容增加PCB的容量負載,不過為了要抑制噪訊,設置在各部位的電容頻率特性,卻可以發揮預期的EMI噪訊抑制效果。

實際應用時只要在頻率導線、Bus導線等高頻導線 圖案(Pattern)附近、形成CPU、Return路徑的內層面(Plane)的分斷附近、形成噪訊出入口的基板側面附近分散設置EMI噪訊對策用電容,就可以消除該部位周邊的噪訊。

對各式各樣基板外形、組件封裝、導線的PCB而言,只要以一定間隔設置EMI噪訊對策用電容,同樣可以獲得分散性的噪訊抑制效果。

b.改變基板的層結構

接著針對被測基板A進行層結構改善,制作圖15所示6層Built up被測基板B,它是利用“Pad on Via”與“雷射Via”加工技術,將上述被測基板A的外層信號線導線變成內層,使Return電流可能流入接地Plane,外層當作接地Plane包覆所有信號層。

改變被測基板結構主要理由是一般4層基板的Return路徑,通常都設有可以通行電源Plane或是最短距離接地,因此在貫穿部位經常造成Return路徑迂回問題,如果信號導線包覆接地Plan e,如此一來大部份的Return路徑會流入接地 Plane,進而解決Return路徑迂回的困擾,被測基板B就是根據上述構想制成 ,因此Return路徑在PCB整體減少30%,同時縮減信號圖案與Return路徑構成的電流Loop距離,進而達成EMI噪訊抑制的目的。圖16是被測基板B的各層結構圖。

圖16是被測基板B的EMI噪訊測試結果,根據測試結果顯示包含利用外層接地Plane的遮蔽(Field)結構,與回避Return路徑迂回的設計確實具有抑制EMI噪訊的效果,不過實際上各式各樣的電路基板要作如此的層結構變更,勢必面臨制作成本暴增的困擾,尤其是所有信號導線都將Return路徑列入設計考慮的話,幾乎無法作業,因此Layout階段盡量避免高頻信號導線透過Via作布線,同時必需在該信號導線鄰近的層設置接地Plane,借此防止Return路徑迂回或是分斷,接地Plane之間以復數Via連接,Return路徑利用復數Via作理想性的歸返。

c.設置多點Grand接地

Return電流流動時PCB內的接地Plane會產生電位差,該電位差往往是EMI噪訊的發生原因之一,而且可能會通過PCB形成所謂的二次噪訊,因此將接地Plane與金屬板作多點連接(圖18、圖19),使PCB的側面與中心位置得電位差均勻化,同時降低接地Plane本身的阻抗(Impedance)并抑制電壓下降。

圖20是多點接地后的EMI測試結果,由圖可知低頻領域EMI噪訊強度略為上升,不過200MHz以上時EMI噪訊受到抑制,這意味著多點接地的有效性獲得證實。

d.鋪設Shield

圖21是在基板側面鋪設Shield的實際外觀,具體方法是在基板側面粘貼導電膠帶,試圖借此抑制基板內層信號線、Via與電源Plane的噪訊,接著再與外層接地Plane連接,測試基板側面的EMI噪訊遮蔽效果,圖22是基板側面鋪設Shield的EMI測試結果,根據測試結果顯示200MHz以下時EMI噪訊強度有下降趨勢,甚至符合規范的Level,證實基板側面鋪設Shield確實可以抑制EMI噪訊。

實際制作PCB時在基板側面鋪設Shield,同樣會面臨成本上升的質疑,類似圖23在基板側面附近設置接地Plane與連續性貫穿Via的新結構,除了可是解決成本問題之外,還可以有效抑制基板側面的EMI噪訊強度;圖24是結合以上各種EMI噪訊對策的PCB測試結果。

綜合以上介紹的EMI噪訊對策,分別如下所示:

?設置EMI噪訊對策用電容

?回避Return路徑迂回的基板層結構設計

?設置多點Grand接地

?基板側面包覆Shield

實際上PCB得EMI噪訊對策會隨著組件封裝、導線、基板外形、層結構,與筐體限制出現極大差異,因此本文主要是探討如何在PCB Layout階段,充分應用EMI噪訊對策手法,根據一連串的對策中找出最符合制作成本,同時又可以滿足規范要求的方法。

電子發燒友App

電子發燒友App

評論