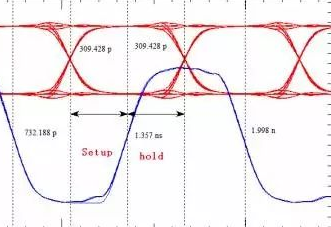

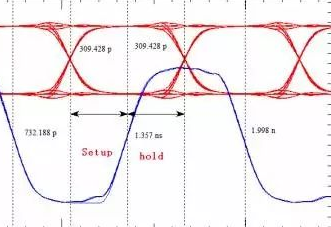

DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,

2017-09-26 11:39:47 6363

6363

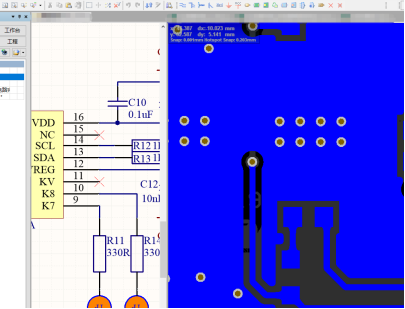

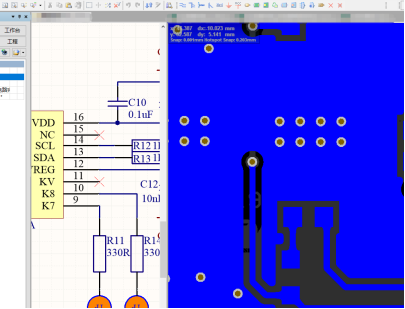

4層藍(lán)牙產(chǎn)品PCB設(shè)計(jì)素材

2023-09-20 07:43:16

關(guān)于PCB設(shè)計(jì)用哪個軟件好?

2012-05-21 10:22:44

經(jīng)驗(yàn),畫過通訊、工業(yè)控制、嵌入式、數(shù)碼消費(fèi)類產(chǎn)品的高速、高密度、數(shù)模混合等PCB設(shè)計(jì)。處理高速信號很有經(jīng)驗(yàn),通過對于疊層的控制、信號的分類、拓?fù)浣Y(jié)構(gòu)的確定、微帶線帶狀線分析、阻抗的控制、時序的分析、平面

2013-03-26 14:52:54

PCB設(shè)計(jì)20H原則大家聽過嗎?還有 怎么減少信號層到參考平面的距離?

2016-01-25 22:52:36

PCB設(shè)計(jì)中為什么要求電源層緊靠地層,有什么作用嗎?

2014-10-24 14:22:08

PCB設(shè)計(jì)中疊層算阻抗時需注意哪些事項(xiàng)?

2019-05-16 11:06:01

在PCB設(shè)計(jì)中,工程師難免會面對諸多問題,一下總結(jié)了PCB設(shè)計(jì)中十大常見的問題,希望能對大家在PCB設(shè)計(jì)中能夠起到一定的規(guī)避作用。

2021-03-01 10:43:30

PCB設(shè)計(jì)中 禁止布線層、絲印層、機(jī)械層這三個層好像概念挺模糊的,比如畫板子的外圍標(biāo)識的時候,使用禁止布線層,同時也可以使用絲印層,那這兩個層有啥區(qū)別啊?另外這個機(jī)械層好像并沒有什么作用,大家在什么情況下會使用這個機(jī)械層?

2019-08-16 04:36:00

與準(zhǔn)確度;(5)Drill層標(biāo)注:Drill層標(biāo)注的信息是提供給PCB加工工廠PE的加工要求圖紙,需要遵循行業(yè)規(guī)范、保證Drill加工信息的準(zhǔn)確性與完備度;(6)PCB設(shè)計(jì)文件輸出:PCB設(shè)計(jì)的最終文件

2017-10-24 14:17:31

;(4)絲印調(diào)整:清晰準(zhǔn)確的絲印設(shè)計(jì),可以提升電路板的后續(xù)測試、組裝加工的便捷度與準(zhǔn)確度;(5)Drill層標(biāo)注:Drill層標(biāo)注的信息是提供給PCB加工工廠PE的加工要求圖紙,需要遵循行業(yè)規(guī)范、保證

2017-10-25 09:03:03

布線設(shè)計(jì);2、對于各種復(fù)雜的產(chǎn)品都有著非常豐富的經(jīng)驗(yàn),能克服目前PCB設(shè)計(jì)布線中的一些缺陷,對高速數(shù)據(jù)線進(jìn)行模擬仿真,保證設(shè)計(jì)質(zhì)量;3、能針對客戶的習(xí)慣,采用不同的設(shè)計(jì)軟件完成產(chǎn)品設(shè)計(jì),如

2012-03-28 16:35:06

PCB設(shè)計(jì)對于電源電路設(shè)計(jì)來說至關(guān)重要,也是新手必要攻下的技術(shù)之一,小編在本文中就將分享關(guān)于PCB設(shè)計(jì)中的一些精髓看點(diǎn)。

2019-09-11 11:52:21

層疊設(shè)置的基本原則 單板層疊設(shè)置的一般原則如下: 元件面相鄰的第二層為地平面,提供器件屏蔽層以及為頂層布線提供參考平面。 所有信號層盡可能與地平面相鄰。以保證完整的回流通道。 盡量避免兩

2023-04-12 15:12:13

六層PCB的結(jié)構(gòu)相對四層板更加復(fù)雜,這次的案例檢測中發(fā)現(xiàn)了與以往不同的問題項(xiàng)。足以說明,對六層板的檢測需要更精準(zhǔn)更復(fù)雜的檢測機(jī)制。六層板的問題究竟出現(xiàn)在哪?讓華秋DFM帶你一起看案例。PCB設(shè)計(jì)分析軟件(華秋DFM)官方下載地址:https://dfm.elecfans.com/?from=BBS

2021-05-20 17:27:38

本帖最后由 1403545393 于 2021-5-18 17:34 編輯

四層板不同于普通PCB板,更多的層面結(jié)構(gòu)的影響,容易出現(xiàn)的設(shè)計(jì)問題也越多今天就來帶大家看看,面對四層板時華秋DFM

2021-05-18 17:30:31

給大家分享一個在快點(diǎn)PCB學(xué)院看到的一篇經(jīng)驗(yàn)總結(jié);非常不錯。 應(yīng)該是一個PCB設(shè)計(jì)高手的分享。 1、PCB板各層的含義是什么? Topoverlay ----頂層器件名稱, 也叫 top

2021-02-05 16:36:39

關(guān)系的正確性;網(wǎng)絡(luò)檢查正確通過后,對PCB設(shè)計(jì)進(jìn)行DRC檢查,并根據(jù)輸出文件結(jié)果及時對設(shè)計(jì)進(jìn)行修正,以保證PCB布線的電氣性能。最后需進(jìn)一步對PCB的機(jī)械安裝結(jié)構(gòu)進(jìn)行檢查和確認(rèn)。 第七:制版。在此之前,最好

2015-10-30 15:22:43

作者:一博科技高速先生自媒體成員 黃剛一個“xue淋淋”的案例告訴大家:正確的原理圖不一定就能產(chǎn)生正確的PCB設(shè)計(jì)。原理圖設(shè)計(jì)與PCB設(shè)計(jì)都是研發(fā)流程中的必經(jīng)階段,我們知道,原理圖設(shè)計(jì)是PCB設(shè)計(jì)

2020-12-11 09:24:41

AD在復(fù)制整塊PCB后,如何在粘貼時只粘貼某一層或某幾層?

2019-09-12 16:01:25

Designer教程零基礎(chǔ)入門 Altium Designer PCB設(shè)計(jì)速成 72講 視頻教程1、Altium Designer19入門教程最新Altium Designer19入門教程:繪制stm32四層

2019-05-16 09:48:00

電層的放置位置以及如何在這些層上分布不同的信號。這就是多層PCB 層疊結(jié)構(gòu)的選擇問題。層疊結(jié)構(gòu)是影響PCB 板EMC 性能的一個重要因素,也是抑制電磁干擾的一個重要手段。本文檔的主要內(nèi)容可以讓你了解

2018-10-17 14:02:32

Cadence 16.6 12層板高速PCB設(shè)計(jì)DDR3實(shí)例 視頻教程

2014-09-23 01:20:03

規(guī)則與PCB設(shè)計(jì)實(shí)例(史上最全PCB入門教程)最新Altium Designer19入門教程:繪制stm32四層主板PCB設(shè)計(jì)教程

2019-05-14 18:09:23

電子發(fā)燒友總結(jié)了以“PCB設(shè)計(jì)”為主題的精選干貨,今后每天一個主題為一期,希望對各位有所幫助!(點(diǎn)擊標(biāo)題即可進(jìn)入頁面下載相關(guān)資料)視頻教學(xué)資料:Altium Designer 2層新手入門實(shí)戰(zhàn)速成

2019-06-05 17:56:38

】RK3188工控主板亞軍(1名):@喊救命的超人 【PCB設(shè)計(jì)大賽】學(xué)生組(經(jīng)典六層板,建議收藏哦!同學(xué))使用的軟件:Altium Designer 20 季軍(2名):@電王之王 (Altium

2020-01-15 18:23:06

的詳細(xì)介紹可以百度搜索“華秋DFM”官方鏈接視頻背景:從新建工程到出Gerber全程錄制,Altium Designer 9.46層板PCB設(shè)計(jì) 全程實(shí)戰(zhàn)演練視頻教程,真正意義上從頭到尾錄制的一個全

2016-05-23 21:24:07

本文主要介紹多層PCB設(shè)計(jì)疊層的基礎(chǔ)知識,包括疊層結(jié)構(gòu)的排布一般原則,常用的疊層結(jié)構(gòu),疊層結(jié)構(gòu)的改善案例分析。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:06:58

:某個PCB設(shè)計(jì)項(xiàng)目經(jīng)過電路板設(shè)計(jì)師評估需要設(shè)計(jì)成6層板,但是產(chǎn)品硬件出于成本考慮、要求必須設(shè)計(jì)為4層板,那么只能犧牲掉信號屏蔽地層、從而導(dǎo)致相鄰布線層之間的信號串?dāng)_增加、信號質(zhì)量會降低。一般

2017-02-22 14:49:02

AN0029—如何在擦除或者編程過程中保證CPU重要內(nèi)容正常運(yùn)行概述有些應(yīng)用有著嚴(yán)格實(shí)時需求,需要在操作閃存擦除/編程時保證程序仍然能運(yùn)行及響應(yīng)一些關(guān)鍵信息來保證整個系統(tǒng)的正常。但是一般存儲執(zhí)行擦寫

2020-08-24 11:31:39

正確的原理圖不一定就能產(chǎn)生正確的PCB設(shè)計(jì)。

2020-12-15 06:35:55

布線設(shè)計(jì);2、對于各種復(fù)雜的產(chǎn)品都有著非常豐富的經(jīng)驗(yàn),能克服目前PCB設(shè)計(jì)布線中的一些缺陷,對高速數(shù)據(jù)線進(jìn)行模擬仿真,保證設(shè)計(jì)質(zhì)量;3、能針對客戶的習(xí)慣,采用不同的設(shè)計(jì)軟件完成產(chǎn)品設(shè)計(jì),如

2012-04-13 17:21:42

態(tài)度服務(wù)于廣大客戶。PCB工程師均有5年以上的設(shè)計(jì)經(jīng)驗(yàn),具備獨(dú)立完成項(xiàng)目能力,對PCB仿真,EMC,RF及高速信號線處理有較豐富的經(jīng)驗(yàn),熟悉PCB生產(chǎn)加工工藝和SMT 生產(chǎn)工藝流程。PCB設(shè)計(jì)能力:1層-24層設(shè)計(jì),HDI or N-HDI設(shè)計(jì);OO:41431437

2014-06-16 16:26:06

4層PCB是一種常見的多層PCB類型,具有多種用途。您是否有興趣了解更多關(guān)于它們的信息,特別是它們的堆棧設(shè)計(jì)和類型?它們的優(yōu)點(diǎn)是什么,與2層PCB相比如何?

2023-04-14 15:38:20

本帖最后由 山文豐 于 2020-6-23 15:21 編輯

濾波電容在PCB設(shè)計(jì)中的正確接法圖上是一個錯誤的濾波電容接法,電源是應(yīng)該直接從電容再到IC那里,濾波效果才會好。 下圖是正確的接法

2020-06-20 19:10:45

對疊層規(guī)劃、元器件布局、布線等所產(chǎn)生的影響做出實(shí)時分析和評估,那么版圖設(shè)計(jì)的好壞通常依賴于設(shè)計(jì)者的經(jīng)驗(yàn)。 在傳統(tǒng)的PCB設(shè)計(jì)過程中,PCB的性能只有在制作完成后才能評定。如果不能滿足性能要求,就需要

2018-11-27 15:23:52

布局和布線是PCB設(shè)計(jì)中的兩個最重要的內(nèi)容PCB設(shè)計(jì)的一般原則做四層板時,如何分割內(nèi)電層?如何畫出自己定義的非標(biāo)準(zhǔn)器件的封裝庫?

2021-04-21 06:54:29

(Layout)設(shè)計(jì)工程師,根據(jù)電氣原理圖和結(jié)構(gòu)圖運(yùn)用專業(yè)PCB設(shè)計(jì)軟件進(jìn)行布線設(shè)計(jì);2、對于各種復(fù)雜的產(chǎn)品都有著非常豐富的經(jīng)驗(yàn),能克服目前PCB設(shè)計(jì)布線中的一些缺陷,對高速數(shù)據(jù)線進(jìn)行模擬仿真,保證

2012-02-10 09:32:02

通常連接所有層。它包含4到50層導(dǎo)電材料。一種特殊類型的膠水連接多層,不同層之間使用一種特殊類型的絕緣體。絕緣體保護(hù)它們免受過多的熱量。 LED PCB設(shè)計(jì)的過程是什么? 利用計(jì)算機(jī)輔助設(shè)計(jì)軟件進(jìn)行

2023-04-17 15:07:14

錯誤。保證網(wǎng)絡(luò)表的正確性和完整性。3. 確定器件的封裝(PCB FOOTPRINT).4. 創(chuàng)建PCB板根據(jù)單板結(jié)構(gòu)圖或?qū)?yīng)的標(biāo)準(zhǔn)板框, 創(chuàng)建PCB設(shè)計(jì)文件;注意正確選定單板坐標(biāo)原點(diǎn)的位置,原點(diǎn)的設(shè)置原則

2008-07-08 19:31:09

PCB設(shè)計(jì)中層疊結(jié)構(gòu)的設(shè)計(jì)建議:1、PCB疊層方式推薦為Foil疊法2、盡可能減少PP片和CORE型號及種類在同一層疊中的使用(每層介質(zhì)不超過3張PP疊層)3、兩層之間PP介質(zhì)厚度不要超過21MIL

2017-01-16 11:40:35

板的布線層層數(shù);(3)信號質(zhì)量控制:對于高速信號比較集中的PCB設(shè)計(jì),如果重點(diǎn)關(guān)注信號質(zhì)量,那么就要求減少相鄰層布線以降低信號間串?dāng)_,這時布線層層數(shù)與參考層層數(shù)(Ground層或Power層)的比例

2017-03-01 15:29:58

哪有PCB設(shè)計(jì)視頻教程下載很全面的PCB設(shè)計(jì)視頻教程,對你肯定有用哦...PCB庫的設(shè)計(jì)視頻教程(上下冊) PCB設(shè)計(jì)進(jìn)階視頻教程(上中下冊) PCB設(shè)計(jì)深入視頻教程(上中下冊)

2009-10-26 17:35:16

PCB的成本,應(yīng)用范圍也比較廣,四層板設(shè)計(jì)流程如下。四層板pcb設(shè)計(jì)流程 1、繪制電路原理圖和生成網(wǎng)絡(luò)表 其中繪制原理圖的過程涉及到元件的繪制和封裝的繪制,掌握這兩種繪制原理圖基本不成問題了。對于錯誤

2019-03-21 10:55:49

在PCB設(shè)計(jì)中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計(jì)和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計(jì)中避免出現(xiàn)電磁問題。

2021-02-01 07:42:30

如何在PCB設(shè)計(jì)階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

我正在嘗試使用spartan 3E入門套件實(shí)現(xiàn)Web服務(wù)器。如何在內(nèi)存中保存HTML頁面?以上來自于谷歌翻譯以下為原文I am trying to implement a web server

2019-06-11 08:29:59

射頻電路PCB設(shè)計(jì)的關(guān)鍵在于如何減少輻射能力以及如何提高抗干擾能力,合理的布局與布線是設(shè)計(jì)時頻電路PCB的保證。文中所述方法有利于提高射頻電路PCB設(shè)計(jì)的可靠性,解決好電磁干擾問題,進(jìn)而達(dá)到電磁兼容的目的。

2021-04-25 06:16:26

PCB設(shè)計(jì)團(tuán)隊(duì)的組建建議是什么高性能PCB設(shè)計(jì)的硬件必備基礎(chǔ)高性能PCB設(shè)計(jì)面臨的挑戰(zhàn)和工程實(shí)現(xiàn)

2021-04-26 06:06:45

手機(jī)PCB設(shè)計(jì)中如何進(jìn)行折疊處設(shè)計(jì)-華強(qiáng)pcb 眾所周知,在整個手機(jī)PCB設(shè)計(jì)中,手機(jī)折疊處用的FPC需要非常好的柔韌性,因?yàn)樾畔a(chǎn)業(yè)部對折疊手機(jī)的翻蓋壽命要求是5萬次,而目前國內(nèi)的一線手機(jī)廠

2018-02-22 10:53:59

連續(xù),不同層的走線阻抗必須連續(xù)。規(guī)則五:高速PCB設(shè)計(jì)的布線方向規(guī)則相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射。簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直

2016-07-07 15:52:45

有沒有在海口的PCB設(shè)計(jì)工程師,有項(xiàng)目,必須要有作品,4層板以上(包括)的PCB設(shè)計(jì),是關(guān)于無人機(jī)方面的項(xiàng)目,有興趣的,請直接跟我聯(lián)系。QQ:395315244

2015-05-13 09:15:32

stm32多少層堆棧8051單片機(jī)有8層,那stm32位單片機(jī)呢?

2020-05-06 04:35:08

是否正確可靠(著重考慮與元件規(guī)格書是否保持一致,可生產(chǎn)性) 5關(guān)鍵元件的布局是否OK?(需要結(jié)構(gòu),硬件,測試,產(chǎn)品工程師確認(rèn)) 6關(guān)鍵器件間的拓?fù)浣Y(jié)構(gòu)是否合理? 7PCB疊層設(shè)置/走線規(guī)則設(shè)置/其他

2015-11-11 16:01:42

高速PCB設(shè)計(jì)的疊層問題

2009-05-16 20:51:30

的設(shè)計(jì)要求,結(jié)合筆者設(shè)計(jì)經(jīng)驗(yàn),按照PCB設(shè)計(jì)流程,對PCB設(shè)計(jì)中需要重點(diǎn)關(guān)注的設(shè)計(jì)原則進(jìn)行了歸類。詳細(xì)闡述了PCB的疊層設(shè)計(jì)、元器件布局、接地、PCB布線等高速PCB設(shè)計(jì)中需要遵循的設(shè)計(jì)原則和設(shè)計(jì)方法以及需要注意的問題等。按照筆者所述方法設(shè)計(jì)的高速復(fù)雜數(shù)模混合電路,其地噪很低,電磁兼容性很好。

2012-03-31 14:29:39

的PCB走線的時候一旦產(chǎn)生了開環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強(qiáng)度。 規(guī)則四:高速信號的特性阻抗連續(xù)規(guī)則 高速信號,在層與層之間切換的時候必須保證特性阻抗的連續(xù),否則會增加EMI的輻射

2016-01-19 22:50:31

以PCB設(shè)計(jì)軟件allegro進(jìn)行操作,以四層板的設(shè)置為例進(jìn)行正片層的光繪設(shè)置。打開allegro操作界面、在ALLGRO的操作命令:具體的生成步驟:(正片層的光繪設(shè)置、以生成TOP層為例)首先把ALLEGRO

2017-01-20 10:22:15

布線設(shè)計(jì);2、對于各種復(fù)雜的產(chǎn)品都有著非常豐富的經(jīng)驗(yàn),能克服目前PCB設(shè)計(jì)布線中的一些缺陷,對高速數(shù)據(jù)線進(jìn)行模擬仿真,保證設(shè)計(jì)質(zhì)量;3、能針對客戶的習(xí)慣,采用不同的設(shè)計(jì)軟件完成產(chǎn)品設(shè)計(jì),如

2011-05-12 09:52:50

介紹了采用Protel99SE進(jìn)行射頻電路PCB設(shè)計(jì)的設(shè)計(jì)流程,為了保證電路的性能,在進(jìn)行射頻電路PCB設(shè)計(jì)時應(yīng)考慮電磁兼容性,因而重點(diǎn)討論了元器件的布局與布線原則來達(dá)到電磁兼容的

2009-03-25 15:37:39 0

0 PCB設(shè)計(jì)基礎(chǔ)教程

此教程包括:

高速PCB設(shè)計(jì)指南之一 高速PCB設(shè)計(jì)指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB設(shè)計(jì)的一般原則 PCB設(shè)計(jì)基礎(chǔ)知識 PCB設(shè)計(jì)

2010-03-15 14:22:26 0

0 本文基于Cadence公司的PCB設(shè)計(jì)工具Concept HDL,介紹了如何在PCB原理圖中實(shí)現(xiàn)對指定功能電路單元的模糊搜索。該軟件不僅可用于未知PCB電路板或未知芯片的解析,也可用于已知原理圖

2010-08-04 15:21:53 0

0 介紹采用Protel99 SE進(jìn)行射頻電路PCB設(shè)計(jì)的流程。為保證電路性能,在進(jìn)行射頻電路PCB設(shè)計(jì)時應(yīng)考慮電磁兼

2006-04-16 22:17:22 1352

1352 RF電路PCB設(shè)計(jì)

介紹采用Protel99 SE進(jìn)行射頻電路PCB設(shè)計(jì)的流程。為保證電路性能,在進(jìn)

2009-01-18 13:16:53 984

984 PCB設(shè)計(jì)考慮EMC的接地技巧

PCB設(shè)計(jì)中,接地是抑制噪聲和防止干擾的重要措施。根據(jù)電路的不同,有不同的接地方法,只有正確

2009-11-17 09:10:49 1326

1326 PCB設(shè)計(jì)技巧大全

1.DOS版Protel軟件設(shè)計(jì)的PCB文件為何在我的電腦里調(diào)出來不是全圖?

有許多老電子工程師在剛開始用電腦繪

2010-03-09 11:42:21 1380

1380 直接進(jìn)入PCB設(shè)計(jì)系統(tǒng),在PCB設(shè)計(jì)系統(tǒng)中,可以直接取用零件封裝,人工生成網(wǎng)絡(luò)表。

2011-12-09 15:38:49 30289

30289 pcb設(shè)計(jì)邏輯芯片功能測試用于保證被測器件能夠正確完成其預(yù)期的功能。為了達(dá)到這個目的,必須先創(chuàng)建測試向量或者真值表,才能進(jìn)檢測代測器件的錯誤。

2012-06-26 15:16:39 1713

1713 PCB設(shè)計(jì)相關(guān)經(jīng)驗(yàn)分享及PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問題

2013-09-06 14:59:47 0

0 設(shè)計(jì)pcb知識 一場好用PCB設(shè)計(jì)技巧百問

2015-11-24 15:19:26 0

0 【PCB設(shè)計(jì)技巧】覆銅技巧【PCB設(shè)計(jì)技巧】覆銅技巧【PCB設(shè)計(jì)技巧】覆銅技巧

2016-02-26 16:59:59 0

0 本文介紹了濾波電容在PCB設(shè)計(jì)中正確接法。在很多PCB設(shè)計(jì)中我發(fā)現(xiàn)很多朋友的濾波電容布線有問題,所以特弄幾個圖說明下,希望對大家有幫助。 下圖是一個錯誤的濾波電容接法,電源是應(yīng)該直接從電容再到IC

2018-05-18 01:02:00 21956

21956

pcb設(shè)計(jì)

2017-04-26 16:44:49 0

0 為了保證PCB設(shè)計(jì)的準(zhǔn)確性,整個PCB設(shè)計(jì)過程中需要進(jìn)行多次檢查,接下來為大家介紹PCB設(shè)計(jì)的六個檢查階段。

2019-05-15 15:51:39 3263

3263 布線是PCB設(shè)計(jì)中非常重要的一部分,會直接影響PCB的性能。在PCB設(shè)計(jì)過程中,不同的布局工程師對PCB布局有自己的理解,但所有布局工程師都在如何提高布線效率方面保持一致,這不僅為客戶節(jié)省了項(xiàng)目開發(fā)周期,而且最大化了保證質(zhì)量和成本。下面介紹PCB設(shè)計(jì)過程和提高布線效率的步驟。

2019-08-02 09:19:37 3103

3103 為了保證線路板設(shè)計(jì)時的質(zhì)量問題,在PCB設(shè)計(jì)的時候,要注意PCB圖布線的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 從產(chǎn)品的角度看,在保證PCB設(shè)計(jì)圖電氣性能正確的前提下,還要充分考慮此設(shè)計(jì)圖對后續(xù)PCB生產(chǎn)、SMT/DIP組裝、和整機(jī)組裝測試是否有無不利的影響。所以一個好的PCB設(shè)計(jì)圖,應(yīng)該是在設(shè)計(jì)人員充分了解

2019-11-05 08:00:00 0

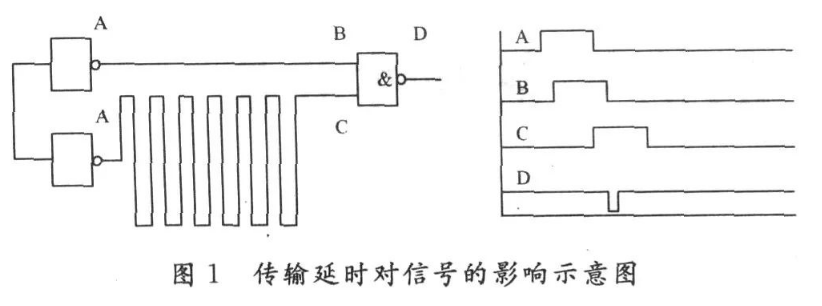

0 DDR布線在pcb設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時序,線長又是一個重要的環(huán)節(jié)。

2020-01-14 14:46:10 1188

1188 PCB設(shè)計(jì)工作完成后,需要進(jìn)行投板生產(chǎn),而在投板之前,PCB設(shè)計(jì)者必須進(jìn)行自檢,并將自檢出的問題進(jìn)行正確處理,在處理過程中有不能單獨(dú)確定的問題時應(yīng)與相關(guān)人員溝通解決。 自檢:PCB設(shè)計(jì)后期處理

2020-11-02 15:37:34 2413

2413 作者:黃剛一個“xue淋淋”的案例告訴大家:正確的原理圖不一定就能產(chǎn)生正確的PCB設(shè)計(jì)。原理圖設(shè)計(jì)與PCB設(shè)計(jì)都是研發(fā)流程中的必經(jīng)階段,我們知道,原理圖設(shè)計(jì)是PCB設(shè)計(jì)的前端流程,之前的案例也分析過一個錯誤的原理圖必然會導(dǎo)致一個錯誤的PCB設(shè)計(jì)

2020-12-24 13:22:40 2112

2112 在PCB設(shè)計(jì)中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計(jì)和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計(jì)中避免出現(xiàn)電磁問題。

2021-01-20 14:38:13 371

371 在PCB設(shè)計(jì)中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計(jì)和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計(jì)中避免出現(xiàn)電磁問題。

2021-01-22 09:54:18 20

20 電子發(fā)燒友網(wǎng)為你提供一個PCB設(shè)計(jì)中的并聯(lián)電阻正確連接資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-03 08:49:18 46

46 PCB設(shè)計(jì)是以電路原理圖為依據(jù),在PCB板上實(shí)現(xiàn)特定功能的設(shè)計(jì),PCB設(shè)計(jì)要考慮到版圖設(shè)計(jì)、外部連接布局、內(nèi)部電子元器件的優(yōu)化布局等多種因素。PCB設(shè)計(jì)的作用是規(guī)范設(shè)計(jì)作業(yè),提高生產(chǎn)效率和改善電子產(chǎn)品的質(zhì)量。

2021-07-21 11:28:55 5290

5290 @[TOC]PCB設(shè)計(jì)經(jīng)驗(yàn)(1)#PCB設(shè)計(jì)規(guī)則#PCB走線經(jīng)驗(yàn)#快捷鍵的使用#易犯錯誤匯總

2021-11-05 18:35:59 19

19 PCB設(shè)計(jì)規(guī)則你知幾何,20個PCB設(shè)計(jì)規(guī)則送給你。

2021-11-06 15:36:00 63

63 當(dāng)前,隨著PCB尺寸要求越來越小,器件密度要求越來越高,PCB設(shè)計(jì)的難度也就逐漸增大。如何在保證質(zhì)量的同時縮短設(shè)計(jì)時間?這需要工程師們有過硬的技術(shù)知識,以及掌握一些設(shè)計(jì)技巧。

2022-11-18 09:19:16 441

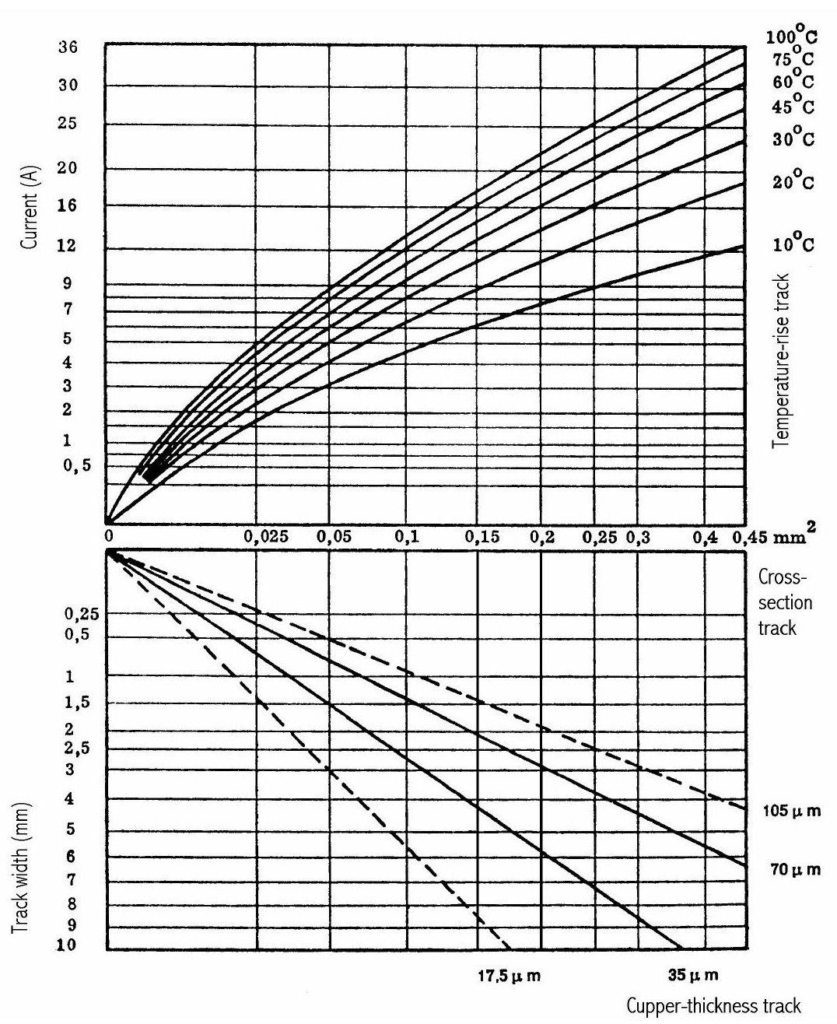

441 設(shè)計(jì) PCB 變得非常容易, 由于可用的工具負(fù)載。對于正在接觸PCB設(shè)計(jì)的初學(xué)者來說, 他可能不太關(guān)心PCB中使用的走線特性。然而,當(dāng)你爬上梯子時,注意PCB走線是非常重要的。在本文中,我們匯總了一些您應(yīng)該了解的有關(guān)PCB走線以及如何為您的PCB設(shè)計(jì)正確走線的重要事項(xiàng)。

2023-05-13 15:15:46 4492

4492

作為PCB設(shè)計(jì)的重點(diǎn),布局是布線的基礎(chǔ),一個完美的布局開端,直接使得布線工作量事半功倍。 本次就來說一下如何在真實(shí)的實(shí)操當(dāng)中規(guī)范的布局。 對于Altium Designer軟件,相比于其他軟件

2023-11-06 15:24:48 237

237

如何在層堆棧管理器中定義單層(單面)板?電路板目前有兩層,但Layer Stack Manager不允許我刪除其中一個信號層。

2023-11-10 15:19:07 330

330 PCB上信號速度高、端接元件的布局不正確或高速信號的錯誤布線都會引起信號完整性問題,從而可能使系統(tǒng)輸出不正確的數(shù)據(jù)、電路工作不正常甚至完全不工作,如何在PCB板的設(shè)計(jì)過程中充分考慮信號完整性的因素,并采取有效的控制措施,已經(jīng)成為當(dāng)今PCB設(shè)計(jì)業(yè)界中的一個熱門話題。

2024-01-11 15:28:00 87

87

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論